一种机载雷达数据记录设备设计

贾敬乐,王 啸,李 强

(南京莱斯电子设备有限公司,江苏 南京 210007)

0 引言

为了更好地对机载雷达信号处理算法进行分析、优化,需要实时记录雷达工作时的原始中频IQ数据。但受限于机载环境的严苛,要求机载电子设备具有小尺寸、轻重量、低功耗的特点[1];为此实现足够高的数据记录速度、足够大的存储容量,对记录设备的处理能力、功耗与体积都有一定要求。本文根据某型号机载雷达数据记录仪要求,记录快速的IQ数据和慢速的信号处理后的数据,设计了一款新型数据记录仪,在满足直流DC28 V供电,功耗小于70 W,重量小于3 kg以及机载工作环境适应性的前提下,实现了500 MB/s的记录速度、8 TB的存储容量的性能指标,同时该设计采用标准文件系统,能够方便数据导出,便于通用软件对数据的识别和分析。

1 设备总体设计

数据记录仪设备基于PCIE通信总线,选用NXP的POWERPC处理器作为系统的主控器;选用Xilinx FPGA实现外部所需数据的专用总线接口;存储介质选用忆芯科技的NVME SSD。FPGA与NVME SSD的PCIE接口分别与主控的PCIE连接。数据由FPGA接收后,由PCIE端口进行传输,由主控对传输的数据进行NVME SSD落盘。

因记录设备受用户结构要求,故采用模块化设计。本方案经过结构布局等综合考虑,将设备分为电源模块、主控模块、NVME存储模块、FPGA接口模块以及电子机箱。电源模块选用9 V~36 V宽输入范围的DC-DC模块,实现DC28 V输入转换DC12 V,用于主控模块、NVME存储模块、FPGA接口模块的供电。主控模块采用XMC形态,提供2路pcie3.0*4通道,分别实现与FPGA接口模块的PCIE接口和NVME存储模块接口的对接,并提供对外的千兆以太网和万兆以太网接口。NVME存储模块采用XMC模块形式,提供PCIE3.0*4接口,模块上集成2个存储控制器和一个PCIE SWITCH,每个存储控制器的磁盘容量为4 TB,总容量为8 TB。FPGA接口模块,包含2个4路一体的PLCC850 nm光模块,一个FPGA可编程器件,以及2个XMC安装位置,用于安装主控模块和NVME存储模块。

2 软件功能设计

2.1 记录流程

根据需求,选用的FPGA芯片为xilinx的690T-1761系列芯片,实现对外和对内Rapidio,PCIE接口。缓存资源采用内部BRAM即可满足数据缓存需求。

雷达的中频IQ数据由串行Rapidio接口NWRITE[2]接入事务类型。为满足数据流的持续写入NVME SSD,数据进入FPGA后经过内部多个512 KB的缓存BRAM存储,并经过SRIO时钟域到PCIE时钟域转换,每512 KB发起一次PCIE DMA[3]操作。根据数据类型带宽不同,采用4个RAM实现IQ数据的流水作业,数据处理后的数据采用2个RAM实现流水作业,IQ数据和数据处理后数据共6个RAM,采取先满先传原则,发起PCIE DMA操作。其中文件操作接收到PCIE中断信息,就会从内存中搬取数据;根据上位机的配置要求,生成符合用户需求的记录文件。生成文件的主要流程,如图1所示。由于记录仪设备本身的磁盘空间是有限的,当记录数据满了后,提供覆盖写和丢弃当前数据两种可选模式。其中记录流程,如图2所示。

图2 记录流程

2.2 回放流程

回放只针对快速的IQ数据进行回放,用于事后的重演分析。可以根据实际需求,选择需要回放的文件(支持回放一个或一组文件);主控模块读取存储模块中的文件至主控内存,并通过PCIE接口进行DMA至FPGA空间。FPGA进行PCIE时钟域到SRIO时钟域转换,每次发起DMA操作时机根据FPGA内部FIFO数据剩余数据量,保证数据流稳定。每次DMA操作512 KB,当FPGA回放数据不足32 KB时候,重新发起DMA。受限于用户信号处理能力,需控制回放速度,回放中,解析数据的帧头,计算回放节拍,将数据从光纤SRIO接口回放,回放流程如图3所示。

图3 回放流程

3 关键技术的工程实现

基于用户要求,采用的方案满足指标同时,兼顾数据维护和经济性原则。实现高带宽的记录需要软硬件协同配合,任何节点的瓶颈都影响设备的性能。

数据用户接口硬件为2路4通道的光纤接口,光模块选择6.25 Gbps速度,协议采用SRIO2.1,其最大理论通信带宽为5×4×0.8/8=2 GB/s,因用户的光纤接口处理器同样是FPGA,不存在CPU开销问题,故理论带宽基本是实际有效带宽,2 GB/s远大于500 MB/s的数据记录指标。

FPGA和NVME SSD均与PowerPC通过PCIE3.0×4相连,PCIE3.0采用128B/130B[3]编码,理论带宽为4×128/130×8/8=3.94 GB/s,远大于500 MB/s的数据记录指标。

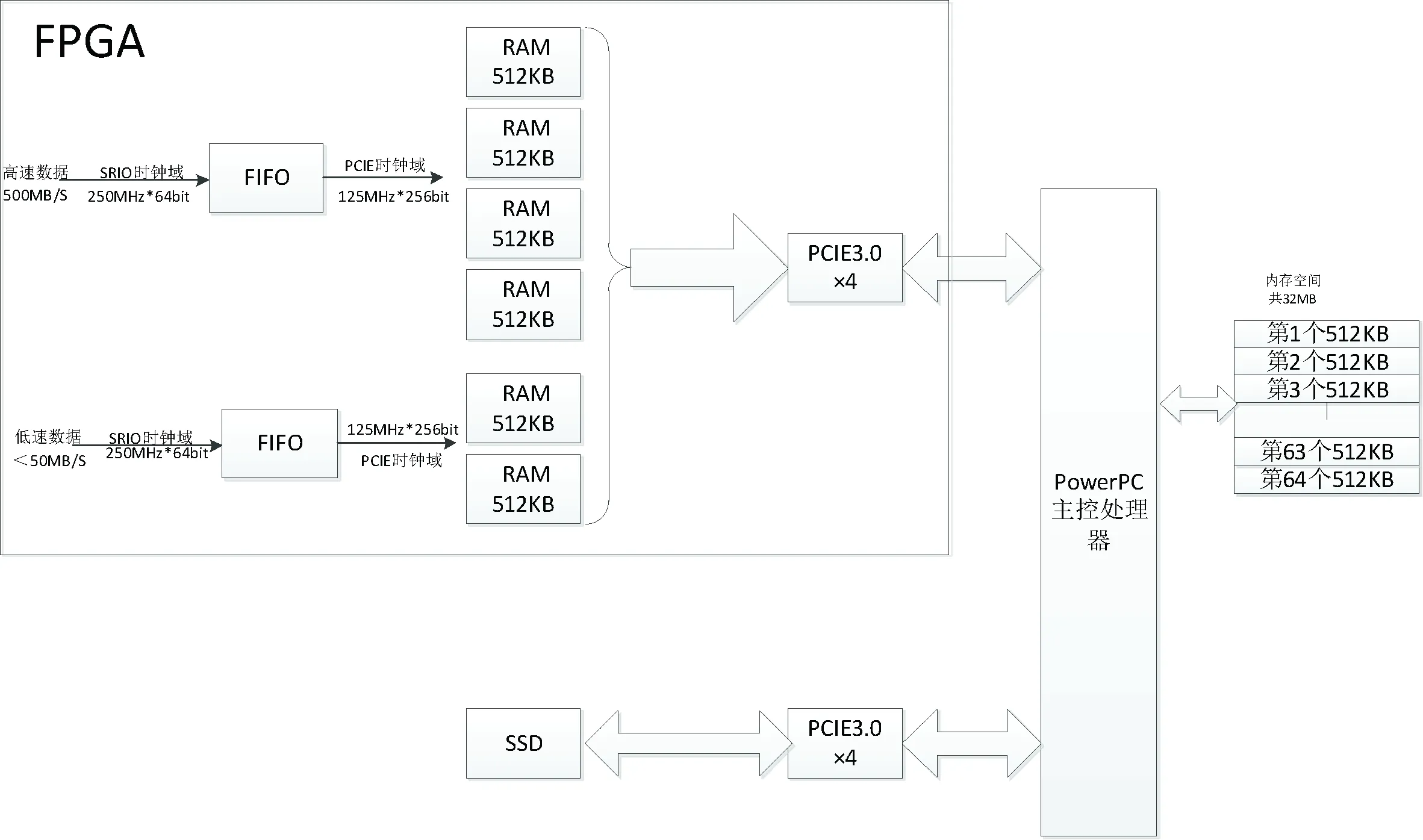

而经硬盘测试工具FIO测试,以512 KB为作为一个块单位写硬盘,单个NVME SSD盘的实际速度可达1 500 MB/s以上,即不需要对两个NVME SSD做任何特殊处理,即可满足500 MB/s的数据记录指标,数据流向,如图4所示。

从图4分析,数据从SRIO进入,经FPGA内部缓存,由PCIE端口进入PowerPC处理器。FIFO写入端时钟和数据为250 MHz×64 bit,读出端为125 MHz×256 bit,读出速度为写入速度2倍。这样数据从FPGA入口到出口,整个数据流速率是由低到高,该段数据流无瓶颈;而处理器到硬盘速度为1 500 MB/s以上,去掉实际开销,远大于500 MB/s数据率,因此整个数据记录流程满足500 MB/s数据记录指标。

图4 数据流向

数据进入FPGA后,先经FPGA内部FIFO进行时钟域和数据位宽转换,将接收到的数据从SRIO时钟域转换为PCIE时钟域,再分别通过各自的RAM缓存队列,将数据依次通过PCIE的DMA操作搬移至处理器内存空间;每搬移512 KB数据,FPGA的PCIE向处理器发送一个中断,处理器根据中断将该512 KB块数据写入硬盘;NVME SSD多队列技术特点,实现高速数据的存储处理,将处理器内存空间开辟32 MB,共64个512 KB空间,FPGA轮询向该空间中的64个512 KB块搬移数据,且处理器依次循环读取64个512 KB数据块,写入硬盘。

4 实际测试结果

实际数据传输时,因文件系统开销存在速度抖动,故在操作主控DDR3内存以及数据写入SSD时,都需要缓冲数据到一定数量时再一次写入,以提高总线传输效率。同时设备设计兼顾在整个系统中的作用,需要配合整个信号处理系统进行记录回放卸载等功能的联试联调,设备在系统中未发挥其最优性能。

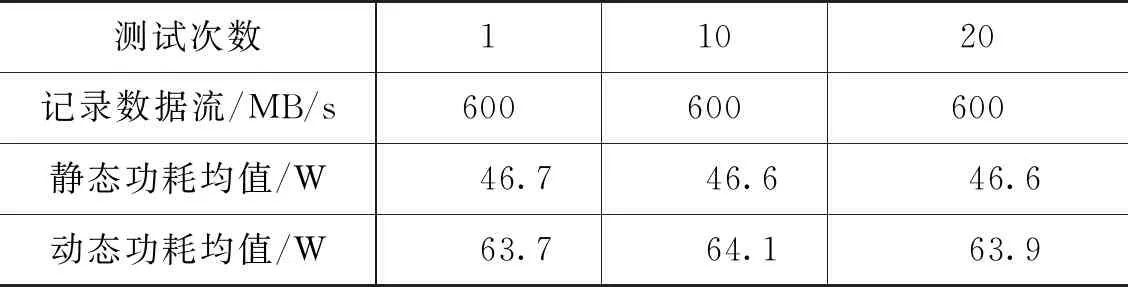

整个设备测试环境采用用户的实际环境,将设备上的主备用光纤和用户的信号处理机相连。设备的千兆口或万兆口与控制计算机相连。登录客户端软件,可对记录设备进行控制,客户端软件可实时显示磁盘容量、温度、快慢数据通道状态,SRIO链路等状态。整机满足实现600 MB/s记录速度,万兆以太网320 MB/s数据下载。整机静态功耗和工作功耗如表1所示。

表1 测试表

5 结语

本文设计的机载雷达数据记录仪满足了用户对记录速度和记录容量的要求,利用高性能高速总线接口,降低了设备功耗、尺寸重量等,同时记录的数据管理采用标准文件系统,便于数据的使用。目前完成高低温、振动、加速度、温度冲击等环境试验,并交付用户使用。