垂直短沟道二硫化钼场效应晶体管*

田金朋 王硕培 时东霞† 张广宇‡

1)(中国科学院物理研究所,北京 100190)

2)(中国科学院大学物理科学学院,北京 100190)

3)(松山湖材料实验室,东莞 523808)

基于二维材料的场效应晶体管在超大规模集成技术方面具有非常大的应用潜力,因此开发高性能的短沟道二维半导体场效应晶体管是构建超大规模集成的必经之路.对于二维材料,获得10 nm 以下沟道长度的二维半导体晶体管难度较大,目前很少有稳定制备亚10 nm 二维半导体晶体管的方法.本文使用石墨烯作为接触材料,氮化硼作为间隔,可以稳定制备垂直短沟道二硫化钼场效应晶体管.基于此方法,制备了8 nm 氮化硼间隔的垂直短沟道二硫化钼场效应晶体管.该器件展现出良好的开关特性,在不同的源漏电压下其开关比大于107;同时关态电流小于100 fA/µm,对源漏直接隧穿效应有很好的抑制作用.此外,该方法同样适用于其他二维半导体短沟道晶体管的制备,为快速筛选出可适用于超大规模集成的二维材料提供了一种有效途径.

1 引言

硅基互补型金属氧化物半导体晶体管技术已达到5 nm 以下技术节点,而由于晶体管的栅极静电调控需要大幅减小沟道厚度以保持其所需性能,使得对晶体管的进一步缩放变得越来越困难[1].随着加工技术的提高,场效应晶体管(field effect transistor,FET)的最终沟道厚度有可能在 1 nm以下,然而对于三维材料而言,当厚度降到5 nm以下时,将可能出现短沟道效应(short-channel effect,SCE),其材料本身粗糙度和界面效应导致的载流子散射将会使晶体管的迁移率严重下降[2-4].SCE 指晶体管在沟道缩短后造成的偏离长沟道晶体管特性的现象,包括接触电阻占比增大、漏致势垒降低(drain barrier lowering,DIBL)和源漏直接隧穿等.而二维(two-dimensional,2D)材料,例如以二硫化钼(MoS2)为代表的过渡金属硫族化合物,具有原子级厚度(约0.6 nm)且表面没有悬挂键,这些天然的优势可以有效免疫SCE,被认为是延续摩尔定律的备选沟道材料之一[3,5-7].

自从2011 年Radisavljevic 等[8]报道第一个二硫化钼场效应晶体管(MoS2-FET)以来,对高性能MoS2晶体管的探索就从未停止过.2016 年Desai 等[9]报道了1 nm 栅极长度MoS2晶体管,他们利用1 nm 直径金属性单壁碳纳米管作为晶体管的栅极调控双层MoS2,其结果显示MoS2对SCE 具有很强的免疫力.目前已报道制备MoS2短沟道晶体管的方法有很多,例如用石墨烯纳米缝隙作为沟道[10,11]、电子束曝光[12,13]、局部相变[14]、Bi2O3纳米缝隙[15]、纳米线作为掩膜[16-19]等.但这些方法得到的沟道长度或沟道位置随机性大、不稳定,且难以推广到其他2D 半导体或用于规模化制备短沟道晶体管.另一方面,有采用垂直晶体管加工方法制备MoS2短沟道晶体管,通常使用金作为垂直沟道晶体管的接触材料,但出现了严重的SCE,其关态电流明显增大并且开关比急剧降低[20].

我们采用石墨烯作为接触材料、以氮化硼(BN)作为间隔加工垂直短沟道MoS2-FET.该晶体管展现出良好的开关特性,在不同的源漏电压下,其开关比大于107,关态电流小于100 fA/µm,对源漏直接隧穿效应有很好的抑制作用.此外,本文制备垂直短沟道MoS2-FET 的方法可以用于稳定制备其他2D 半导体短沟道晶体管,快速筛选对SCE具有抑制作用和适合制备高性能FET 的2D 材料.

2 垂直沟道晶体管制备过程

实验上,首先在SiO2(300 nm)衬底上机械剥离两个石墨烯(石墨烯A 和石墨烯B)和薄层氮化硼(BN-A 和BN-B),再用干法转移捡起石墨烯A并转移到薄层BN-A 上形成石墨烯A/BN-A 异质结(图1(b)).接着用电子束光刻曝光和反应离子束刻蚀(reactive ion etching,RIE)光刻胶未覆盖的区域以形成边界对齐的石墨烯A/BN-A 异质结(图1(c)).接下来采用干法转移的方法把石墨烯A/BN-A 转移到石墨烯B 上,并与石墨烯B 的边界错开(图1(d)).之后用湿法转移的方法把化学气相沉积生长在蓝宝石衬底上的MoS2转移到石墨烯A/BN-A/石墨烯B 异质结上,并覆盖石墨烯A/BN-A 对齐的边界处(图1(e)).然后干法转移顶栅BN-B 到MoS2上,并覆盖石墨烯A/BN-A对齐的边界处(图1(f)).最后用电子束光刻曝光出器件的栅极和源漏电极部分,再用电子束蒸发(e-beam evaporation)沉积3/30 nm 的Ti/Au 作为接触电极(图1(g)).

3 垂直短沟道晶体管的结构测量与分析

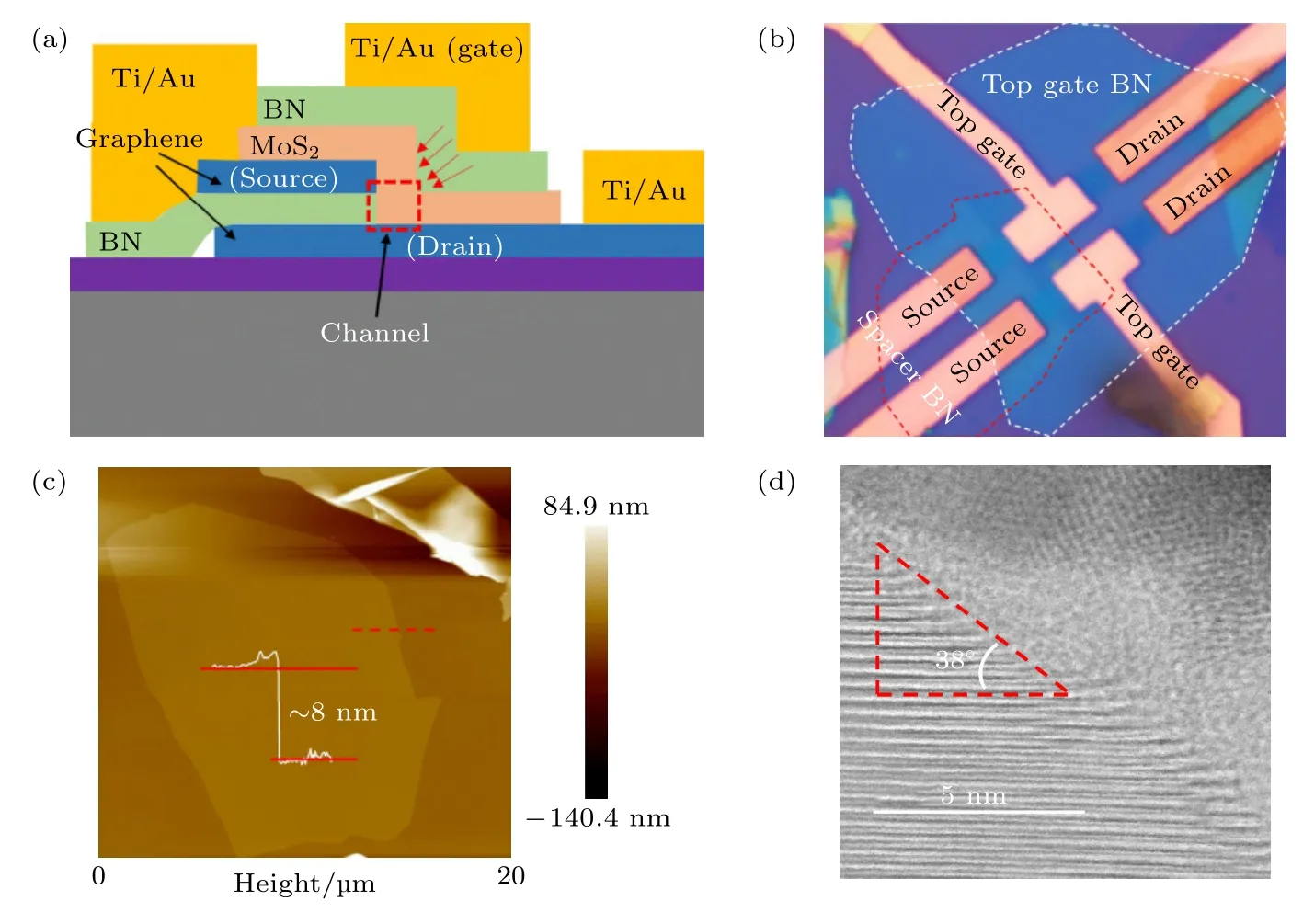

图2(a)是短沟道FET 的结构示意图,其中石墨烯A 与石墨烯B 作为FET 的源极和漏极,BN-B做为晶体管的栅介电层.石墨烯的接触金属和顶栅电极是3/30 nm Ti/Au.BN-A 隔在石墨烯A和石墨烯B 之间,使晶体管源漏不相连,而源漏中间被BN 隔开的MoS2部分(图2(a)红色虚线方框)为该晶体管的沟道区域,其长度为间隔在两个石墨烯之间BN-A 的厚度.图2(b)展示了该8 nm垂直短沟道晶体管的光学显微镜图,白色虚线方框部分为顶栅BN-B,红色方框部分为间隔BN-A.该短沟道器件的间隔BN 厚度约为8 nm(图2(c)),顶栅BN-B 介电层厚度约为 15 nm,该8 nm 沟道晶体管器件的沟道宽度W=2 µm.由于在刻蚀石墨烯A/BN-A 时会伴随着BN 的横向刻蚀,刻蚀后的BN 边界并不是严格垂直,从上到下会有一个倾角,该倾角约为38°(图2(d)),所以该短沟道晶体管的沟道长度L约为13 nm.

图2 8 nm 垂直短沟道MoS2-FET 结构(a)垂直短沟道晶体管的结构示意图,红色虚线方框部分为晶体管垂直沟道区域;(b)短沟道器件光学显微镜图;(c)间隙BN-A 的原子力显微镜测量图,间隙BN 厚度约为8 nm;(d)刻蚀后氮化硼斜面截面透射电子显微镜图,顶切角度为38°Fig.2.Structure of 8 nm vertical short-channel MoS2-FET:(a)Structure diagram of the vertical short-channel transistor,the red dotted box is the vertical channel region of the transistor;(b)optical microscope image of short-channel devices;(c)atomic force microscope image of spacer BN-A with a thickness is about 8 nm;(d)transmission electron microscope image of BN cross-section after etching,and the top-cut angle is 38°.

4 垂直短沟道晶体管电学表征

分别对8 nm 沟道MoS2晶体管的转移特性、输出特性、石墨烯与MoS2之间的接触电阻、以及是否存在DIBL 和源漏直接隧穿等进行了系列表征和分析.

4.1 垂直短沟道晶体管的转移特性

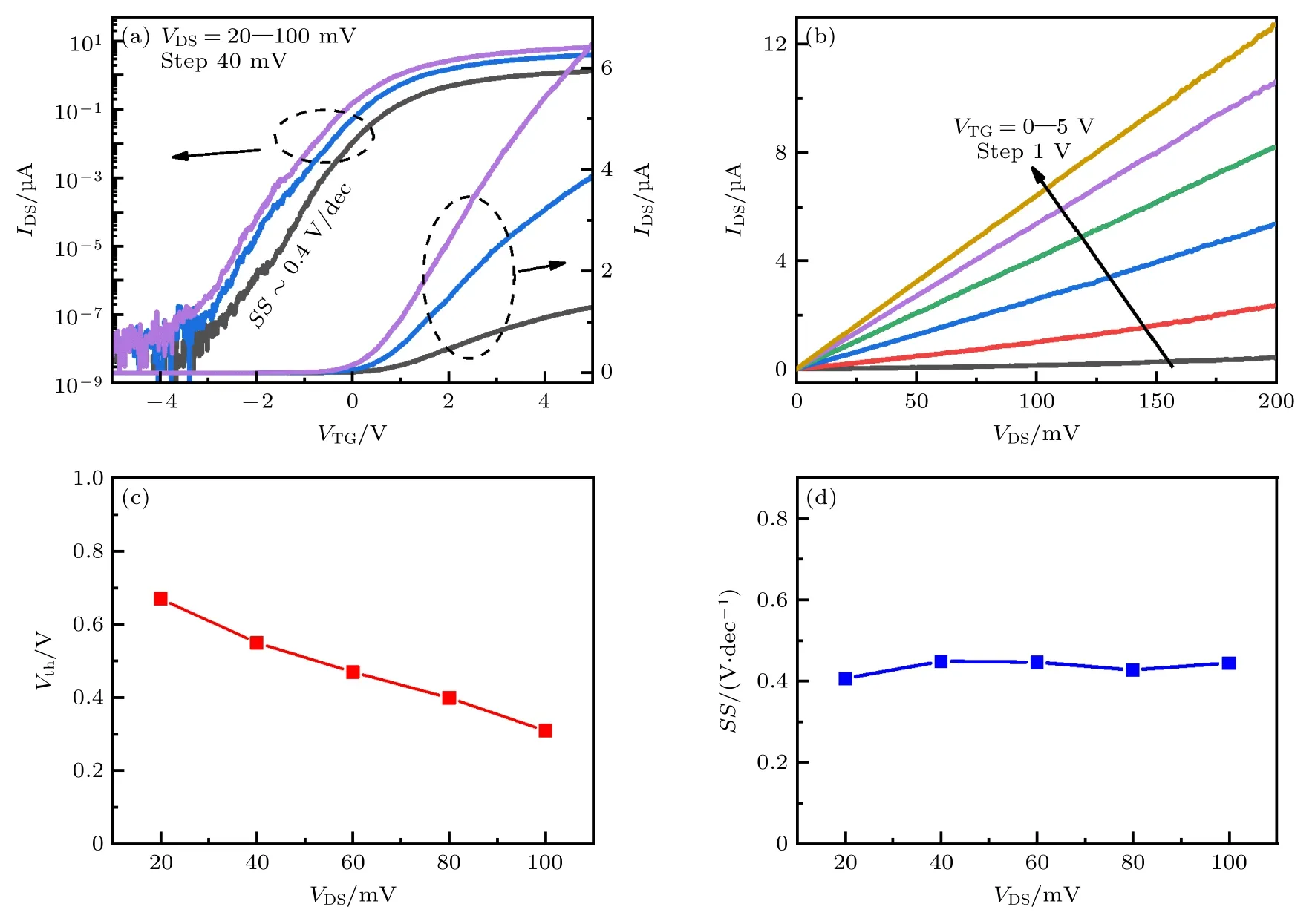

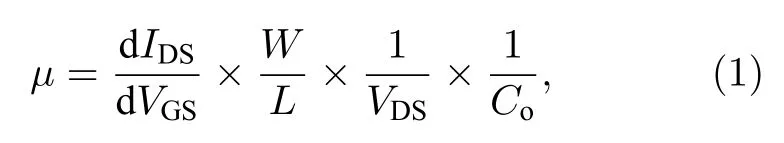

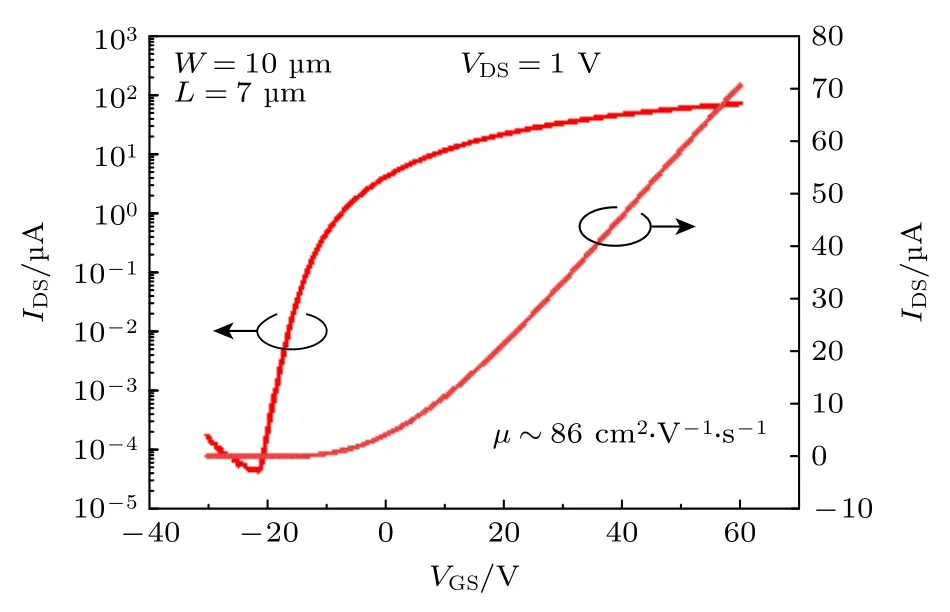

图3(a)展示了 8 nm 沟道MoS2晶体管的转移特性曲线.该短沟道器件在不同源漏电压下表现出良好的开关特性,其开关比大于107,关态电流IOFF<100 fA/µm,在VDS=0.1 V 时开态电流达到3.3 µA/µm(对应载流子浓度n约为6.4×1012cm-2).该短沟道晶体管同时展现出了良好的亚阈值特性,其亚阈值摆幅SS=dVGS/d(lgIDS)=0.4 V/dec.有效场效应迁移率表达式为

图3 8 nm 垂直沟道MoS2 晶体管电学表征(a)不同源漏电压VDS 下的转移特性曲线IDS-VGS,亚阈值摆幅(SS)约为0.4 V/dec;(b)传输特性曲线IDS-VDS;(c)晶体管阈值电压Vth 随源漏电压VDS 的变化;(d)亚阈值摆幅随源漏电压VDS 的变化Fig.3.Electrical characteristics of 8 nm vertical channel MoS2 transistor:(a)Transfer characteristic curve IDS-VGS with different VDS,subthreshold swing(SS)is about 0.4 V/dec;(b)output characteristic curve IDS-VDS;(c)threshold voltage Vth as a function of VDS;(d)subthreshold swing as a function of VDS.

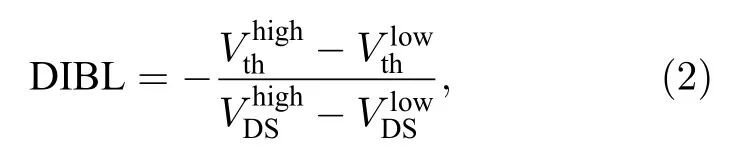

其中Co为介电层的单位电容,W和L分别为晶体管的沟道宽度和长度,计算所得有效迁移率约为0.3 cm2·V-1·s-1(VDS=0.02 V).该8 nm 晶体管计算所得有效迁移率相对长沟道器件有效迁移率(86 cm2·V-1·s-1,图4)偏低,这是由于在短沟道情况下接触电阻的占比增大[11,15].

图4 7 µm 长沟道器件转移特性曲线Fig.4.Transfer characteristics curve of the 7 µm channel length transistor.

4.2 垂直短沟道晶体管的输出特性

图3(b)展示了8 nm 晶体管的输出特性曲线IDS-VDS,可以看到在不同的栅压VGS下,源漏电流IDS随着源漏电压VDS线性增加,说明石墨烯和MoS2之间是很好的欧姆接触.通常在金属蒸镀过程中,高能的金属分子和团簇轰击MoS2表面,有可能在接触区域造成缺陷,出现费米面钉扎,导致接触电阻增加[21].与蒸镀金属不同,在该8 nm晶体管的制备中,MoS2是转移到石墨烯上,石墨烯和MoS2之间的接触是范德瓦耳斯接触,具有良好的欧姆接触,没有因金属直接在MoS2表面蒸镀造成晶格破坏而出现费米钉扎的问题.但是该器件中,由于BN 介电层的调节能力有限导致载流子浓度不高,接触电阻比较大,造成开态电流小并且迁移率较低.

4.3 垂直短沟道晶体管阈值电压随源漏电压的变化

当晶体管源漏距离缩短,源极电压的增加会直接影响源极和沟道之间接触势垒的高度和宽度,造成阈值电压随源漏电压的增加而逐渐减小,被称为DIBL,是SCE 的一种[1].图3(c)是8 nm晶体管阈值电压Vth随源漏电压的变化关系,随着源漏电压的增加,阈值电压逐渐减小.DIBL 可以表示为

4.4 垂直短沟道晶体管亚阈值摆幅随源漏电压的变化

源漏直接隧穿效应是指当晶体管沟道长度缩短到很小时,沟道中的电场强度很大、势垒变窄,这时源极和漏极之间载流子会穿过接触势垒和沟道直接发生隧穿.该隧穿电流在亚阈值区域表现为关态电流上升和亚阈值摆幅增加[22,23].图3(d)是8 nm 晶体管亚阈值摆幅随源漏电压的变化,可以看到随着源漏电压的增加,亚阈值摆幅只是轻微的有所增加,由0.4 V/dec(VDS=0.02 V)增加到0.45 V/dec(VDS=0.1 V),并且关态电流并没有明显增加.这说明该8 nm 晶体管在亚阈值区域没有出现明显的源漏直接隧穿效应,这得益于我们使用了石墨烯作为晶体管的源漏接触.和金属接触相比,石墨烯在Dirac 点附近有更快的载流子浓度的衰减,所以在亚阈值区域其电流衰减更快[24],同时抑制了隧穿电流的产生.

5 总结

用BN 作为沟道间隙,制备了石墨接触的间隙为8 nm 的垂直短沟道MoS2-FET.该晶体管展现出了良好的开关性能,VDS=0.1 V 时的开态电流达到3.3 µA/µm,而关态电流IOFF<100 fA,开关比大于107,亚阈值摆幅SS=0.4 V/dec.从输出特性曲线可以看出,该石墨接触的短沟道器件展现了良好的欧姆接触.计算DIBL为4.5,表明该短沟道器件表现出了SCE,而由于我们采用石墨烯作为接触材料,在不同源漏电压下器件的亚阈值摆幅和关态电流的变化很小,说明该短沟道器件没有源极到漏极的直接隧穿,有效抑制了源漏直接隧穿效应.此外我们制备垂直短沟道MoS2-FET 的方法同样适用于制备其他2D 半导体短沟道晶体管.该方法具有高稳定性和重复性,为2D 材料短沟道晶体管的制备提供了一种有效加工途径,同时可以快速筛选对SCE 具有抑制作用和适合制备高性能FET 的2D 材料.