一种基于压控延时链的时钟相位监测方法

王奇 孔祥松

(中国电子科技集团公司第十四研究所 江苏省南京市 210039)

随着雷达应用中探测分辨率的要求越来越高,雷达信号带宽随之增大,例如在典型的SAR成像应用中,为使分辨率达到1m,理论上信号带宽需要达到320MHz[1]。按照奈奎斯特采样定理[2],更高的信号带宽要求雷达接收机具备更高的与之匹配的采样频率。在雷达接收机中,通常使用FPGA对ADC采集的中频信号进行预处理,随着ADC采样频率的增加,数据接口时钟及数据处理时钟随之增加。在雷达接收机中,为了简化雷达工作流程,减少信号处理时间,通常需要接收机具备多通道同步能力。多通道同步能力的实现一是需要接收机信号链路上的分频时钟实现同步,二是需要实现外部定时信号的稳定采集,本质上二者都需要实现跨时钟域的稳定同步,即信号在跨时钟域同步时满足建立-保持时间要求。时钟频率的增加使得跨时钟域同步过程中的建立-保持时间裕量减小,为实现稳定的跨时钟域同步,需要对两个时钟的相对相位进行监测。

在FPGA中,通常采用多相时钟的方法对时钟间的相对相位进行检测。该方法通常由时钟管理器(例如Xilinx FPGA中的MMCM)产生同频率但有固定相位差的多个时钟对目标时钟同时进行采集,根据采集到的寄存器值确定时钟间的相对相位。该检测方法检测时间短,但需要消耗宝贵的全局时钟资源(时钟管理器、BUFG等),同时受限于可产生的多相时钟个数,该相位监测方法的精度通常较低。针对多相时钟鉴相方法的不足,本论文提供了一种基于多抽头压控延时链的时钟相位监测方法,该方法利用FPGA中丰富的压控延时链对时钟实现可控延时,利用延时后的时钟对被监测时钟进行采集即可实现时钟间的相位监测。在2.5ns的监测范围内,本论文提出的方法可实现78.125ps精度的相位监测,同时仅需要少量的寄存器、查找表等通用逻辑资源。

1 相位监测原理

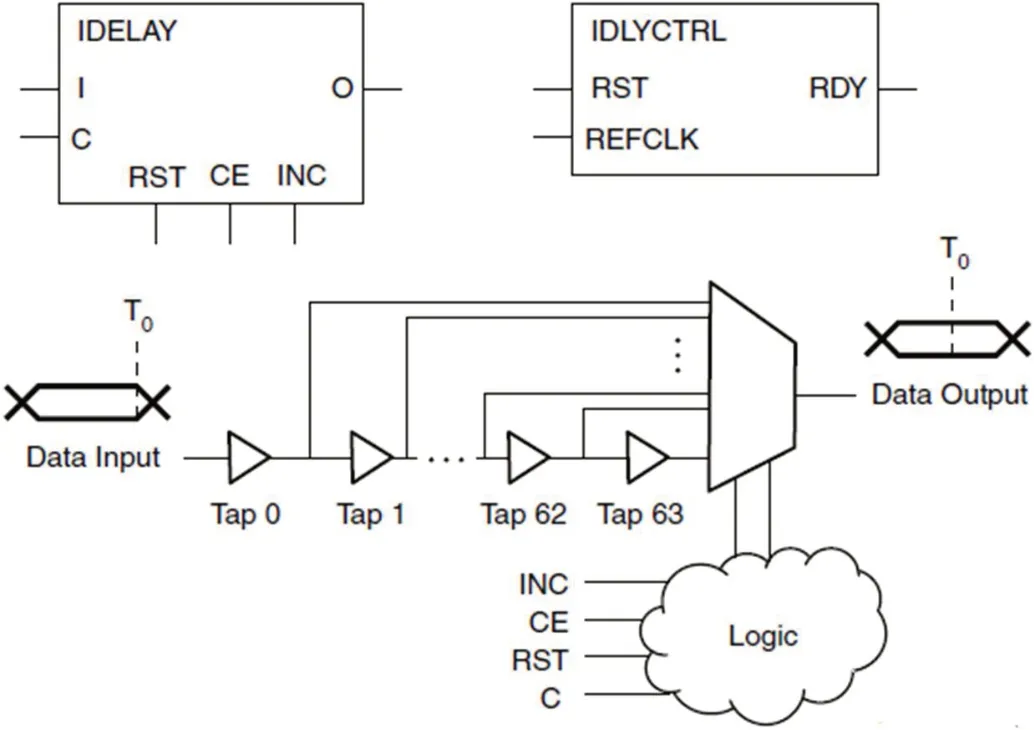

在Xilinx 7系列FPGA中,每个I/O块均包含一个名为IDELAYE2[3]的可编程延时单元,该延时单元可对I/O端口输入的时钟、数据或者来自内部逻辑的信号进行可编程延时。如图 1所示,IDELAYE2是一个包含64个延时单元、具有64个抽头的压控延时链,64个抽头引出的信号通过一个高性能多路选择器实现可编程延时输出。该压控延时链由校准模块IDELAYCTRLE2以输入参考时钟为基准进行校准,整条延时链的总延时时间等于1个参考时钟周期,因此校准完成后单元延时精度为

图1:压控延时链原理简图

ttap=Trefclk/64

参考时钟通常为200MHz,则此时延时链的理论延时精度为78.125ps。由于IDELAYE2为压控反馈延时链,因此对温度、电压等波动具有良好的稳定性。

由于寄生电容的存在,将延时链插入信号路径会不可避免的恶化信号质量。如图 2所示,在600Mbps的速率下对时钟和数据经延时链后的眼图进行测试,测试所用数据码型为PRBS23.测试结果表明随着延时链的增长,IDELAYE2对数据信号的恶化较为明显,根据Xilinx的测试结果[4],在高性能模式下单个延时单元会对数据信号增加约5ps的抖动。与此形成鲜明对比的是,时钟信号几乎可以无失真地通过延时链,这是由于时钟信号占空比为50%,具有理想的平衡特性,码间干扰较小。因此利用压控延时链进行时钟相位监测不会对时钟质量造成明显恶化。为了保证延时后的信号质量,Xilinx提供的IDELAYE2原语仅提供了延时链前32个延时单元的控制接口,因而延时链的最大延时范围为1/2Trefclk。

图2:不同延时值对时钟及数据的影响对比

时钟相位监测的原理如图 3所示,将主监测时钟CLK1经压控延时链延时后输出至D触发器时钟输入端,将被监测时钟CLK2直接输出至D触发器的数据输入端,延时控制逻辑对压控延时链实施控制,实现CLK1的相位调整,判断逻辑根据D触发器采集到的数据记录扫描的位置,通过调整压控延时链的延时值即可精确移动CLK1的相位,实现对CLK2的扫描采集。

图3:相位监测原理示意图

2 相位监测设计实现

本论文中利用压控延时链对100MHz时钟进行延时调整,以调整后的100MHz时钟采集400MHz时钟实现二者相对相位的监测。在FPGA中实现的基于压控延时链的时钟相位监测程序原理框图如图 4所示,由校准模块、压控延时链、延时控制模块、采样寄存器以及输出编码模块组成。其中校准模块直接例化IDELAYCTRLE2原语实现,在本论文的实现中参考时钟频率为200MHz,因此压控延时链的延时步进为78.125ps,最大延时范围为2.5ns。压控延时链直接例化IDELAYE2原语实现,延时输入来源设置为内部逻辑输入,信号类型设置为时钟,延时类型需设置为可编程类型,即可通过控制接口动态调整延时值。

图4:相位监测原理框图

延时控制模块由一个状态机实现对压控延时链的控制。状态机的状态转移图如图 5所示,状态机在IDLE状态等待启动信号,当启动信号为1时进入SET状态,状态机在SET状态对压控延时链的延时值进行设置,然后进入等待状态,等待一定时间后状态机进入MEASURE状态,等待监测完成信号。当监测完成信号为1,并且当前延时值为31时表示所有延时值已遍历,状态机进入IDLE状态。如果监测信号为1但当前延时值小于31则进入SET状态设置下一个延时值。

图5:控制状态机状态转移图

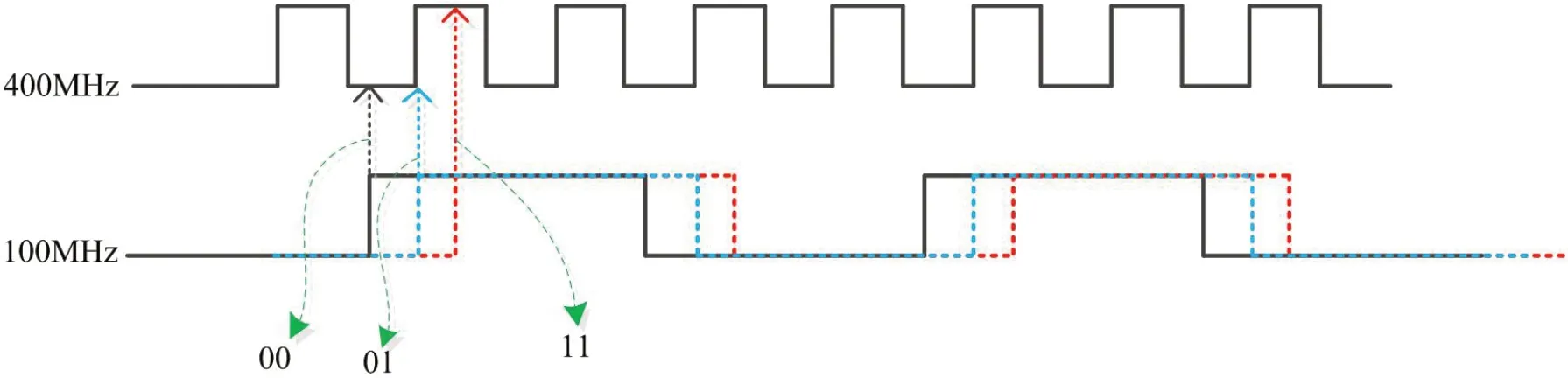

如图6所示,输出编码模块根据采样寄存器采集的结果进行编码,监测完成后输出特定编码格式的监测结果。在状态机的MEASURE状态,输出编码模块对采样寄存器的输出值进行计数,采样寄存器在每个延时值对被监测时钟采样N次,输出编码模块对采集到的结果进行累加。采样结束后如果累加和为0,则表示在该延时值下监测时钟上升沿采样到被监测时钟低电平位置,该延时值的测试结果编码为二进制00;累加和大于0且小于N,则表示两个时钟沿碰沿,该延时值的测试结果编码为二进制01;累加和为N则表示在该延时值下监测时钟上升沿采样到被监测时钟高电平位置,该延时值的测试结果编码为二进制11。所有延时值测试完成后,32个延时值的测试结果按顺序合并为64位监测结果进行输出。

图6:输出编码示意图

上述设计在型号为XC7K325T-1FFG900I的FPGA上进行了实现,实现后的资源消耗统计如图 7所示,该实现结果表明基于压控延时链的相位监测方法仅需要极少量的通用逻辑资源即可实现,其中锁存器使用344个,约占总资源量的0.084%;使用查找表169个,约在总资源量的0.083%;I/O块使用两个,占比0.4%。

图7:FPGA逻辑资源消耗统计

3 测试结果

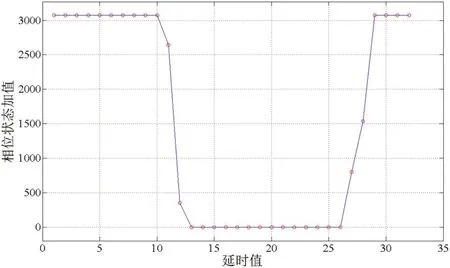

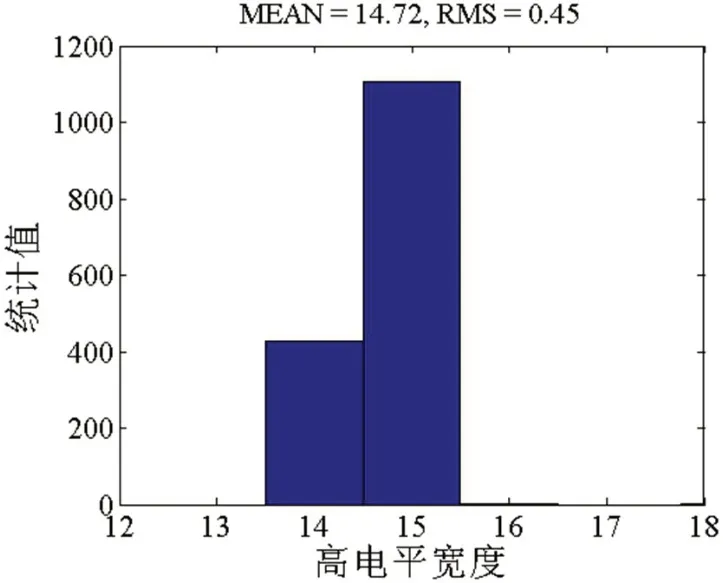

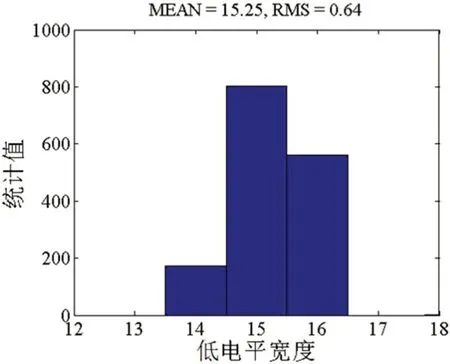

为验证上述方法的功能和性能,本论文搭建测试平台进行了测试。测试连接由频标组件产生100MHz及400MHz时钟输出至FPGA,其中400MHz时钟为被监测时钟。在FPGA中采用混合时钟管理器(MMCM)产生200MHz参考时钟及100MHz监测时钟。相位监测模块输出的监测结果通过JTAG接口上传至计算机进行分析。将测试采集到的约1500个波形进行重建分析,设置高电平的权值为2,亚稳态的权值为1,低电平的权值为0,对波形进行累加重建,重建后的波形如图 8所示,测试数据很好地重建了400MHz时钟的波形。对所测得的时钟波形的高低电平宽度进行统计,统计结果如图 9及图 10所示,测试结果表明,时钟波形中高电平宽度约为14.72个延时节拍,即1150ps;时钟波形中低电平宽度约为15.25个延时节拍,即1191.4ps。

图8:400MHz时钟波形重建结果

图9:400MHz时钟高电平宽度测试结果

图10:400MHz时钟低电宽度平测试结果

4 结论

本论文采用了FPGA中的压控延时链,设计了一种低资源消耗、高精度的时钟相位监测方法。该方法在各逻辑资源消耗量小于0.4%的情况下,实现了精度为78.125ps的时钟相位监测,可以广泛运用于具有多时钟同步要求雷达接收系统中。