Xilinx FPGA 高速信号数据处理系统研究与设计

蒲宝卿,高庆芳,撒志敏

(陇南师范高等专科学校 数信学院,甘肃 陇南 742500)

随着电子通讯和雷达对抗等技术的快速发展,传统信号处理系统中的数据采集、数据分析与处理、数据检测和数据存储技术已经不能满足现阶段各个领域中的需求[1]。FPGA数据信号处理系统面对数据海量增涨化、数据传输高速传输化、数据采集高可靠化和数据文件管理便捷化等需求,仍有下述问题需要解决[2]。

(1)当信号处理系统中的数据采集频率高速变化时,如何实现高速数据信号的快速迁移;

(2)数据信号的高速迁移,如何设计高速数据信号存储方案;

(3)当数据信号采集储存后,如何实现便捷的数据文件的管理。

为了解决上述问题,设计了Xilinx FPGA XCZU9EG高速信号数据处理系统。该系统的核心由PS(Processing System)和PL(Programmable Logic)组成[3]。PS控制功能主要实现采集系统的数据控制处理、信号数据分析和信号数据检索等功能。PL数据接口主要是提供Aurora X8的高速数据传输接口,为系统提供数据通道。系统硬件设计主要包括了数据采集、数据迁移和数据存储硬件电路设计。

软件功能主要实现了GTX(Gigabit Transceiver)数据交换、AXI-DMA(Advanced eXtensible Interface-Direct Memory Access)底层驱动和数据迁移命令交互,从而实现数据的DDR4(Double Data Rate 4)迁移存储等。

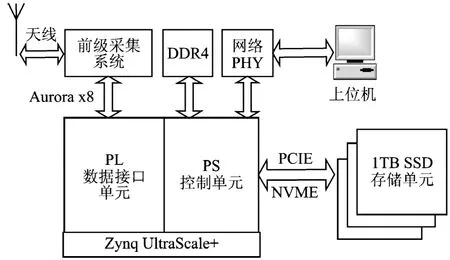

1 数据处理系统总体框架设计

数据处理系统方案的核心采用了多重处理架构Xilinx FPGA XCZU9EG平台,该平台的PS(Processing System)控制单元模块主要由ARM Cortex-M53和ARM Cortex-R5组成,PL(Programmable Logic)模块主要由24个高速串行收发器提供了数据接口单元[4]。数据处理系统总体框架如图1所示。

图1 数据处理系统总体设计

前级数据采集模块主要实现数据的快速采集、快速处理和快速转发功能。DDR4模块中的内存数据迁移功能主要由数据采集系统PS AXI IP(Intellectual Property)内核来实现。1 TB SSD(Solid State Drives)存储单元采用了PCIE和NVME协议实现数据的上传与下载存储。上位机的主要功能是通过HeEdit 软件实现数据采集处理系统的数据交互。

2 数据信号处理系统硬件设计

2.1 数据信号采集硬件系统电路设计

高频数据信号采集系统主要包括了XC7K325T模块、ADC12J2700模块和高频正弦信号处理功能模块。

(1)XC7K325T:通过clock按照固定频率完成A/D数据信号采集和FIFO数据储存, 具备24路GTX多通道,可以同时实现多路信号传输功能。

(2)ADC12J2700:主要完成数据信号的频谱采样、信号滤波、信号变频和信号调谐等。

(3)高频正弦信号(High frequency signal)经过信号调制电路(signal modulate circuit)转换成差分信号,同时通过差分clock控制ADC12J2700的采样频率,实现多路信号的转换采集和传输功能[5]。数据信号采集硬件系统如图2所示。

图2 数据信号采集硬件系统

2.2 高频信号迁移硬件系统设计

高频信号采集完毕后,XC7K325T提供的高速接口首先完成FIFO的信号转存功能,然后通过PL单元的AXI IP内核和PS单元的PCIE X4内核完成硬件底层驱动和GT Lane接口对接,及时通过Aurora x8接口将高速数据资源(High speed data source)迁移至DDR4内存模块中[6]。高频信号迁移硬件电路系统设计如图3所示。

图3 高频信号迁移硬件电路系统

AXI-DMA主要通过AXI-LITE processor端口来完成PS内核配置,AXI-stream端口主要实现PL模块的数据信号交互功能。AXI-DMA的数据信号处理模式为直接寄存器储存模式。

AXI-DMA外部信号迁移路径为:AXI Data FIFO→S_AXIS_S2MM→ AXI-DMA→M_AXI_S2MM→DDR4。

AXI-DMA内部信号迁移路径为:内存DDR4→DDR MC→M_AXI_MM2S→AXI-DMA→ M_AXI_MM2S→Data FIFO。

2.3 高频信号存储硬件系统设计

高频信号存储硬件采用的是支持PCIE X4 Gen2.0接口的SSD存储控制器,数据交换协议采用NVME(N-Volatile Memory express ME)协议。该存储控制器的型号为STAR1000,主要包括了LDPC、多核CPU、RAID、片上SRAM和控制逻辑单元。它可以实现流水线模式的Flash编程,大大提升了数据存储的速度[7]。高频信号存储器STAR1000电路设计如图4所示。

图4 高频信号存储硬件系统

3 系统软件设计

3.1 高频数据采集和数据迁移软件流程设计

IP内核开启AXI-DMA的硬件驱动程序装载、AXI-DMA硬件地址的应用层匹配和AXI-DMA数据采集通道的初始化工作,然后启动左右线程1和线程2。

线程1主要能够实现数据信号的采集和数据迁移功能,当FLAG=1时,打开Aurora接口通道,REQ=1和FLAG=0时,关闭Aurora接口通道同时REQ复位归0,数据源请求标志REQ=1后,启动Aurora接口通道开始数据迁移工作,并采用PCIE/NVME协议进行数据存储。

线程2的功能主要实现TCP/IP通信协议的启动和实时解析网络数据包,千兆网络保障通信信道的畅通功能[8]。高频数据采集和迁移软件流程如图5所示。

图5 高频数据迁移与存储设计

3.2 高速FIFO 芯片FLASH存储流程设计

高速FIFO 芯片的FLASH 的存储模式采用“交叉写”模式,资源通道Source_divided_A进行FLASH_1数据存储时,按照每1 KB编帧和每1 KB划分开,Fifo_inselect 选择FIFO_1 与FIFO_3的数据进入后面的16 KB 标准FIFO,完成FIFO存入(pro_empty=8KB),最后实现数据存入FLASH_1[9]。同理可得,Source_divided_B通道FLASH_2数据存储交叉方式,交叉模式可以提高FLASH存储速度。FIFO 芯片的FLASH存储流程设计如图6所示。

图6 高速FIFO 芯片FLASH存储流程设计

4 系统搭建与测试

针对高速信号数据处理系统进行了环境搭建和系统测试。数据信号经过采集与处理后,进行了数据信号的回读并将回读结果通过HeEdit 软件进行了展示,单行数据的字节数为1 024。其中每帧数据中,RS485接口有效帧标识为“Fx和Ex”。Ge端口的有效帧标识为“FAF6”,图像帧标识为“DC 92”,PCM行标识为“EB 90”。本文的部分测试数据0000270H-0000300H结果如图7(a)所示,0000698H-0000708H结果如图7(b)所示。

从图7(a)和图7(b)可以看出在系统测试中,高速信号数据处理系统采集的测试数据整齐有序及格式完整,数据规则符合采集系统需求。帧数据误码率低、数据可读性高、存储速率快。经过多次测试,各类帧数据标识几乎没有错误,误码率接近为0,处理速度快,系统符合设计初衷。

5 结语

基于Xilinx FPGA XCZU9EG高速信号数据处理系统主要包括整体框架设计、硬件系统设计和软件系统设计三部分。核心平台的PS单元模块主要完成了数据处理功能,PL模块主要为系统提供数据通道。数据信号处理系统硬件系统主要完成了采集、迁移和存储电路设计,系统软件设计主要包括了高频数据采集、高频数据迁移和FIFO数据信号存储等。测试结果表明,该高速信号数据处理系统具有数据排列整齐有序、误码率低、存储速度快、检索便捷等优点,具备较强的推广性。