基于Verilog HDL的一种CPLD测试模块设计

杨鲲,杨彬彬,曾垒,高灿辉,刘姚军

(国营芜湖机械厂,安徽 芜湖 241007)

Verilog HDL(Verilog Handware Description Language,即Verilog硬件描述语言)能够形式化地抽象表示电路的行为和结构,具有强大的硬件描述功能。它允许设计者用其来进行各种级别的逻辑设计,以及数字逻辑系统的仿真验证、时序分析和逻辑综合,由于其标准规范且易于掌握,已经成为目前应用最为广泛的硬件描述语言之一。因此,采用Verilog HDL对CPLD进行硬件编程就可以方便、稳定、精确地实现对CPLD的功能测试。CPLD(Complex Programmable Logic Device,即复杂可编程逻辑器件)是20世纪80年代中期发展起来的一种新型逻辑器件,是目前数字系统设计的主要硬件之一,它可以在制造完成后由用户根据自己的需要定义其逻辑功能。它具有编程灵活、集成度高、设计开发周期短、适用范围宽、开发工具普及、运算速度快、易于扩展和移植、性价比高等特点,可实现较大规模的电路设计,因此被广泛应用于产品的原型设计和产品生产中。CPLD器件已成为电子产品中不可缺少的组成部分,它的设计和应用成为电子工程师必备的一种技能。

1 测试模块设计

1.1 ispLSI1032的基本结构

ispLSI系列器件是由Lattice公司生产的基于与或阵列结构的复杂PLD产品。芯片由若干个模块组成,模块之间通过全局布线区GRF连起来,每个模块包括若干个通用逻辑块GLB、输出布线区ORP、若干个I/O引脚和专用输入引脚。ispLSI1032芯片具有192个寄存器、64个通用I/O管脚、8个专用输入管脚、4个专用时钟输入管脚和一个全局布线区,最高频率60MHz,最快延迟时间20ns。其功能框图和引脚图如图1所示。

图1 ispLSI1032功能框图和引脚图

1.2 测试模块设计

由于是对芯片进行功能测试,所以将ispLSI1032作为处理芯片,搭载外围相应测试电路即可。为了方便测试,需同时提供两片芯片的接口,并将所有的I/O口做输入输出测试,且两片芯片测试不受影响。整理出硬件需求如下:

(1)供电电源接口:外接+5V电源供电,提供电源和地输入。

(2)ISP接口:用于对芯片进行程序下载,使用跳线座区分两片芯片的下载需求。

(3)I/O测试接口:将I/O口引出,便于外接示波器进行波形观察。

(4)功能控制开关:选择波形测试或者电平测试功能。

(5)电平控制开关:在电平测试模式下,设置端口输出高或低电平。

软件需求如下:

(1)波形测试功能:对板载晶振提供的时钟信号进行分频处理,在相应端口输出固定频率的方波,并用示波器进行检测。

(2)电平测试功能:在输出端口直接输出高/低电平,通过发光LED直观观察。

(3)编号UA芯片测试接口功能为单数I/O口为信号输入端口,双数I/O口为信号输出端口。

(4)编号UB芯片测试接口功能为单数I/O口为信号输出端口,双数I/O口为信号输入端口。

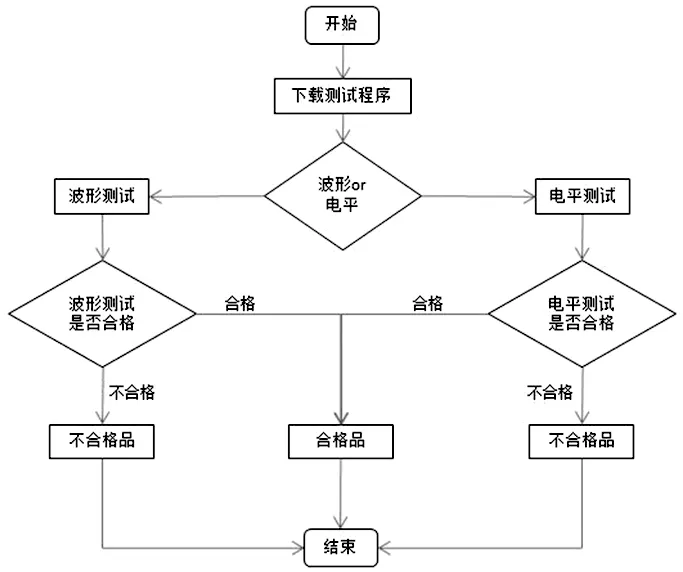

单次芯片测试流程图如图2所示,在UA处测完后,重新烧写程序,输入输出端口定义对调,在UB处重复检测过程。

图2 测试流程图

Lattice ispLSI1032芯片测试原理如图3所示。X2为供电电源接口,输入电压+5VDC;X1为芯片下载接口,使用跳线座短接X101、X102区分两片芯片的下载需求;单刀双掷开关S1作为功能控制开关,控制波形与电平测试,S3为电平测试的输入电平选择开关;I/OA1-B4为测试孔,方便进行波形测试,发光二极管则是观察电平测试。

2 测试芯片源代码

ispLSI1032芯片的Verilog HDL语言程序描述如下。模块ispLSI1032_test 用来产生多路输出信号,其中输入时钟clk频率为8MHz,fun_switcher为功能选择开关,当为高电平时,选择波形测试,当输入为低电平时,选择电平测试;cnt为分频变量,用于将输入时钟进行10分频;为了方便测试,将32个输出I/O口分为4组,并将分频后的结果赋予到每组I/O口上,然后即可通过示波器进行测试。

module ispLSI 1032_test (clk,fun_switcher,ioctl,out);

input clk.fun_switcher;

input [31:0] ioctl;

output [31:0] out;

reg [31:0] out;

reg [9:0] cnt;

reg [7:0] reg8;

reg clkadd;

always @(posedge clk)

begin

if (cnt==10)

begin

cnt<=10’d0;

cntadd++;

end

else

begin

cnt<=cnt+1;

out<=out;

end

end

always @(posedge clkadd)

begin

if (fun_switcher)

begin

out<=ioctl;

end

else

begin

reg8++;

out[7:0]<=reg8;

out[15:8]<=reg8;

out[23:16]<=reg8;

out[31:24]<=reg8;

end

end

endmodule

3 结语

Lattice ispLSI1032芯片的测试方法已在实际工作中得到应用,芯片测试速度、效率及精确度均满足要求,工作稳定可靠。本文在分析了ispLSI1032的内部结构及测试原理和需求的基础上,利用硬件描述语言Verilog HDL进行设计,对芯片做功能测试,进行筛选。该方法开发成本低,设计周期短,操作易上手,修改逻辑方便,能够极大地降低人力成本,是一种快捷有效的测试方法。