浅谈一种基于AD9910的L波段频率合成器

许晨煜

(国营芜湖机械厂,安徽 芜湖 241007)

当前通信领域向大带宽、高准确度、高速率低延时的方向迅猛发展,通信系统内各部件的指标要求也逐渐提高。L波段是航空航天通信过程中常用波段,主要用于卫星通信、导航识别、询问应答等系统,对于信息的准确率、时效性、保密性有很高的要求。频率合成器作为通信技术的基石,其性能直接决定通信质量。DDS直接数字频率合成技术在近年出现并在工程应用方面实现突飞猛进的发展,本文采用AD9910实现了一种具有较高性能的L波段频率合成器的设计。

1 DDS技术介绍

频率合成(Frequency Synthesizer)是指一个或多个具有高频率稳定度和高精确度的参考信号源,通过频域的线性运算等信号处理技术,产生具有同样稳定度和准确度的大量离散频率的过程。频率合成器的主要性能指标包括:频率范围(带宽);频率分辨率;频率准确度;转换时间;杂散等。随着电子技术的发展,频率合成技术已由直接模拟频率合成技术、间接频率合成技术发展至第三代直接数字频率合成即DDS技术。

DDS频率合成器由D/A转换器(DAC)、相位累加器(PD)、波形存储器(ROM)、低通滤波器(LPF)等主要部件组成,其工作原理为查找表示的。工作流程为:在每个周期内根据提供的正弦函数,对基准信号进行采样,得出不同时刻的相位幅度频率值,将该三类物理量转换为电压大小代表的数字量,该数字量进行D/A转换并将滤波后输出平滑正弦波。相对于前两代传统的频率合成器,DDS除了能够方便地产生方波、三角波、锯齿波等任意波形外,还具有频率分辨率高、相位连续且频率转换时间短、易于控制等优点。由于D/A转换器性能所限以及相位取整等算法的固有因素限制,DDS也存在一些缺点如杂散抑制差、工作频带受限,但一般使用条件下其关键性能指标不受限制。

2 方案设计

2.1 AD9910功能介绍

AD9910是ADI公 司 推 出 的 一 款3.3V CMOS直 接数字频率合成器,采样速率高达1GSPS,频率分辨率0.23Hz。其内部集成了14位DAC,可输出400MHz频率以内的模拟信号。图1为架构图,图2为功能块详细介绍。与普通DDS芯片相同,AD9910采用波形存储器+相位累加器+D/A转换器的通用设计,DDS核心的控制信号为幅度频率相位三类。它有4种工作模式:单频模式、RAM调制模式、线性斜坡调制模式、并行数据端口调制模式。单频模式下DDS控制信号仅直接来自于图2中所示可编程寄存器,RAM调制模式下信号仅来自RAM,线性斜坡调制模式下控制数据来自数字斜坡发生器,并行数据端口调制模式下控制数据来自高速并口。

图1 AD9910架构

图2 AD9910功能块详解

2.2 方案设计

2.2.1 控制模块设计

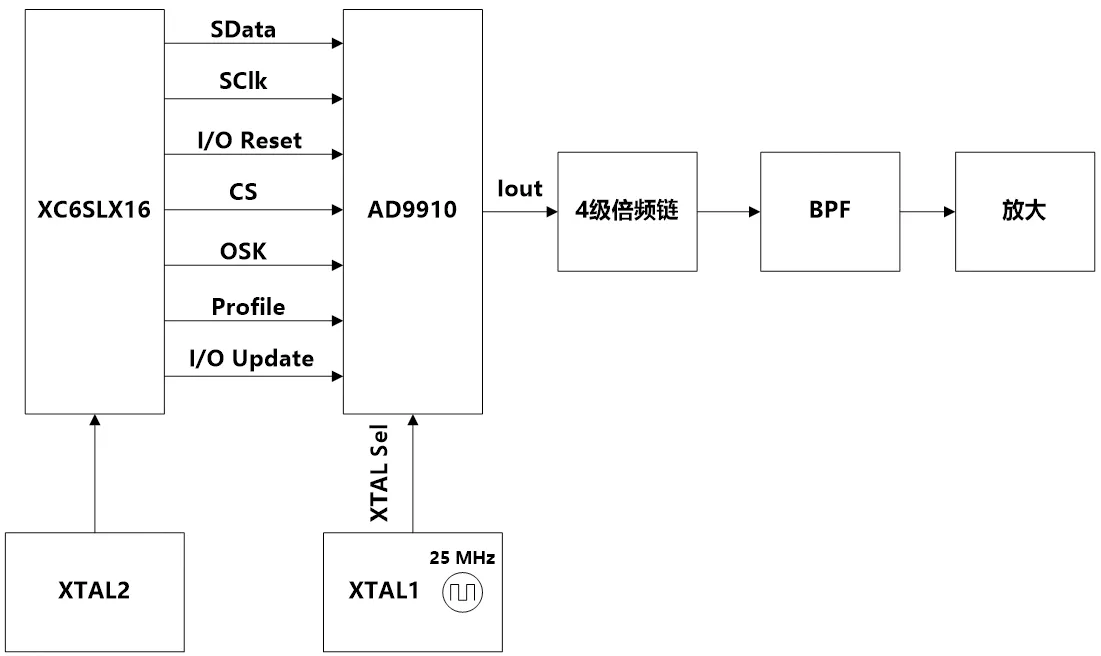

本方案采用FPGA+DDS+倍频链的频率合成器架构,如图3所示。

由于设计目的是为了检测某产品定频工作状态下的性能,必要时进行可选的步进1MHz信号输出,频率步进时间0.5s,远未达到AD9910性能上限,因此无需考虑使用并口快速跳频功能,采用单频工作模式即可。控制端以Xilinx公司现场可编程逻辑门阵列芯片XC6SLX16作为控制器,以串行码作为频率控制字控制AD9910输出,并以一定周期切换串行码使频率在规定时间内步进。XC6SLX16是Xilinx公司工业级FPGA芯片,具有丰富的逻辑资源,I/O口数据传输速率高达800Mb/s,支持串行ATA、PCIe、1G以太网等对外高速接口,性价比极高。

XC6SLX16与AD9910主要接口总线图见图3。FPGA工作时,首先启动初始化,对自身、AD9910进行初始化设置片选CS、I/O Reset等信号时序,再设定八位Profile寄存器数值,当OSK信号有效时信号幅度相位被写入暂存于Profile, Profile寄存器由专门时钟信号Sync Clock决定其最短刷新时间,Sync Clock由系统时钟四分频而得即250MHz。Profile使能随I/O Update控制时序生效而定时刷新输出频率信号频率值。

图3 系统架构

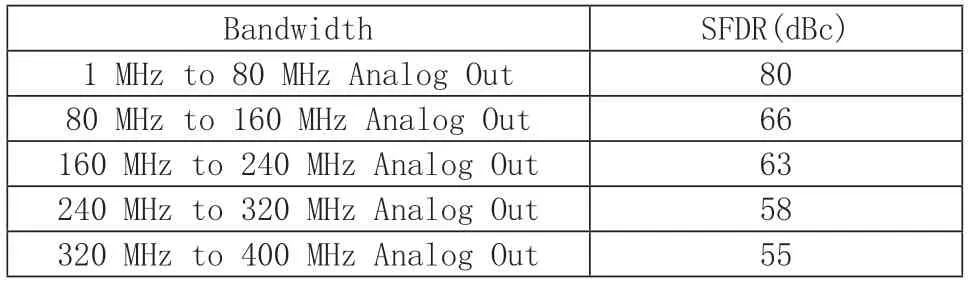

2.2.2 倍频链路设计

根据指标要求,该产品频率分辨率≤20Hz,频率范围1.2~1.6GHz,杂散抑制不少于55dBc,幅度0±1.5dBm。AD9910频率分辨率在最大系统时钟1GHz时为109/232≈0.23Hz,因此倍频链放大倍数不大于64。表1为AD9910宽频带范围下的杂散抑制参数,由图可见,仅考虑芯片本体,只有输出信号频带为0~240MHz时杂散抑制不少于60dBc,后级倍频、信号放大等均会对此产生影响,如果因为一味地减少频率分辨率而增大AD9910输出信号频宽,虽然利用高性能滤波电路可能达到抑制杂散的参数指标,但信号质量必定不佳存在一定风险,增加后期调试和电装复杂程度和工作量。

表1 AD9910 SFDR

综合考虑所有条件,设置AD9910输出信号频率范围72.5~102.5MHz,采用四级倍频链。又因在每一次倍频后均需滤除杂散,前端DDS输出信号频宽达30MHz但最大频率仅102.5MHz,若前端采用宽带带通滤波器,由于链路中有放大电路,系统整体滤波效果必然很差,对于滤波器件的性能和电路搭建要求很高。因此将AD9910输出信号划分为10个频段,这样四路倍频链中滤波器最小带宽分别为3MHz、6MHz、12MHz、24MHz。前端与后端滤波电路带宽均较小。本项目无合适的数控滤波器货架产品,单个倍频链及前后连接采用程控射频开关—滤波器—程控射频开关—倍频—程控射频开关的设计,共有四级倍频。10个频段的选通主要由XC6SLX16和2个HMC252射频开关完成,HM252为3线6出高速无衰减射频开关。射频开关选频码由XC6SLX16产生,与频率控制字一起智能发送。图4为倍频链架构。

图4 倍频链架构

3 试验结果与结论

如图5所示,该系统输出幅度满足设计要求0±1.5dBm,且设计中具有调节容限,方便随时自主调节。设置扫频范围10kHz时,可以明显看出杂散抑制超过55dBc;经测试在1.2~1.6GHz的全频带范围内,杂散抑制均大于55dBc。经测试验证输出信号频率分辨率为5Hz,满足设计指标。

图5 测试结果