软件无线电架构的导航接收机模拟前端设计

孙金中,付秀兰,高艳丽

(安徽芯纪元科技有限公司,安徽 合肥 230031)

0 引言

随着信息技术的飞速发展,无线接收机的实现形式也发生了巨大变化,原来的超外差、低中频、零中频架构的无线接收机已经不能满足现代通信、雷达、电子对抗等多频段、多模式及多功能的电子装备的需求,软件无线电架构的接收机因其自身的结构特点,是未来无线通信、多模导航、多功能一体机的理想选择[1-4]。

软件无线电架构的接收机的设计难点是设计高性能的接收机模拟前端电路。随着集成电路技术的飞速发展,模数转换器的转换速度越来越高,使得设计单片软件无线电架构的接收机成为了可能[5-6]。

本文设计了一款软件无线电架构的接收机模拟前端用于多模卫星导航系统的射频信号接收及转换,从而实现单片软件无线电架构的导航SoC 芯片。该模拟前端通过低功耗高速模数转换器直接对导航信号进行射频采样量化转换,在数字域完成频率变换及信号处理,数字电路随着集成电路工艺的进步面积和功耗可以不断降低,由于内部集成了宽带的射频放大器和高速ADC可以对不同模式的导航信号全部进行采样量化转换,实现了单个模拟通道完成多模导航信号的处理,从而实现系统终端的最优化设计[7-9]。

1 电路设计

1.1 软件无线电架构的接收机模拟前端设计

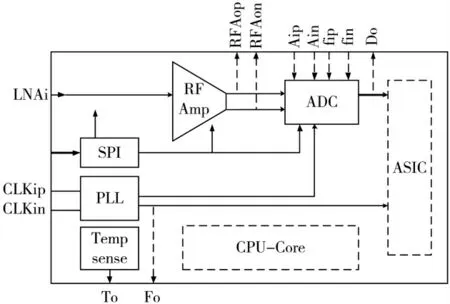

如图1 所示,本文设计的高性能接收机模拟前端芯片内部集成高增益射频放大器、低功耗高速ADC、锁相环等,外围只需要搭载天线连接低噪声放大器(LNA)、声表射频滤波器(SAW)、时钟和电源即可完成多模导航卫星射频信号的接收放大滤波及模数转换。该接收机模拟前端内部只需要加入用于数字信号处理的基带电路及CPU 电路就可构成单片的多模导航SoC 芯片。

图1 接收机模拟前端的系统架构

1.2 宽带射频放大器的设计

高性能接收机模拟前端芯片中的射频放大器主要完成导航信号的低噪声放大,使得微弱的导航信号及噪声放大到ADC 可以完成量化的信号电平值[10]。由于不同模式导航信号的频率差异较大,为了满足北斗、GPS、GlONASS 等导航信号的射频放大,该射频放大器的带宽设置为1.1 GHz 到1.7 GHz,增益设计为38 dB。

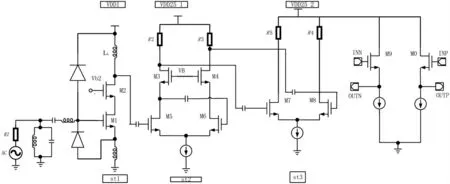

本文设计的射频放大器结构如图2 所示,放大器包括三级放大器电路和一级输出驱动电路,在第一级的输入还加入了宽带匹配电路,宽带匹配电路全部在片上实现。

图2 射频放大器顶层电路原理图

1.3 低功耗高速模数转换器ADC 的设计

射频采样ADC 主要完成射频信号的采样量化,将模拟信号转换成对应的数字信号提供给后端的数字基带处理电路进行处理。该模块的主要难点是射频采样,由于要量化的信号频率高达1.5 GHz 以上,如果采用低通奈奎斯特ADC 需要转换时钟超过3 GHz,这在具体的电路实现上是十分困难的,而且电路实现所需的功耗、面积也是十分不经济的。然而导航信号的带宽一般在几十兆赫兹以内,根据带通奈奎斯特采样定律,采用欠采样的ADC 来完成采样量化转换实现具体的电路功能。该ADC 的模拟全功率输入带宽要包括各模式下的导航信号频率,同时要具有足够的动态范围以满足系统抗饱和的要求,该射频采样ADC 要实现的具体技术指标为7 bit/250 MS/s,模拟输入带宽为2.5 GHz,功耗低于10 mW。

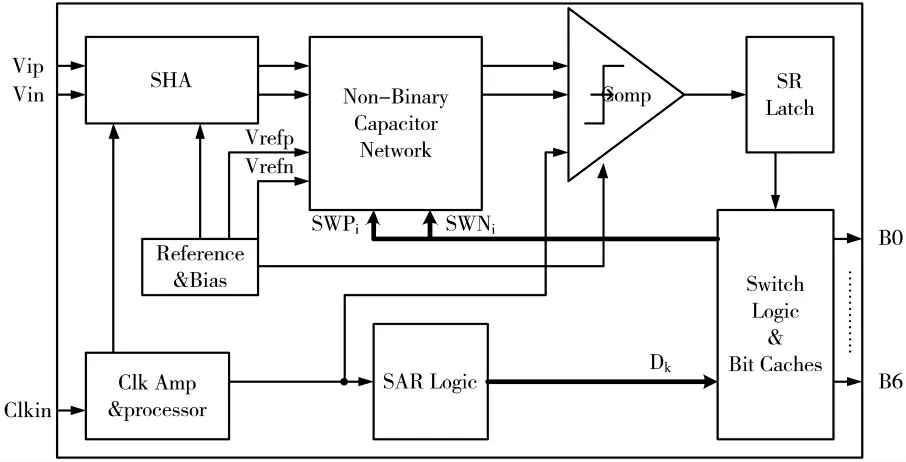

本文设计的高速ADC 结构框图如图3 所示,该ADC 是典型的逐次逼近SAR ADC 架构,从结构框图可知,该ADC 可划分成如下电路子模块:宽带采样保持电路、非二进制权重电容DAC 电路、动态比较器和锁存输出电路、逐次逼近控制逻辑电路和开关电容阵列控制逻辑产生电路、输出控制和驱动电路、时钟放大和处理模块以及基准产生和偏置电路等[11-12]。

图3 射频采样SAR ADC 结构框图

1.4 高性能时钟锁相环的设计

在高性能接收机模拟前端芯片中,锁相环主要产生用于ADC 的系统时钟。由于ADC 直接对射频信号完成采样量化,时钟信号的质量将限制转换后数字信号的信噪比,因此本SoC 芯片中的锁相环需要设计成一个低噪声、性能稳定的锁相环。

本文设计的倍频锁相环结构框图如图4 所示,该锁相环由鉴相器(Phase Detector)、电荷泵(Cpump)、环路滤波器、四级压控差分振荡器、相位内插器、电压调节器、时钟选择器、分频器和测试电路组成。采用1.2 V/2.5 V 双电源供电,其中1 V 主要给鉴相器、分频器等数字电路供电;2.5 V 电源提供给电压基准源产生出电荷泵、环路滤波器、压控振荡器、相位内插器等模块所需的工作电压。

图4 锁相环电路结构框图

2 版图设计

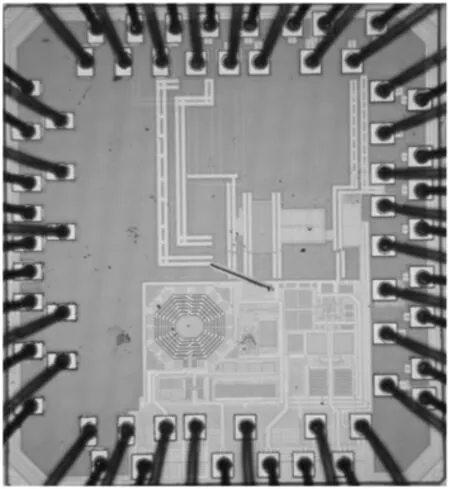

本文设计的接收机模拟前端芯片采用55 nm CMOS工艺设计实现,模拟前端内部集成了射频放大器、时钟锁相环、ADC 和SPI 接口(便于测试)模块,ADC 的输出采用LVDS IO 输出,整个芯片的大小为1 200 μm×1 320 μm。模拟部分采用全定制的版图设计方法,在设计中重点考虑射频放大器和ADC 之间的信号隔离及匹配,同时为了降低锁相环时钟信号对射频放大器的干扰,将射频放大器放在最下边,锁相环放在最上面。该芯片的显微照片如图5 所示。

图5 模拟前端芯片的显微照片

3 测试结果

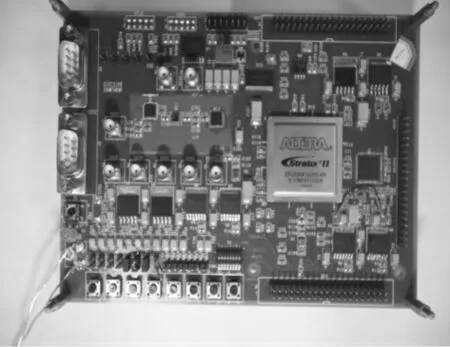

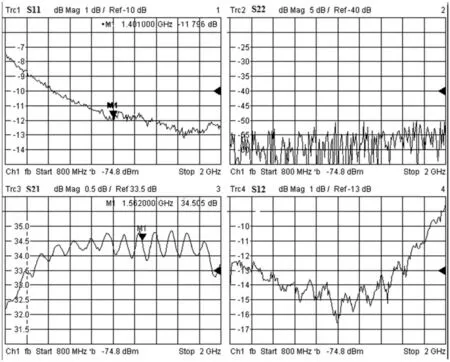

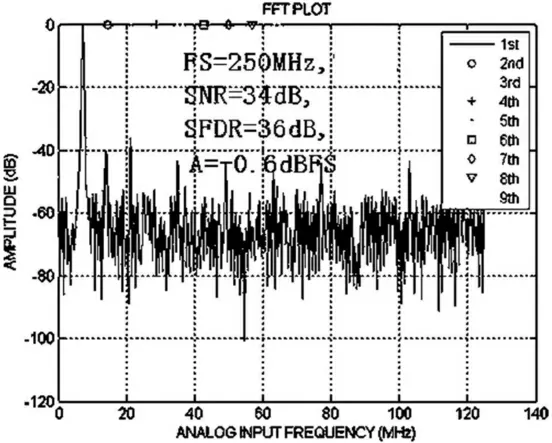

根据上述方案实现的接收机模拟前端芯片采用数模混合集成电路的设计技术,结合超深亚微米VLSI 设计技术不仅在功能上全面达到了设计要求,同时在芯片功耗、面积、可测性及使用灵活性方面获得了良好的效果[13-14]。基于该接收机模拟前端芯片的系统测试平台综合考虑结构、环境适应性、可靠性、电磁兼容性、长期稳定性等因素。接收机模拟前端系统测试终端如图6 所示,射频放大器的S 参数测试结果如图7 所示。低功耗ADC 的测试结果如图8 所示。该接收机模拟前端主要测试结果汇总如表1 所示。

表1 模拟前端芯片的测试结果汇总表

图6 接收机模拟前端芯片测试终端

图7 S 参数的测试结果

图8 ADC 的动态测试结果

4 结论

基于软件无线电架构的接收机模拟前端电路通过电路设计并实现,并已成功应用在多模导航SoC 芯片中;通过对接收到的卫星导航信号直接射频采样量化转换成对应的数字信号,在数字域完成频率变换,通过单个模拟接收通道处理多个不同频率不同制式的导航信号,极大地降低了模拟电路的规模及功耗。