太赫兹波导封装技术的研究与应用

刘 军,于伟华,吕 昕

(1.中国电子科技集团公司第五十四研究所北京研发中心,北京 100070;2.北京理工大学毫米波与太赫兹技术北京市重点实验室,北京 100081)

1 引言

太赫兹(terahertz,THz)波通常指频率位于100 GHz~10 THz(波长30 μm~3 mm)范围内的电磁辐射,其覆盖了微波高频段、亚毫米波段以及红外低频段.在过去的几十年中,半导体技术的发展促进了太赫兹技术在太赫兹成像、太赫兹安检、太赫兹通信、太赫兹雷达以及微小目标探测等不同领域的应用[1~7].太赫兹半导体器件和单片微波/太赫兹波集成电路(Monolithic Microwave/Terahertz Integrated Circuit,MMIC/TMIC)芯片的封装设计是实现太赫兹系统应用必不可少的关键技术之一.随着工作频率升高到太赫兹频段,器件及芯片尺寸减小,出现了陶瓷技术、微加工技术、3D 打印技术等新兴概念并实现小型化、质轻的封装结构,但是就目前对太赫兹封装技术的研究来看,采用具有损耗低、稳定性好、可靠性高以及可重复性强等优点的金属矩形波导形式封装结构仍然是最为有效、可靠和可行的方法.矩形波导一般采用上下腔体分离的方式利用铣削工艺进行分别加工,目前铣削工艺的加工精度可以达到微米级别,也就是意味着波导封装结构可以应用于3 THz以内[8,9].

目前在太赫兹频段采用的波导封装方式有:混合探针波导封装[10];单片集成E 面探针波导封装[11];单片集成偶极子探针波导封装[12];鳍线过渡波导封装[13]等.随着频率的升高,键合线电感效应增加从而引起反射,恶化封装器件的性能;单片集成E 面探针在较大的沟道尺寸装配MMIC 芯片与较小的沟道尺寸抑制高次模之间存在冲突;鳍线过渡结构适用于差分放大器.通过研究发现,混和探针波导封装形式和单片集成探针波导封装形式仍然是太赫兹频段常用的封装形式.因此,本文基于波导-微带探针过渡结构对文献[14]中研制的D 波段放大芯片进行了混和探针波导封装设计,并对太赫兹频段单片集成探针波导封装结构开展研究,在220 GHz 频段进行设计验证,为将来太赫兹全集成芯片设计奠定基础.

2 D波段放大器封装模块研制

2.1 波导-微带探针过渡结构仿真分析

为了实现波导与微带之间最大能量转换也即实现工作带内波导与微带之间良好阻抗匹配,需要设计具有良好性能的探针过渡结构.波导-微带探针形式结构简单,便于加工,并且过渡结构具有良好的带宽和传输性能,非常适用于毫米波太赫兹波频段.

本次D 波段波导-微带探针过渡结构选用E 面探针来设计实现,在HFSS(High Frequency Structure Simulator)中建立的波导-微带E面探针过渡结构的模型如图1(a)所示.其中,输入波导口为WR-7 标准波导,介质基板采用介电常数为3.78、厚度为50 μm 的石英基片,微带线金层厚度为4 μm.为了减小装配误差,在探针结构左侧设计了对位标记,该结构对整个探针过渡结构性能不产生影响,只起到对位参考的作用.同时为了抑制波导模和微带线的高次模等,拓宽了金属屏蔽腔的宽度,此模型中金属屏蔽腔宽度为0.56 mm.根据文献[15],计算出探针尺寸、50 Ω 微带线宽度以及探针中心与短路面的距离,以此为探针结构初值,在HFSS 中建立结构模型.首先对结构中关键尺寸进行手动调节,使得过渡结构的带宽满足性能要求,随后通过设置优化变量的方式对探针的长度和宽度、短路面的距离以及阻抗变换结构等关键尺寸进行优化,最终得到探针过渡结构的仿真结果如图1(b)所示.通过仿真结果可以看出,在110~170 GHz 频带范围内,回波损耗S11 优于20 dB,插入损耗S21优于0.1 dB,满足设计要求.

图1 HFSS中E面探针结构及仿真结果

2.2 D波段放大模块测试

为了验证装配后波导-微带探针过渡结构性能,首先对背靠背探针结构进行了测试分析,实际装配完成的背靠背探针过渡结构如图2 所示.采用Rohde &Schwarz ZVA50 矢量网络分析仪,搭配Rohde&Schwarz ZC170(110~170 GHz)的扩频模块对D 波段波导-微带探针背靠背过渡结构进行测试.

图2 D波段背靠背探针过渡结构内部装配图

图3(a)展示了D 波段背靠背探针过渡结构的测试与仿真的对比结果,测试结果显示,在整个D 波段内,回波损耗S11 优于15 dB,插入损耗S21 优于2.4 dB.通过图3(a)可以看出,实测结果与仿真结果有一定的差距,观察图2 探针装配图可以发现左侧导电胶涂抹过多,导致导电胶溢出.对于该情况在HFSS 中进行仿真分析,发现当导电胶涂抹溢出15 μm 的时候,仿真与测试的回波损耗基本一致,具体对比情况如图3(b)所示.除此以外,还存在导电胶的涂抹不够均匀和部分区域涂抹不够饱满等情况,人工装配误差以及腔体的加工精度误差等都会导致过渡结构的性能恶化.

图3 背对背结构测试结果对比与分析

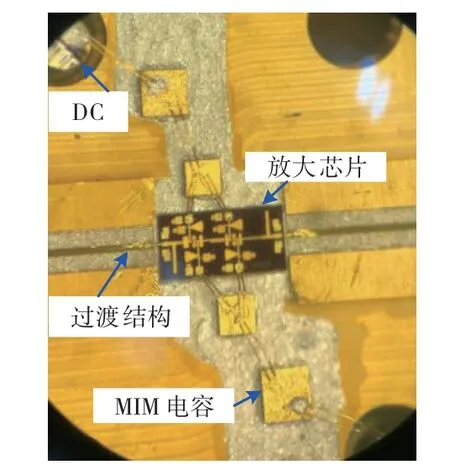

D波段放大芯片装配过程主要包括以下几个部分:波导-微带探针过渡结构的装配、D 波段MMIC 芯片装配、芯片电容装配以及玻璃绝缘子和跳线连接等.在装配过程中探针的对位和芯片与探针之间的金丝键和对整个装配过程的影响最大,因此在装配过程中要格外注意,最终在波导腔体中装配完成的放大芯片如图4所示.搭建的D 波段S 参数测试平台包括矢量网络分析仪、D波段扩频模块、直流电源,同时测试系统还包括功率计,以便对放大模块进行功率特性的测试.在测试系统进行测试之前,首先进行系统的预热及校准,以便获得准确的电路S参数特性.

图4 放大器芯片内部装配示意图

模块测试得到的S 参数与在片测试得到的S21 对比如图5(a)所示,由图可以看出封装模块在139 GHz测试得到最大增益为10.8 dB,在137~144 GHz 频率范围内,增益大于7.8 dB,输入端回波损耗S11 优于5 dB,输出端回波损耗S22优于8.5 dB.

由于在139 GHz处增益值最高,因此对该频点的功率特性进行了测量,该频点的功率特性曲线如图5(b)所示.受限于矢网输出功率,本次只对输入功率范围为-20~-11 dBm 进行了测试,随着输入功率的增加,输出功率逐渐增加,并且增益出现一定程度的压缩,最大输出功率约为0.56 mW.

图5 封装放大器测试结果

与在片测试结果对比看出,封装与在片测试结果曲线变化趋势基本一致,但是封装后芯片性能下降严重,封装损耗大于5 dB.究其原因可能在于,芯片接地共面波导(Grounded Coplanar Waveguide,GCPW)焊盘尺寸为52 μm,本次封装只能采用单根直径25 μm 的金丝进行键合连接,由于频段较高,金丝在此频段寄生效应明显,且只采用单根金线,造成芯片封装后性能恶化严重.

对拱高50 μm、跨距140 μm 的单根25 μm和两根18 μm 金线在HFSS 中进行建模仿真分析,仿真分析对比结果如图6所示.由图可以看出,随着频率升高,键合性能下降,在140 GHz处,单根金线插损约为0.78 dB,两根金线插损约为0.48 dB,因此采用两根键合线可以改善键合性能.除此以外,对不同拱高和跨距的单根25 μm 键合性能进行仿真分析,具体如图7 所示.由图7可以看出,随着拱高和跨距的增加,键合性能恶化.根据对单根25 μm 金线的仿真结果,以及前文背对背结构的测试结果可知,在120~160 GHz 频段范围内,插损理论值约为2.9~4.6 dB,由图7 也可以看出金线键合尺寸的变化对键合性能影响明显.

图6 单根25 um与两根18 um金线仿真结果对比

图7 不同拱高和跨距下金丝键合性能仿真分析

因此,采用两根直径18 μm 的金线进行键合连接可以降低金丝键合对封装后芯片性能的影响,同时将探针结构中的微带线换成共面线也会降低过渡结构的损耗.

3 D波段放大器封装模块研制

通过对前文D 波段芯片的测试结果以及对金丝键合性能的仿真分析可以发现,基于波导-微带探针结构的混和探针波导封装对芯片GSG(Ground-Signal-Ground)焊盘尺寸、金丝尺寸以及装配工艺等都提出了较高的要求,同时,金丝键合装配工艺对于太赫兹频段芯片封装性能的影响具有不确定性.因此,在太赫兹芯片封装方面,研究基于波导-集成探针过渡形式的封装结构具有重要意义.

3.1 波导-集成探针过渡结构仿真分析

E 面探针和偶极子的方式都会引起高次模或者电磁场谐振等问题,解决该问题的方式可以减小沟道尺寸,但是这就限制了E 面探针和偶极子的尺寸,从而进一步限制了太赫兹芯片尺寸.本文基于50 μm 厚度的石英介质设计了220 GHz 波导-集成探针过渡结构,采用偶极子天线过渡结构的方式可以实现宽尺寸电路的波导封装而不引起其他形式的波导模式,同时可以完美的在磷化铟(Indium Phosphide,InP)等半导体介质上复现.图8 展示了本文设计的波导-集成探针过渡结构HFSS模型,输入输出采用WR4标准矩形波导.

图8 波导-集成探针过渡结构模型

该结构包括阻抗变换器、偶极子结构、共面槽线-微带线巴伦结构以及50 Ω 微带传输线等.输入的电磁波首先通过阻抗变换器被偶极子结构接收,然后经过共面槽线-微带线过渡巴伦结构将波导模式转换成微带线模式.阻抗变换器作用类似于E 面探针过渡结构中的探针,主要用于集成过渡结构的阻抗匹配、电磁波模式转换以及改善损耗性能和带宽性能等.共面槽线-微带线转换巴伦结构采用了45°的扇形线,因为其相比于微带线具有更宽的工作带宽,同时减小了整个结构长度.该结构采用厚度为50 μm、介电常数为3.78的石英介质进行设计实现.

经过仿真优化,波导-集成探针过渡结构的相关尺寸如图9(a)所示,仿真结果如图9(b)所示.通过仿真结果可以看出,在208~236 GHz 频带范围内,回波损耗S11优于10 dB,插入损耗S21优于1 dB;在211~235 GHz范围内,回波损耗S11 优于15 dB,插入损耗S21 优于0.85 dB.

图9 波导-集成探针过渡结构及HFSS仿真结果

3.2 波导-集成探针过渡结构测试

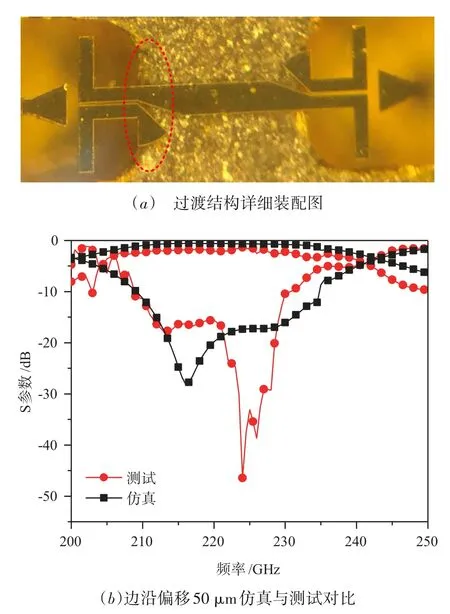

波导腔体采用上腔与下腔的方式进行装配,整个模块尺寸为15 mm×10 mm×15 mm,探针过渡结构装配实物图如图10所示.

图10 集成探针过渡结构实物图

对过渡结构模块测试采用中电四十一所AV3672E矢量网络分析仪和3643R(170~260 GHz)扩频模块进行S参数测试.图11展示了该结构的测试结果与仿真结果的对比,测试结果表明:该结构在208~233 GHz 频带范围内,插入损耗S21 优于3 dB,回波损耗S11 优于8 dB,在224 GHz 频点处,获得该结构的最优性能,其插入损耗S21为1.3 dB,回波损耗S11为46.4 dB.

通过图11 可以看出,测试与仿真之间存在较大的差距,通过观察发现腔体结构加工存在较大误差,理想装配情况应该是扇形边线与两侧垫台对齐,但是实际加工的垫台长度变短,导致左侧扇形边线对齐后,右侧不能对齐,如图12(a)红色框内所示.

图11 集成探针过渡结构S参数测试与仿真对比结果

在HFSS 中对该误差进行仿真分析,发现当金属垫台缩短50 μm 的时候,仿真与测试结果吻合情况较好,如图12(b)所示.除此以外,随着频段升高,芯片尺寸减小,装配带来的误差也不可避免对过渡结构性能造成很大的影响,如前文对D 波段背靠背过渡结构的分析所述,在装配过程中因导电胶涂抹不均匀等也会对结果有较大的影响.

图12 集成探针过渡结构测试结果分析

虽然因加工误差、装配等因素对220 GHz 波导-集成探针过渡结构的性能产生一定影响,但从测试结果来看,该结构在208~233 GHz频段范围内仍然具有适用性.经过改进加工工艺误差以及进一步的仿真分析等措施以后,该结构可以在InP 等半导体介质上实现完美复现,为以后全集成芯片的设计提供了基础.

4 结论

本文主要开展太赫兹波导封装相关研究工作,首先利用E 面探针的形式对自研的D 波段MMIC 芯片进行封装,对装配后的波导模块进行测试,测试结果表明最大增益为10.8 dB@139 GHz.受限于GSG 焊盘尺寸,本次只采用单根25 μm 金丝进行键合连接,频段内损耗大于5 dB.随着频率升高到太赫兹频段,金丝键合引起的寄生效应明显,导致封装性能严重恶化,同时随着焊盘尺寸的减小,对金丝键合的尺寸和工艺提出了更高的要求.为了消除因金丝键合对封装后芯片性能引起的不确定影响,本文设计了一种适用于太赫兹频段的波导-集成探针过渡结构,并在220 GHz 频段内进行设计验证.因加工精度和装配误差等原因,波导-集成探针过渡结构的测试与仿真结果之间存在一定差距,但是该结构在该频段仍具有一定的实用价值,并且可以拓展到太赫兹其它频段,为将来全集成芯片设计提供基础.