2~6GHz高谐波抑制低噪声放大器芯片研究与设计

薛源,吴浩洋

(中国电子科技集团公司第十三研究所,河北 石家庄 050051)

0 引 言

近几十年来,随着通信系统变得日益复杂,对高性能单片微波集成电路的需求也日益增长。低噪声放大器广泛应用于手机、基站和卫星通信中,其主要指标包括小信号增益和噪声系数。随着系统在多功能集成方面的迅猛发展,单个系统集成多个频段的器件和子系统成为重要的发展方向,如何规避不同频段器件之间的干扰是当前射频系统领域里亟待研究的重要课题。具体对于低噪声放大器芯片而言,如何降低二次谐波能量就成了一个重要的研究和设计方向,表现在具体指标上,就是提高二次谐波抑制比。通常而言,对于宽带低噪声放大器,二次谐波抑制比极其有限,约为10 ~15 dBc,难以满足通信系统的典型要求(35 ~40 dBc)。

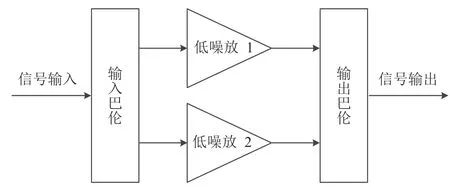

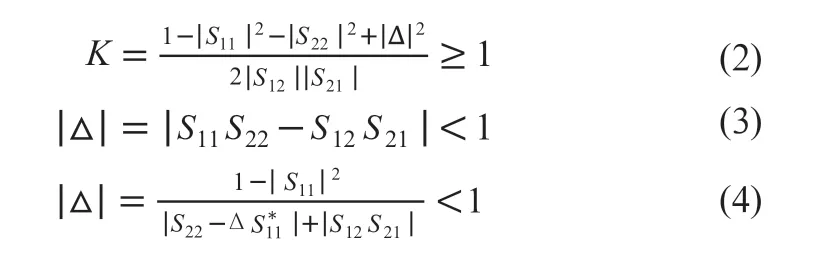

本文创造性地提出了一种新型电路拓扑结构,该结构能够在有限地牺牲噪声系数指标的前提下,大幅度提升二次谐波抑制比。该新型拓扑结构主要由输入巴伦、两个相同的低噪声放大器和输出巴伦构成,如图1所示。输入信号进入芯片后,经由输入巴伦,信号一分为二,且相位相差180°,然后各自通过一个相同的低噪声放大器放大,同时放大器产生二次谐波分量,此后再经由一个输出巴伦进行主频信号的合成,同时抵消两个放大器产生的二次谐波分量,实现二次谐波的零输出。实际应用中,由于巴伦结构无法做到完美的相位相差180°,因此难以实现二次谐波的完全消失,但是由矢量合成原理可知,输出端的二次谐波分量会有明显的降低。

图1 高谐波抑制低噪声放大器电路拓扑

基于此拓扑结构,利用GaAs pHEMT 单片工艺,本文设计并流片了一款2~6 GHz 低噪声放大器,测试表明,噪声系数较低,二次谐波抑制能力得到较大幅度地提升,满足通信系统的要求,验证了高谐波抑制拓扑结构的有效性。本文首先对2~6 GHz宽带低噪声放大器的设计进行详细的论述,其次介绍巴伦结构的理论和设计方法,最后描述由巴伦合成的低噪声放大器的各个指标和性能,特别是与单个低噪声放大器的性能对比。

1 宽带低噪声放大器的设计

对于低噪声放大器MMIC 芯片设计,首先应该对单个HEMT 器件进行仿真,以确定器件的最优尺寸。本次设计采用三级放大以满足增益要求。对器件进行仿真,第一级器件的尺寸为4×33 μm 时,噪声系数最优。第二、三级器件尺寸的选择主要考虑增益和线性,通过单管的仿真对比分析,器件尺寸4×27 μm 和4×30 μm 能满足系统指标要求。在每级管子尺寸确定之后,结合直流仿真和噪声系数的仿真,确定偏置电压和电流。电路使用单电源自偏置结构,可以通过调整源极自偏电阻的大小来优化偏置电压,以期达到最优噪声系数的最佳线性特性。

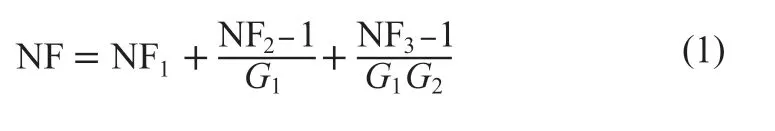

在低噪声放大器设计中,三级放大电路总的噪声系数NF 由式(1)决定,其中NF、NF和NF分别是第一级管子、第二级管子和第三级管子的噪声系数,,是第一级和第二级放大的增益。根据该公式,在输入匹配电路设计中,任何无源元件,包括电阻,电容和传输线,均会直接恶化整个电路的噪声系数。除此之外,低噪声放大器输入匹配设计的根本原则在于用最少的无源元件将HEMT 器件的最佳噪声阻抗共轭匹配至50 欧姆。4×33 μm 器件的噪声系数圆如图2所示。

图2 器件4×33 μm 的噪声系数圆

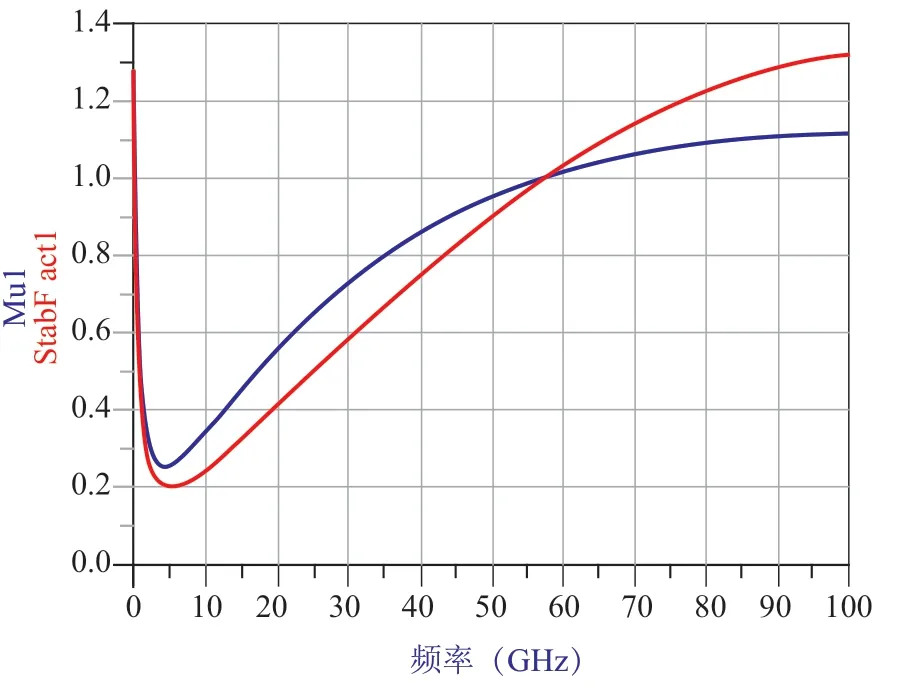

为了保证低噪声放大器的绝对稳定,根据公式(2)、公式(3)和公式(4),首先对第一级的HEMT 器件单独进行稳定性分析和评估。单管稳定性仿真分析如图3所示,可见从350 MHz 至58 GHz 频率范围内,器件存在条件不稳定。

图3 器件4×33 μm 的稳定性仿真

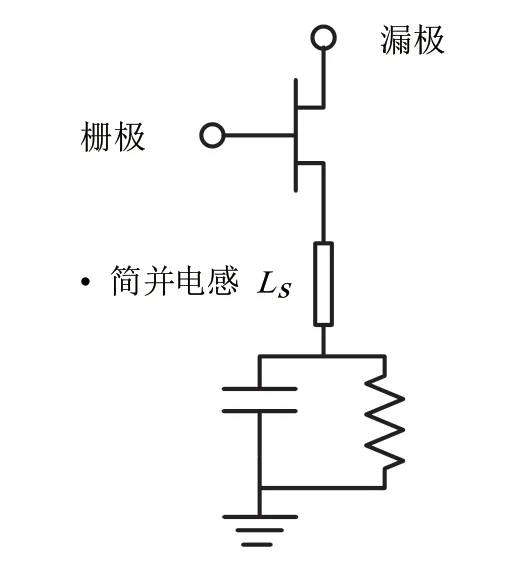

采用源极简并电感技术可以有效提高电路的稳定性,并且能有助于将器件的输入阻抗匹配至50 欧姆。原理图如图4所示,设计中,简并电感L连接HEMT 器件的源极和RC偏置电路,从而将器件的输入阻抗提高,减小了输入阻抗与50 欧姆的差距,使得输入匹配电路的设计更为简单。此外,L的存在构成了器件从输出到输入的负反馈,大大提高电路的稳定性,同时有利于提高电路的线性度。然而,源极简并电感带来这些优点的同时,也带来了缺点,其中最主要的是增益的降低。根据有效跨导系数的表达式(式(5)),源极电感会引起有效跨导的降低,从而导致电路增益的降低。

图4 源极简并电感提高稳定性原理图

因此简开源极电感大小的选择需要折中设计考虑,反复迭代设计,选择最优值。

其中,g为器件本征跨导,L为源极简并电感,C为栅极到源极的等效电容。

低噪声放大器的工作频段要求是2~6 GHz,相对带宽达到100%,级间匹配需要采用特殊的宽带匹配设计,典型的拓扑结构为RC 串联负反馈,如图5所示,即将有源器件的漏极端用RC 串联电路与有源器件的栅极端相连,构成带阻性的负反馈。根据增益带宽乘积为一定值的规律,阻性负反馈降低了器件的增益,但是却拓宽了其工作带宽,同时还能有效改善稳定性,将潜在的自激振荡信号衰减为零或是打破信号的正向反馈链路,避免不稳定现象的产生。

图5 RC 串联负反馈结构

低噪声放大器的原理图使用两级放大拓扑,采用源极简并电感技术和RC 串联负反馈技术,带宽达到2~6 GHz,版图电磁仿真结果显示,噪声系数约为4.1 dB,增益28.5 dB,值得注意的是,在压缩1 dB 附近,该单独低噪声放大器的二次谐波抑制比仅为20 dBc。与系统的指标要求(35 dBc)相差甚远,因此,针对高谐波抑制比的要求,需要做特殊的设计考虑。采用巴伦合成式的拓扑结构有助于抵消二次谐波分量。

2 宽带巴伦的设计

巴伦是用于单端信号转差分信号,或者是实现差分信号合成为单端信号的无源元件。常用于倍频器、平衡式混频器以及偶极子天线中。实现巴伦的方式和结构有很多种,其中最广泛使用的结构形式就是Marchand 巴伦。Marchand 巴伦由两个四分之一波长耦合线构成,如图6所示。具有插入损耗低,工作频带宽等优点。

图6 Marchand 巴伦结构示意图

将两个相同的低噪放通过巴伦结构合成,能使得每个低噪放产生的二次谐波分量相抵消。输入信号进入芯片后,经由输入巴伦,信号一分为二,且相位相差180°,然后各自通过一个相同的低噪声放大器放大,同时放大器产生二次谐波分量,此后再经由一个输出巴伦进行主频信号的合成,同时抵消两个放大器产生的二次谐波分量,实现二次谐波的零输出。

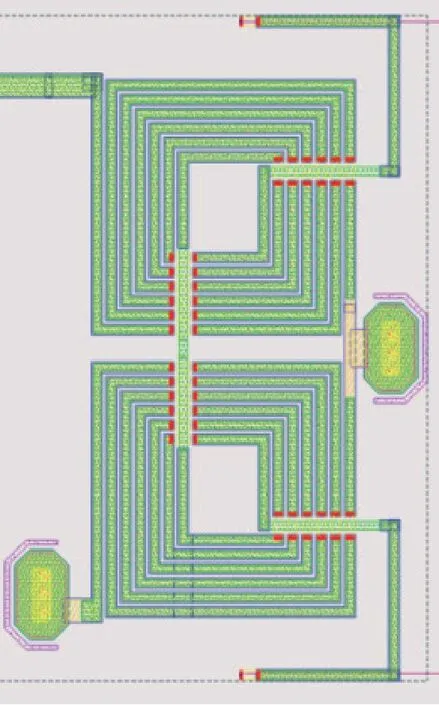

然而分布式的Marchand 巴伦尺寸较大,难以在常规芯片尺寸上实现,因此本文的设计中,采用集总元件构成Marchand 巴伦,优点是尺寸小,方便集成,缺点是插损较大,平衡性较差,其最终实现的版图结构如图7所示。单独集总式巴伦的仿真结果如图8所示,单路插损在-5 dB 左右,幅度之差在1 dB 以内,相位之差在180°附近。

图7 集总式Marchand 巴伦版图结构

图8 单独巴伦仿真结果

3 高谐波抑制比低噪放测试结果

本文设计的宽带低噪声放大器采用砷化镓pHEMT 单片工艺制备,并通过探针台在片测试了芯片的增益、二次谐波抑制比、噪声和压缩1 dB 输出功率等性能指标。

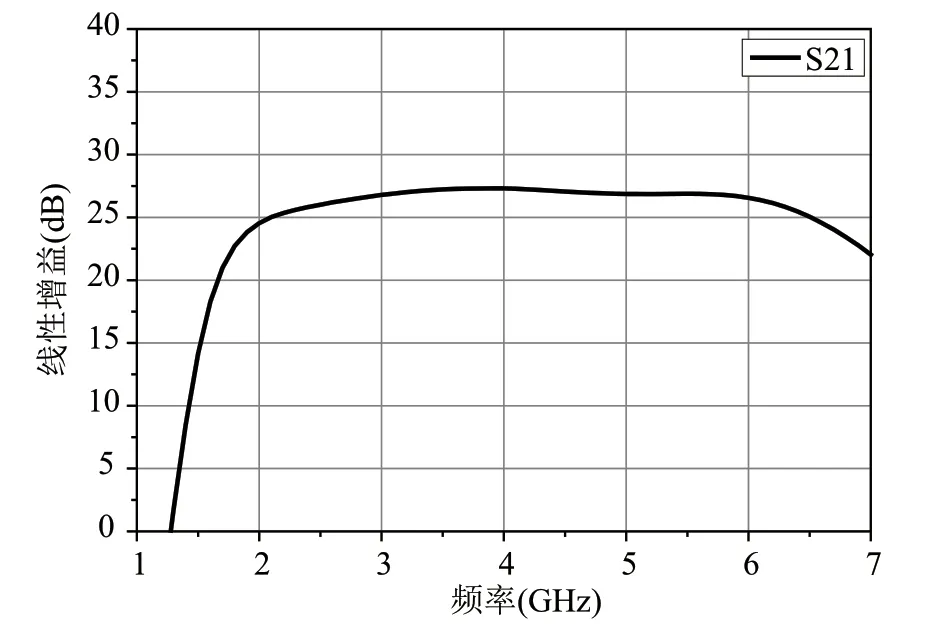

如图9所示,增益决定了放大器对信号的放大能力,对于低噪声放大器,线性增益的平坦度也非常关键。本文设计的高谐波抑制比低噪放达到了27 dB 的线性增益,且在3~6 GHz 带宽内增益波动小于1 dB。根据公式(1),增益越大,越有利于放大器噪声的降低。因为巴伦结构引入了较大的插损,所以该高谐波抑制比低噪放的增益与单独低噪放相比较低。

图9 放大器线性增益测试结果

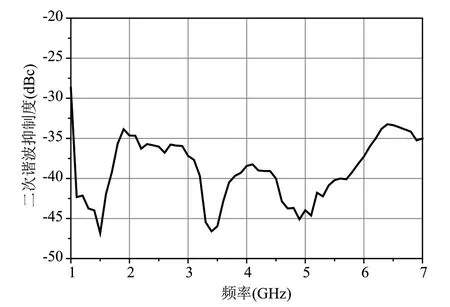

本文设计的高谐波抑制比低噪放的二次谐波抑制比测试结果如图10 所示。该放大器在2~6 GHz 的宽带内,实现了超过35 dBc 的二次谐波抑制比。单低噪放的二次谐波抑制比为22 dBc,与之相比,使用本文提出的巴伦合成拓扑结构设计出的单片低噪放芯片,对二次谐波的抑制效果提升明显,达到了通信系统的典型要求(35~40 dBc)。由于实际设计的巴伦无法实现完美180°的相位差,实际芯片依然存在二次谐波分量。理论上,通过对设计和工艺的优化,使巴伦的差分相位差更加接近180°,即可进一步提高使用该拓扑结构放大器芯片二次谐波抑制比。

图10 放大器二次谐波抑制比测试结果

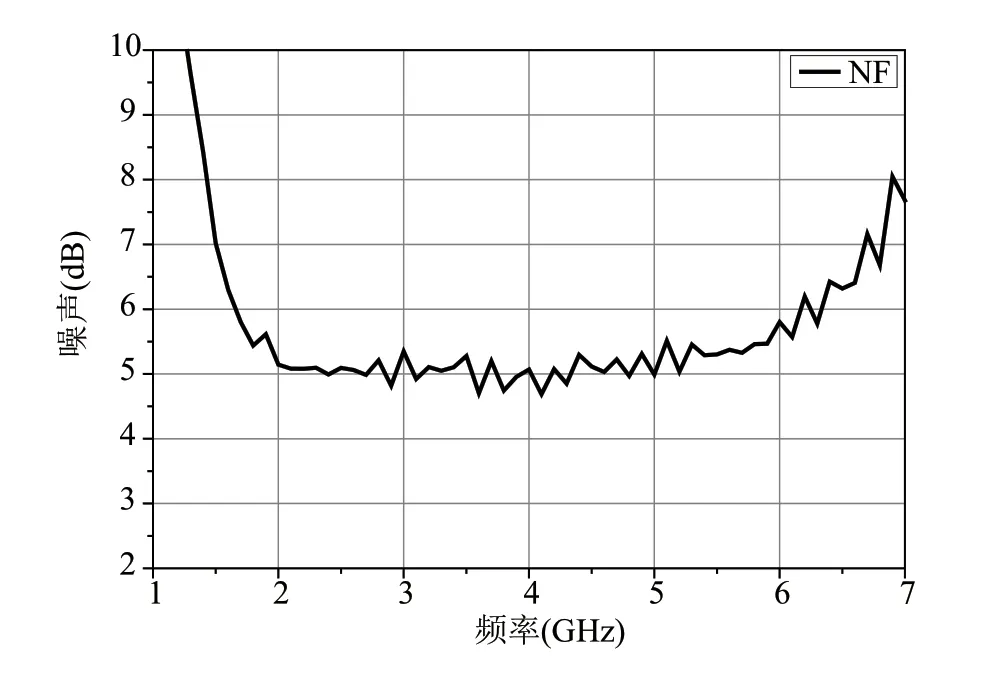

本文设计的高谐波抑制比低噪放芯片噪声系数为5.5 dB,测试结果如图11 所示。与单低噪放相比,噪声系数有明显增加。这是因为输入巴伦和相应的匹配网络,增加了输入匹配网络中的无源元件,恶化了放大器第一级的噪声系数。而根据公式(1)可知,第一级的噪声对整个放大器的噪声系数影响很大,所以在输入端引入巴伦结构,增加了整个低噪放芯片的噪声系数。

图11 放大器噪声系数测试结果

本文设计的高谐波抑制比低噪放芯片为7 dBm,测试结果如图12 所示。压缩1dB 输出功率越大,放大器就能对更大的输入信号进行线性放大。当输入信号过大时,经过放大器的输出信号超过,输出信号会由于压缩而失真。

图12 放大器压缩1 dB 输出功率测试结果

4 结 论

本文针对通信系统应用,提出了一种采用巴伦合成拓扑提高二次谐波抑制比的方法,利用该方法,设计并流片了一款频率范围为2~6 GHz 的高谐波抑制比低噪放芯片。该芯片在整个频段内的增益典型值为25 dB,噪声系数5.5 dB,输出压缩1 dB 功率为7 dBm,二次谐波抑制比达到35 dBc。与常规宽带低噪声放大器芯片相比,二次谐波抑制比提升非常明显。