基于FPGA SoC的EtherCAT协议栈设计与实现

尹震宇,许 鹏,徐福龙

1(中国科学院 沈阳计算技术研究所, 沈阳 110168)

2(中国科学院大学,北京 100049)

3(辽宁省国产基础软硬件工控平台技术研究重点实验室, 沈阳 110168)

E-mail:xupeng181@mails.ucas.ac.cn

1 引 言

在众多工业总线中,EtherCAT凭借速度快、实时性好[1]、拓扑灵活[2]等优点得到了越来越广泛的应用.传统的EtherCAT实现主要基于PC机及普通的网卡,通过实时补丁来提高实时性,除了存在体积大功耗高等问题,还存在着实时性和稳定性得不到保证的缺点.因此近年来基于嵌入式平台的EtherCAT协议栈实现方式得到了越来越多的关注.例如,王慧娇在嵌入式平台上实现了EtherCAT主站的开发[3],高恩博则实现了在嵌入式Linux平台上的EtherCAT主站设计[4],饶阿龙在Windows平台上完成了实时EtherCAT主站开发[5].然而传统嵌入式平台性能仍然偏低,如果仍采用实时补丁的方式来实现,在系统负载较大时实时性会受到影响.因此本文提出基于FPGA SoC的EtherCAT协议栈实现方案.通过在Xilinx推出的Zynq异构平台上构建具有实时性的Linux操作系统并在FPGA上配置网络适配单元,实现在嵌入式平台上高效运行的EtherCAT协议栈,并配置可脱离系统独立工作的安全单元,实现在系统故障情况下的安全停止功能.相较于传统的EtherCAT协议栈实现方式,本文设计方案实现难度低、性能高、易于工业现场部署、运行稳定性高且成本低,并且具有安全停止功能,具有实际应用价值.

2 关键技术

2.1 EtherCAT协议

德国威尔市的倍福自动化公司于2003年推出了EtherCAT协议的实时工业以太网技术[6].该技术有3大优点,1) 具有超高的传输速率;2)能够传输超高的数据量;3) 具有高效的传输效率.自从2007年EtherCAT协议成为了ISO、IEC和SEMI三大规范标准以来,EtherCAT作为一种全新的、高效率的工业以太网技术受到业界的广泛欢迎,被EtherCAT技术协会(ETG)在欧洲、亚洲、美洲的全球大部分地区进行宣传和推广.

作为全新出现的工业以太网技术——EtherCAT协议对IEEE802.3以太网规范进行了全面的扩充,它还利用全双工的传输模式以及新提出的“on the fly”帧处理技术有效地提高了数据传输速率[7];同时EtherCAT协议在实时性和同步精度等方面的性能也有相当大的提升,已成为广受欢迎的工业以太网技术[8,9].

EtherCAT的特点如下[10]:

1)主站配置要求低:只要控制单元带有以太网控制器,无论该单元功能是否丰富、计算性能是否强大,都可以配置为EtherCAT主站,包括嵌入式平台单元和X86平台的PC系统,都可以组成EtherCAT控制系统.

2)具备以太网标准所需条件:EtherCAT协议是从以太网修改而来,其具备以太网标准需要的条件,其他以太网的设备可以与其主从站一起构成EtherCAT协议控制系统[11].

3)具有高效率:EtherCAT传输模式是全双工方式,可达到百兆的通信速率,并且还提出了“on the fly”的全新帧处理技术,可以保证高效率地传输[12,13].

4)具有高精度的同步性能:其具有超高的同步精度,同步精度可达到100纳秒.

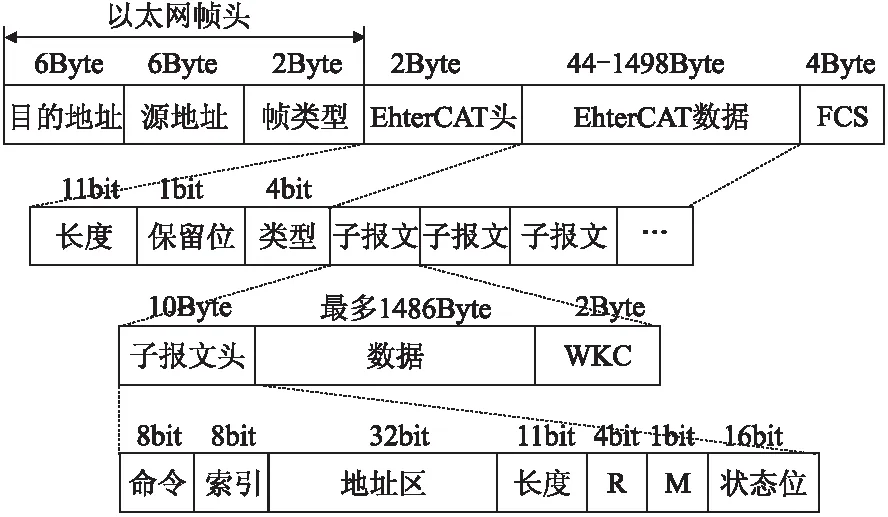

2.2 EtherCAT数据帧结构体

EtherCAT帧结构包含4大部分—以太网帧头、EtherCAT头、EtherCAT数据和FCS[14].以太网帧头占固定的14字节,其中包含6字节的目的地址和6字节的源地址以及2字节的帧类型.目的地址、源地址、帧类型均采用unsigned char数据类型.EtherCAT头总共占2字节,其中包括占位为11位的EtherCAT数据长度、占位为1位的保留位和占位为4位的类型均采用unsigned char数据类型.EtherCAT数据总共占可变的其最少占44字节,最大占1498字节,EtherCAT数据里有若干个子报文,每一个可变的子报文包含固定长度的10字节的子报文头以及可变的最多1486字节的数据和固定长度的2字节的WKC,其中可变的数据以及定长的WKC均采用unsigned char类型的数据类型. 最后是子报文头,子报文头包含8位的命令、8位的索引、32位的地址区、11位的长度、4位的保留位、1位的后续报文标志、16位的状态位,命令、索引、地址区、长度、保留位、后续报文标志、状态位均采用unsigned char作为数据类型[15],该EtherCAT帧的结构图如图1所示[10].

图1 EtherCAT数据帧结构Fig.1 EtherCAT data frame structure

2.3 EtherCAT数据帧解析

对于帧的解析,首先获取接收有效的数据帧,获取的数据帧为二进制数可以用于实现帧结构的解析过程,然后判断是否成功接收到数据帧,成功接收则对二进制的数据进行按EtherCAT帧格式位解析,之后将目的地址,源地址等转换成十六进制数,将EtherCAT数据长度、命令、子报文数据长度等转换为十进制数,最后将所有按位解析之后的结果输出,其流程图如图2所示.

图2 EtherCAT帧解析流程图Fig.2 EtherCAT frame analysis flow chart

3 EtherCAT主站软硬件设计

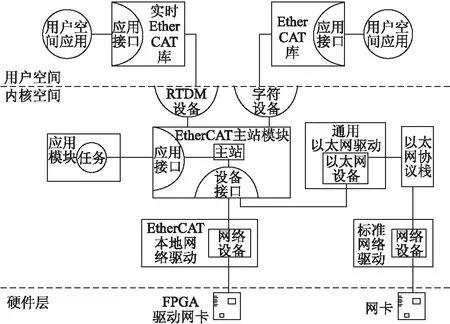

3.1 EtherCAT协议栈软件结构

EtherCAT协议栈软件结构如图3所示[16],主要由网络适配单元驱动、以太网协议的驱动及应用程序结构等构成.同时为了使平台具有更好的通用性,保留了普通网卡的驱动,使平台上原网口也可以继续实现普通以太网的功能.

图3 EtherCAT协议栈软件结构Fig.3 Software structure of EtherCAT protocol stack

3.2 Zynq平台实时系统

为了使EtherCAT协议栈能在Zynq平台上运行,首先需要在Zynq平台上构建Linux系统,并且系统需要具有实时性,来满足EtherCAT协议栈的实时性需求.Xilinx官方提供了petalinux工具来方便在Zynq平台上构建Linux,使用此工具可以很方便的完成U-boot启动、文件系统等配置,因此本文选用此工具来构建Linux系统.petalinux构建系统流程如图4所示.在使用petalinux构建系统之前,首先需要在Vivado中构建目标平台,并且生成HDF文件,方法为在Vivado中创建项目并完成IP核添加及参数配置,并创建顶层文件及添加管教约束,生成bitstream,并导出为HDF描述文件.安装petalinux工具之前,先根据提示安装所需软件包,同时根据要求修改系统配置.运行命令安装petalinux,创建工程并导入已经生成了的硬件配置信息,运行petalinux-build命令编译系统,生成U-Boot、Linux内核和RootFS镜像等文件.使用petalinux工具配置文件系统存储位置为SD卡,并将生成的镜像文件、文件系统文件等拷贝到SD卡中,设置好串口参数,将SD卡插入开发板,在串口终端工具可看到系统成功运行.

图4 Petalinux构建系统流程Fig.4 Construction process of Petalinux system

下一步进行Preempt RT补丁包的配置以使系统具有实时性,首先需要下载与内核版本相对应的版本的补丁包.Petalinux支持配置外部源码树,这使得使用petalinux配置补丁相较于传统Linux方便很多,在使用patch命令将实时补丁融入内核后,使用petalinux提供的开发工具,直接使用编译命令就可以完成内核制作,再将生成的若干文件拷贝到嵌入式平台,即可完成配置.

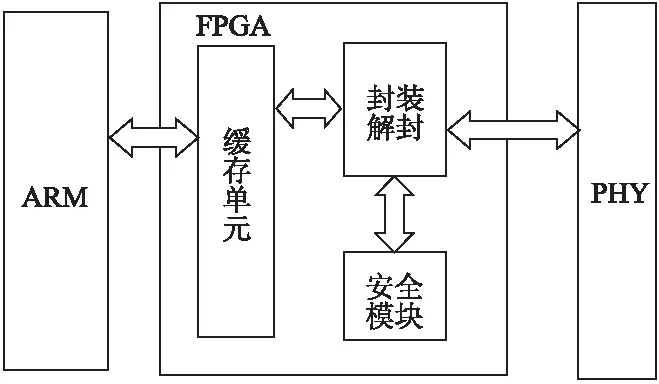

3.3 EtherCAT协议栈网络适配单元

安装实时补丁的linux操作系统的实时性虽然有了很大提升,但是操作系统可能要处理多个实时任务,并且可能存在负载过大的情况.这种情况下单纯依靠实时补丁难以满足系统的实时性需求.因此本文使用FPGA通过硬件方式配置EtherCAT协议栈的数据链路层,执行解析数据帧等工作,通过硬件方式保证系统的实时性.同时,zynq平台的PS即ARM核部分和PL即FPGA部分均可以相互独立运行,PL部分可以不依靠PS部分的指令而自行执行控制操作,因此同时在PL端配置运行安全功能,在PS端不能正常收发指令时,PL端根据实际情况发送相关命令,使伺服驱动器等设备能够安全停止,保证生产线的安全运行,减少由于系统出现问题带来的经济损失,避免生产安全事故.

图5 EtherCAT协议栈网络适配单元Fig.5 Network adaptation unit of EtherCAT protocol stack

为了通过硬件方式保证EtherCAT协议的实时性,本文将数据帧的接收、发送和解析等工作均部署在FPGA上执行.并且为了保证运行安全的相关功能够正常运行,特别是在ARM核上系统出现崩溃等情况时能够及时向伺服驱动器等设备发出停止指令,安全功能也要部署在FPGA上独立执行.具体设计如图5所示,FPGA上共配置由BRAM构成的两个独立的缓冲区作为待发送数据和接收数据的缓冲区、数据帧解析和封装单元来解析封装数据帧、数据帧收发单元来发送接收数据帧.

由于开发板底版上只配置了一个网络接口并且是与PS部分连接的,FPGA若想使用则需要将数据传输回ARM核发送,显然实时性将会受到很大影响,因此选择在FPGA上扩展口连接PHY芯片及网络接口的形式,使FPGA有独立连接的网络接口并且有能力在脱离ARM的情况下独立完成数据帧的发送和接收任务,并且在FPGA上配置数据帧收发单元,单元内包括缓冲区来存放将要发送和刚接收的数据帧.在FPGA上使用BRAM配置两个缓冲区,分别是待发送数据帧缓冲区和接收数据帧缓冲区,并且配置为FIFO.对于待发送数据帧缓冲区.数据帧封装解析单元通过AXI总线在队尾向BRAM写入待发送数据帧,而发送接收控制单元则从队头依次读出待发送数据帧进行发送.对于接受数据帧缓冲区,发送接收控制单元将接受到的数据帧存入队尾,而数据帧封装解析则从队头依次读出接受数据帧并进行处理.

3.4 安全功能单元

由当部署在ARM核上的EtherCAT无法正常工作甚至linux系统崩溃无法发送接收数据帧时,部署在FPGA上的安全功能应该能够自动运行,向外发送数据帧以实现安全停止.安全功能模块主要由计时器、安全指令存储区组成.不同厂商的伺服驱动具有不同的安全停止指令,因此本文使用BRAM配置安全指令存储区,提供给用户,用户输入指令内容存入存储区.同时在FPGA上部署定时器,当待发送数据帧缓冲区为空或接收数据帧缓冲区存满时,计时器开始工作,计数到达不同时钟周期时发送对应指令.例如,当待发送数据帧缓冲区为空,计时器开始计时,当10个时钟周期内仍没有新数据写入时,发送位置及速度归0指令,再过10个时钟周期仍没有新数据写入,则发送下使能信号.

4 实验验证

本文搭建的测试平台分别基于米联客Zynq开发板和基于国产龙芯CPU的工控单元.在开发板上对系统的实时性进行测试,以判断是否能够满足实时性要求,并且与只安装实时性补丁的实验平台进行对比,判断实时性是否有提升.在基于龙芯CPU的工控单元上使用自行开发的程序对捕获的数据帧进行分析,判断开发板发送的数据帧是否满足EtherCAT要求,同时在开发板端人工触发异常情况,包括停止发送数据帧和停止接收数据帧,通过分析工控单元接收的数据帧来判断安全功能模块是否成功发送安全指令及指令内容是否正确,验证安全功能有效性.

4.1 实时性测试

为测试平台的实时性,需要在操作系统内模拟出日常使用环境中的负载情况,主要包括大量计算、内存访问和输入输出请求.Linux操作系统本身就自带了一些工具来方便我们对这3种负载情况进行模拟,因此选用这些官方工具模拟日常负载环境,并且测试打入实时补丁的操作系统在模拟负载环境中的实时性.

首先进行日常负载的模拟.在Linux系统中,可以通过压缩随机数计的方式来模拟CPU负载,因为选定的平台为多核结构,因此模拟的指令如表1所示.

表1 CPU负载模拟代码Table 1 CPU load simulation code

对内存负载的模拟通过减少内存总量实现.通过在内存中创建文件系统并写入文件来模拟.写入文件越多,使用的内存也就越多,在写入文件足够多时就会产生页面置换来模拟页面置换的负载情况.具体实现方式为创建一个文件系统的挂载点,然后在该目录下创建文件,文件大小及块大小都可以自行定义.如创建块大小为512K、文件大小为256M的文件代码如表2.

表2 内存负载模拟代码Table 2 Memory load simulation code

对输入输出请求的模拟可以通过不停拷贝文件来实现,可以创建一个全是0的512M的文件,使用for循环执行20次操作,每次循环都拷贝新文件来覆盖旧文件.具体方式为表3所示.

表3 输入输出负载模拟代码Table 3 Input output load simulation code

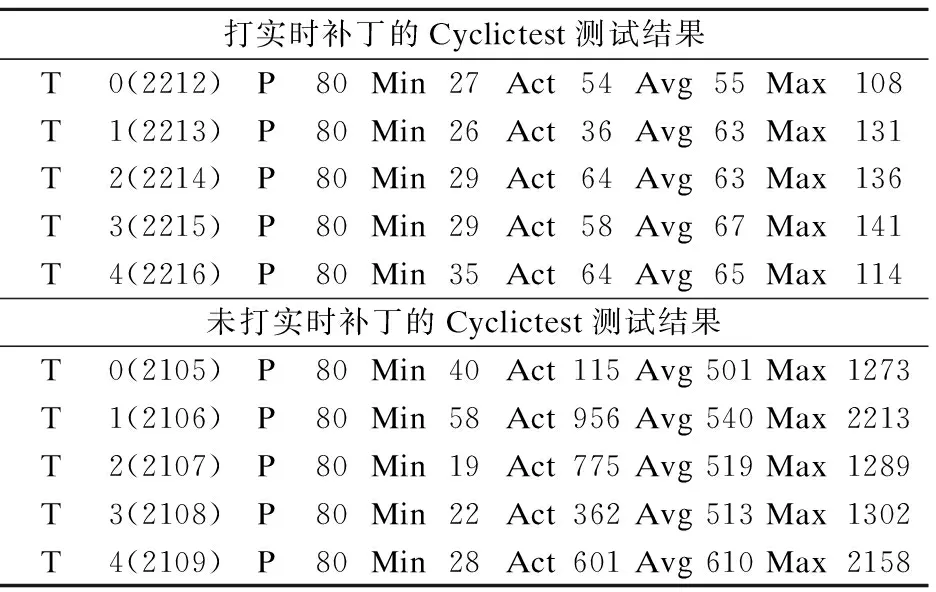

使用Cyslictest工具测试在高负载下的Linux系统的实时性能,可知平均延迟、最大延迟均有减少,相较于非实时内核,实时内核更加稳定,可以满足EtherCAT协议栈的需求.

4.2 数据帧内容测试

实时性测试结果对比如表4所示.在测试实时性之后还要对协议栈发送的数据帧内容进行测试,以确保协议栈的正常运行.测试平台选用实验室开发的基于龙芯的工控单元,单元具有测试数据帧内容功能,可解析数据帧的内容.测试结果如图6,可以看到数据帧内容正确.

表4 实时性测试结果对比Table 4 Comparison of real time test results

图6 数据帧内容测试结果Fig.6 Data frame content test result

4.3 安全功能测试

为测试实验平台的安全功能,需要人为触发异常情况,可以通过在操作系统内强行停止协议栈发送和接收数据帧,来触发FPGA上的安全功能单元,来判断安全功能是否正常运行.因为不同厂商的伺服驱动器指令各不相同,为了对安全功能进行验证,我们设定数据第13、14位分别为使能信号和抱闸信号,对数据帧解析并查看13、14位情况来验证功能正确性.如图7、图8为测试结果,可以看到工控单元依次收到了下使能、抱闸的信号,因此可以验证安全功能可以正常运行.

图7 安全功能数据帧测试结果1Fig.7 Security function data frame test result 1

图8 安全功能数据帧测试结果2Fig.8 Security function data frame test result 2

5 结束语

本文详细的介绍了EtherCAT协议栈特点、数据帧结构及解析数据帧的过程,提出了一种基于FPGA SoC的EtherCAT协议栈实现方案,通过在FPGA上部署网络适配单元,同时加入安全功能单元,实现了EtherCAT协议栈在嵌入式平台上的高效运行,经过实验测试,平台具有良好的稳定性,数据帧内容正确,安全功能可以正常运行,具有很强的实用性和应用价值.