基于HDL的北斗B1C信号Weil码产生方法

赵丙风,孙寿浩,谭志强,何健

1.中国电子科技集团公司第五十四研究所,河北,石家庄,050081;2.电子信息系统复杂电磁环境效应国家重点实验室,河南,洛阳,471001;3.光电对抗测试评估技术重点实验室,河南,洛阳,471023

0 引言

卫星导航系统绝大多数都是一个基于码分多址(CDMA)的直接序列扩频通信系统,早期的卫星导航信号伪随机码多为Gold序列或者m序列;Gold序列应用于北斗B1I /B3I信号、GPS L1CA/L5C信号、Galileo E5a/E5b信号等,m序列主要用于频分多址的GLONASS G1信号[1]。进入21世纪,主要卫星导航系统加速了各自的GNSS现代化进程,其中GPS增加了基于Weil码L1C信号,北斗系统中增加了基于Weil码的B1C信号[2]。

Weil码具有码长为质数的优点,在不接近2n的指定码长约束下,易于通过截短或增补实现较好地维持原伪码的相关性能,降低寻码的复杂度[3]。同时,研究表明Weil码的奇偶自相关最大旁瓣相关值相对于Gold码更小,Weil码的自相关结果方差也更小,幅度和变化范围更接近,而Wei码的奇偶互相关与Gold码相差很小,也表明了Weil码具有更好的相关性能[4],以及更好的抗干扰性能[5]。

Weil码是将两个勒让德序列进行异或得到的,而B1C信号通过对Weil码进行循环截取的方式得到了合适长度的伪随机序列[2]。由于勒让德序列的特殊性,在现场可编程逻辑门阵列(FPGA)或者专用集成电路(ASIC)实现中,很难直接产生所需的勒让德序列或者Weil码。FPGA实现中常通过软件生成所有信号的Weil码,并将Weil码写入RAM中存储,信号接收过程中直接读取RAM中存储的伪码;另一种方式是通过多端口ROM存储勒让德序列,使用时读取ROM中的勒让德序列计算对应的Weil码[4][5]。

但是在ASIC中,ROM都是单读取端口,只能通过多个ROM块实现多端口ROM;此外,ASIC中RAM的面积是同等容量ROM的4倍以上,即现有的Weil码生成方式在ASIC实现时会消耗较多的资源与实现面积。针对以上问题,本文设计了一种基于单端口ROM多次读取的Weil码产生方法,完成了基于FPGA的原型平台实现与验证,并将该方法成功应用到ASIC设计中。

1 Weil产生算法

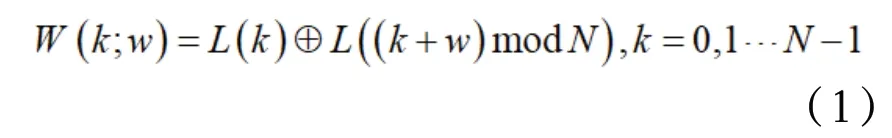

B1C信号包含了导频和数据两个支路,其中数据支路包含了扩频主码与电文信息,导频支路包含了扩频主码和子码。导航和数据支路的主码均由Weil码截断产生,长度为N的Weil码的定义为[2]:

式中,mod表示取模运算;w为产生Weil码所需的两个勒让德序列相位差;L(k)为长度为N的勒让德序列,其定义如下:

通过对长度为N的Weil码循环截取,就能够得到如下的长度为N0的B1C信号数据或者导频支路的主码序列:

式中,p就是所选的Weil码的截取位置;w为产生Weil码的勒让德序列相位差。

B1C信号共设计了126个主码序列,每个主码的截取位置p和相位差w不相同,详细数据可以参考B1C信号的接口控制文件(ICD);B1C信号的数据支路和导频支路各有63个主码,对应于北斗三号系统支持的63颗卫星。B1C主码速率为1.023Mcps,长度N0为10230,由长度N为10243的Weil码截断产生。

2 已有实现方案

由于勒让德序列的计算方法涉及二次剩余理论,不易于通过HDL语言完成对应的产生算法设计,无法直接在FPGA或者ASIC中通过计算产生,因此当前导航接收机中主要通过单读写端口RAM或者双读取端口ROM存储的方式实现基于Weil码的导航信号接收处理。

2.1 单端口RAM方案

RAM存储的实现方式可以使用单端口读写RAM,为了节省RAM的资源,会根据B1C信号的接收通道数量设计使用的RAM数量。因为同一卫星播发的B1C信号的数据支路和导频支路是时间对齐的,而不同卫星的之间的延迟是不固定的,所以需要每个B1C信号接收通道对应一个RAM存储器。Weil产生框图如图1所示。

图1 基于单端口RAM存储的Weil产生框图

图1中工作时钟fs即为接收机信号接收通道工作时钟;DDS为接收通道中的伪码NCO,用于产生接收信号主码的提取脉冲,频率为fc;软件写控制接口根据软件指令将软件产生的B1C信号数据和导频主码存储到对应地址的RAM中;本地码发生控制器用于产生当前需要的数据和导频主码读取地址;读写控制器在软件控制下实现RAM数据的读写切换。

该方案中,每个接收通道中需要存储的数据量为10230*2=20460kbits,实际由于RAM资源的特殊性,其读写地址均为2的整次幂,所以实际的RAM大小为16384*2=32768bits,即32kbits。

2.2 双端口ROM方案

RAM实现方案除了存储资源的消耗外,还占用了软件的计算资源和总线资源,所以后续提出了基于ROM存储勒让德序列,通过多端口读取来实时计算Weil码产生B1C主码的方案[4][5],如图2所示。

图2中工作时钟fs即为接收机信号接收通道工作时钟;DDS为接收通道中的伪码NCO,用于产生接收信号主码的提取脉冲,频率为fc;通过双端口同时读取ROM中0相位和w相位的勒让德序列,然后经过异或和循环截断得到所需的Weil码。

图2 基于双端口ROM存储的Weil产生框图

该方案中,ROM存储的数据为长度为10243的勒让德序列,实际存数长度为16384bits。因为每一个ROM仅能产生一个Weil序列,所以每一个跟踪通道需要两个ROM,总的待存储数据量与RAM方案相同。相比于RAM方案,ROM存储方案在消耗资源不变的情况下,大大减少了软件的计算量。

在ASIC实现中,同等容量的RAM资源占用面积是ROM的4倍以上,所以ASIC设计中采用ROM的存储方案更具有优势。同时因为ROM资源的特殊性,双端口ROM只能用两个相同的ROM块实现,也就是说,按照现有ROM方案,每个B1C接收通道需要4个相同容量的ROM块才能实现同时产生数据和导频主码。

3 单端口ROM方案

3.1 工作原理

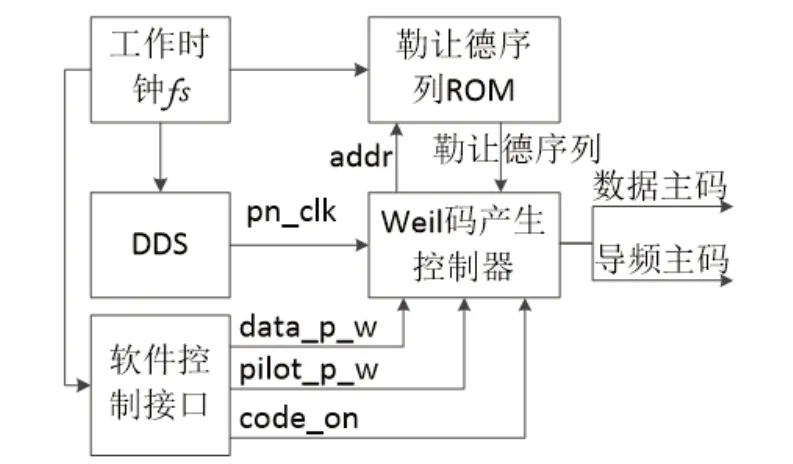

因为导航接收通道的工作时钟fs一般远高于导航信号伪码速率fc,所以可以利用fs的时钟速率,多次读取单端口ROM的方案,通过顺序计算得到所需的B1C信号数据和导频主码。实现方案的框图如图3所示。

图3 基于单端口ROM存储的Weil产生框图

勒让德序列的存储ROM以通道时钟fs进行读取;接收通道内置DDS基于工作时钟fs产生频率为fc的主码提取脉冲pn_clk;软件控制接口根据软件设置将本通道对应的数据和导频主码对应的截取位置p和相位差w写入到Weil码产生控制器中,同时根据开通道的需求配置Weil码产生控制器工作使能信号code_on;Weil码产生控制器根据使能信号code_on确定其是否工作,在每个pn_clk脉冲后,以时钟速率fs完成4次对应的ROM序列读取,然后将读取到的结果依次完成异或运算得到对应的数据和导频主码。

3.2 实现方案

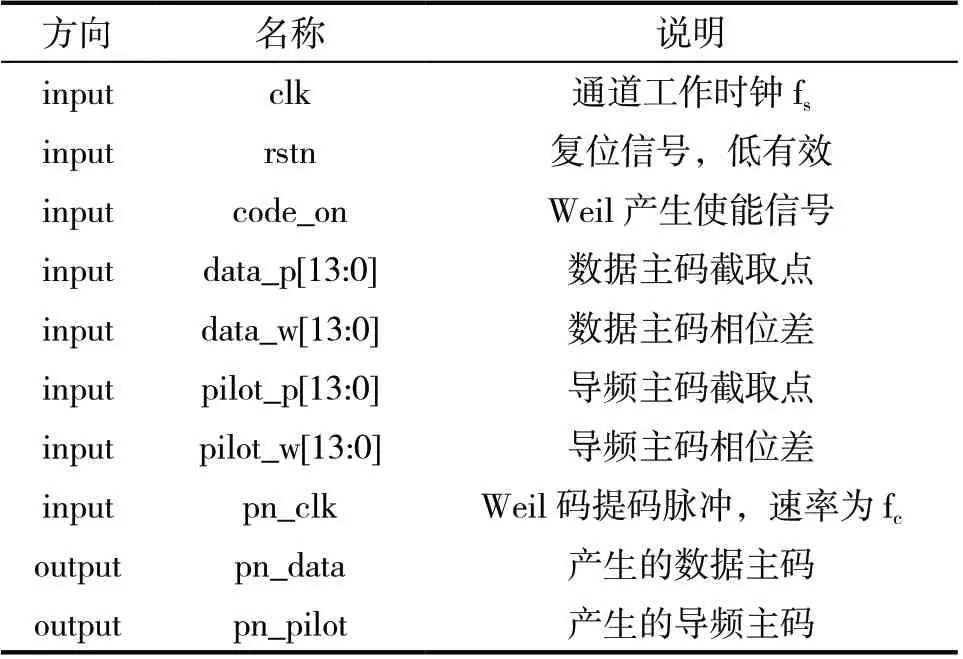

Weil码产生控制器的端口信息如表1所示。Weil码产生控制器的内部工作时序如图4所示。

表1 Weil码产生控制器端口说明

图4 Weil码产生控制器内部工作时序

Weil码产生控制器的工作流程如下。

(1)软件启动某个卫星的Weil码产生,配置卫星对应的数据和导频主码对应的相位截取点和相位差,设置code_on信号为1,启动对应通道的Weil码产生使能。

(2)Weil码产生控制器检测到code_on信号的上升沿,触发第一个Weil码产生使能信号gen_en,后续每输入一个提码脉冲pn_clk,产生一个对应的gen_en信号。

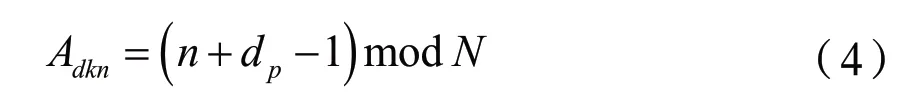

(3)每个gen_en信号触发rom_addr信号计算,依照速率fs依次完成四个读取地址计算,分别是:

式中,n的取值范围是0~10229,表示第n个主码;N的取值为10243,为勒让德序列长度;dp和dw为导频主码相位截取位置和相位差取值;pp和pw为导频主码相位截取位置和相位差取值。

(4)根据ROM读取输出,依次将第n个数据和导频主码计算所需的勒让德序列Ldkn、Ldkwn、Lpkn、Lpkwn存储至本地寄存器data_lk、data_lkw、pilot_lk、pilot_lkw。

(5)在ROM读取完成,依据存储的勒让德序列计算并输出第n个数据和导频主码,计算过程如下:

需要说明的是:

(1)Weil码产生控制器在使能信号code_on置位后,即开始计算第一对数据和导频主码,这与接收通道中通道接收开始后立即进行相关的需求相符,只要保证在接收通道开启前完成Weil码产生控制器的配置,即可保证信号接收启动后有码可用;

(2)后续每个提码脉冲pn_clk有效后,有效的伪码在延迟9个clk后输出,因此在接收通道开启时需要合理控制开启时刻,保证接收用伪码的相位正确性;

(3)每对数据和导频主码输出在时间上是严格对齐的,这与实际使用需求相符。

4 实施效果

基于ASIC原型验证平台(核心器件为Xilinx Zynq UltraScale+的XCZU19EG),利用软件工具Vivado 2018.3,对本文提出的基于HDL的北斗B1C信号Weil码产生方法进行了验证,完成了B1C信号的接收测试,并利用Vivado自带的集成逻辑分析仪(ILA),采集了24号卫星的数据和导频主码信号产生的结果,如图5所示。

图5 B1C信号24号星数据和导频主码产生结果

文献[2]中给出了B1C信号24号星数据主码前/后24个伪码取值为77312776/56550366(八进制),导频主码前/后24个伪码取值为10544206/54230354(八进制),确认了本文提出的方法可以正确产生对应的B1C信号数据和导频主码。

5 结语

本文研究了基于HDL的北斗B1C信号Weil码产生方法,使用单端口ROM存储勒让德序列,通过高速时钟顺序读取四次ROM,产生B1C信号接收所需的数据和导频主码,解决了在ASIC实现中Weil码的存储器面积消耗过大的问题,并经过原型接收机的验证Weil码产生的正确性。实验证明,本文研究的Weil码发生方法适用于基于FPGA的导航接收机,也适用于导航芯片设计。