基于STM32的LVDS数据传输系统

朱静 蔡昌勇

摘要:数据在高速传输时会出现信号误码风险、EMC风险、信号串扰衰减和失真问题,而LVDS低压差分信号,可减少上述风险,提高数据传输的距离与可靠性。针对以上问题,本文设计了一种基于STM32和LVDS的数据传输系统,读取TTL并行数据并转换成串行数据,输出给LVDS电平转换电路转换为LVDS信号经过LVDS传输线缆进行传输。然后接收端接收LVDS信号转换为串行TTL电平,由单片机转换为并行数据输出,借助LVDS可完成信号的高速传输。经过实验验证,信号传输没有明显的失真和衰减,信号传输速率较高。

关键词:低压差分传输技术;嵌入式系统;高速信号传输;STM32

中图分类号:TP391 文献标识码:A

文章编号:1009-3044(2022)14-0025-03

开放科学(资源服务)标识码(OSID):

随着计算机技术和微电子技术发展,人们对数据的传输速率要求越来越高,于是传统的TTL电平和CMOS电平由于其相对较低的传输带宽和可靠性,已经不能满足高速数字信号传输的要求。为此,在目前常见的高速传输协议(如USB、HDMI、DP)中都采用差分信号传输[1]。低压差分信号传输技术LVDS(Low Voltage Differential Signaling)也是一种常见的差分数字信号传输方案,其广泛用于视频信号传输中,是一种成熟可靠的高速信号传输方案[2]。

在电子设备中经常需要使用较长的导线传输数字信号,由于走线较长,导致传输线的阻抗增大,从而导致信号衰减,增大信号误码风险,EMC风险也会提高,信号串扰衰减和失真问题也会更恶劣[3]。而LVDS技术由于其为低压差分信号,减少了由衰减引起的误码问题,由于差分对两线之间信号反相,减少了差模信号辐射,很好地抑制了串扰风险,并且由于差分信号较高,共模抑制比的特性降低EMC风险[4]。

将传统的TTL并行信号转换为LVDS串行信号传输,可以减小因传输时延造成的误码,减少传输线线束数量,提高稳定性和传输速率。在数据量较大、传输距离较长的使用场景下,用LVDS代替一些TTL或CMOS电平传输的数字通信接口,提高设备性能和可靠性。本文利用STM32设计了一种基于LVDS的数据传输系统,实现TTL与LVDS电平的互相转换,数据可通过LVDS进行高速传输。

1 系统总体设计

本系统读取TTL并行数据并转换成串行数据,输出给LVDS电平转换电路转换为LVDS信号,经过LVDS传输线缆进行传输。然后接收端接收LVDS信号,转换为串行TTL电平,由单片机转换为并行数据输出,借助LVDS可完成信号的高速传输。

2 硬件电路设计

2.1 信号读取转换电路

信号读取转换电路具有TTL并行逻辑时序读取、数据缓存、串行逻辑时序产生三个主要功能。要实现以上功能大致有两种备选方案,一种是完全由数字逻辑电路实现以上功能,数字逻辑电路具有实时性高、运行效率高、数据传输速率高等优点。数字逻辑电路可以选用分立的逻辑器件搭建,也可以选用现场可编程逻辑门阵列(FPGA)。如果选用FPGA可以方便调试,遇到逻辑问题可以马上更改,FPGA系统时钟一般在200MHz以上,假设每个字节串行信号发送需要200个时钟周期,理论上数据传输速率可以达到1Mbyte/s[5]。FPGA是一种比较昂贵的元器件,而MCU方案成本较低,方便调试,可以使用SWD接口进行在线调试,实时读取内存中的数据,MCU逻辑处理能力相比一般的单片机要高出很多,I/O口读写速度较快,满足本系统需求[6]。最终选择了意法半导体(ST)生产的STM32F103C8,原理图如下所示。

电路包括MCU、时钟电路、复位电路、电源电路、下载调试电路、串口电路以及并行接口电路。电路工作电压为3.3V,并行接口电路,包含一路时钟信号和8位并行信号。在信号通路上添加一个22R电阻,限制信号通路上的电流大小,在一定程度上保护了MCU的I/O口,并且此电阻还可作为端接匹配电阻,当信号波形出现振铃或其他因为阻抗匹配问题时,可以修改此电阻大小实现阻抗匹配。调试过程中还可以通过取下这一电阻断开某一连接。

2.2 电平转换电路

MCU读取并行信号后,将读取到的信号转换成串行信号,信号传输到电平转换电路后,将MCU发出的TTL串行信号转换成LVDS串行信号再发出,接收端收到LVDS信号后,需要将LVDS信号,转换成TTL信号,发送给接收端MCU读取。电平转换电路基于SN65LVDM176D LVDS收发芯片实现,芯片中集成了接收与发送两种模式,可以实现改变电路元器件设置电路工作模式。由此发送端和接收端可以使用同一PCB,通过不同的焊接方式实现发送或接收功能。通过设置芯片的2脚和3脚两个脚的高低电平,即可设置工作模式,如果是发送端电路,则焊接R5和R7两个电阻,如果是接收端,则焊接R1和R2两个电阻。

SN65LVDM176D芯片与一般LVDS芯片结构有所不同,此芯片输出负载为50Ω,输出端和输入端各需要一个100Ω电阻。LVDS接口和传输线需要有屏蔽层,保证信号传输过程中不受干擾,屏蔽层还能提供信号回流路径,让整个传输回路阻抗连续。差分信号需要使用双绞线传输,选择传输线时需要注意传输线是否双绞线。

3 软件设计

3.1 TTL并行信号时序软件实现

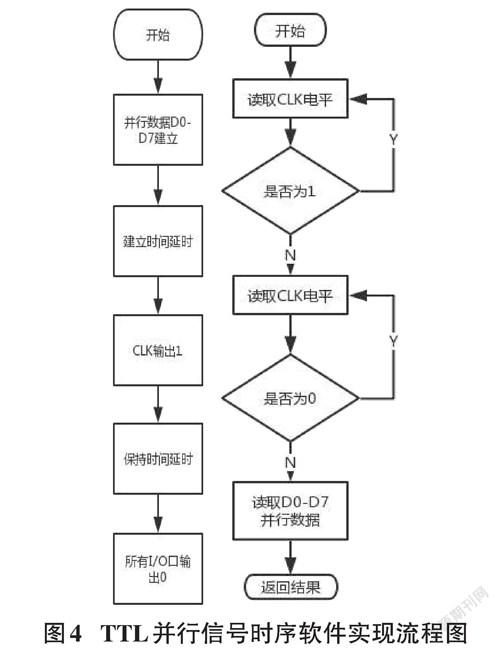

本系统输入信号为TTL并行信号,读取并行信号需要按照一定时序进行读取,在设计软件时需要设计并行数据收发时序。硬件设计的并行接口中包括一路时钟线和8路信号线,在每个时钟上升沿时读取8路数据线上的并行数据。A770A41B-28F9-47F0-8DC2-DE44C06F6493

在实际传输过程中,如果并行信号还没有完全建立时钟线就置1,接收端检测到上升沿后,读取到未建立完成的并行信号,读到的数据可能会是错误的,所以在软件设计的时,需要设计合适的建立时间。如果建立时间太短,会影响数据传输准确率,建立时间太长,会降低传输速率。合适的建立时间只有在软件实际调试的时才能确定,需要在软件调试的时多次尝试,从而确定在不影响传输准确性前提下的最小建立时间。

并口发送软件主要内容是先设置I/O口D0~D7输出,需要发送的8位并行数据,软件延时适当时间作为建立时间,再将CLK设置1,输出上升沿,最后再延时一段时间后CLK设置为0,完成一次并行数据发送。接收软件开始运行后,先等待CLK为0,然后等待CLK拉高,即CLK输出上升沿,然后读取D0~D7并行数据,最后返回读取的数据。

3.2 TTL串行数据时序软件实现方案

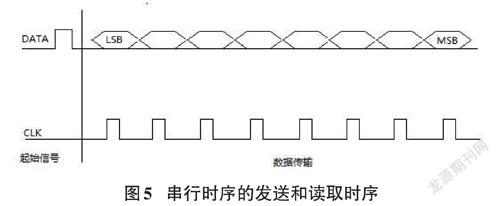

软件读取到并行数据输入后,需要将读取到的数据转换成串行数据发送,软件设计时需要设计串行发送时序,并且用程序实现串行时序的发送和读取。每个数据需要有一个起始信号,接收端通过检测起始信号判断是否开始读取数据。起始信号之后每一CLK上升沿时,DATA高低电平代表1bit数据,数据发送顺序是从最低有效位(LSB)开始发送,以最高有效位(MSB)结束。

发送端软件先将DATA置1延时一段时间再拉低,延时时间不能太短,太短接收端将检测不到起始信号,然后循环发送每一位数据。串行信号发送也存在建立时间,发送每1bit数据都要先将DATA置位,然后延时一定时间再将CLK置1。

接收端软件先等待DATA为低电平,再等待DATA置1,此时检测到起始信号,然后循环读取串行数据每一位并保存,最后函数返回读取到的串行数据。

4 系统验证

将发射电路、接收电路、STM32最小系统共同构成调试系统,STM32最小系统作为并行信号发生器。将最小系统与发送端电路的并行接口,发送端电路与接收端电路通过LVDS接口通信,用一根SCSI-14连接线连接两电路板的SCSI-14端口。

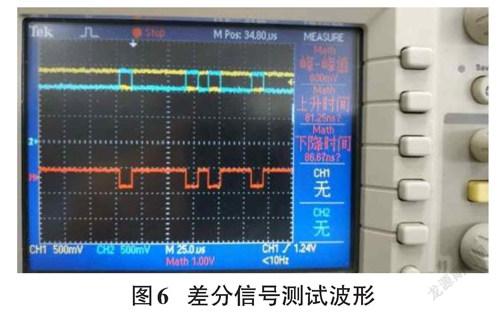

电平转换电路输入信号为TTL电平,给电平转换电路输入方波,如果电路正常工作,接收端100Ω电阻两端信号幅度应该为350mV左右。在发送端电路SN65LVDM176D芯片4脚输入峰值为3.3V,最小值为0V的方波,连接好SCSI-14传输线,用示波器测试接收端电路SN65LVDM176D芯片6、7引脚。测得LVDS信号峰值VP-P为800mV,幅度为[VP-P2] = 400mV。测试结果属于官方数据手册中的幅度范围,电路工作正常。最后测试SN65LVDM176D芯片1脚连接的22Ω电阻远离芯片一侧的TTL信号,确认信号没有失真,可以进行系统联合测试。

发送端和接收端分别烧录测试模式软件开始测试,用示波器两通道测试接收端LVDS差分信号D-和D+,并且将示波器设置为math->ch1-ch2模式,并测试math通道上升时间、下降时间、幅度。测得差分信号测试波形如图6所示。由测量结果可以计算本系统硬件最大支持的时钟频率为1/(10×RT)= 1.23MHz。再分别用示波器两个通道测试接收端由LVDS转换的TTL电平DATA与CLK波形,测量传输1byte数据所需时间,由测试结果可得传输周期为171.0us。

经过测试,在系统工作频率下LVDS和TTL信号都没有明显的失真和衰减,如果需要更高的传输速率,需要使用更高级的处理器作为逻辑转换单元。

5 总结

本文分别从LVDS数据传输系统的总体设计、硬件设计、软件设计与系统测试方面进行了描述,基于STM32与SN65LVDM176D设计了一套基于LVDS的数据传输系统。结合软硬件联合测试结果,在系统工作频率下LVDS和TTL信号都没有明显的失真和衰减,为数据的高速传输提供了一种灵活可靠、可移植性强的方案。

参考文献:

[1] 熊光阳.基于FPGA的高速图像传输系统设计[D].桂林:桂林电子科技大学,2020.

[2] 谢詹奇.高速LVDS收发器的研究与设计[D].上海:上海交通大学,2008.

[3] 鄢玲玲,文丰,李辉景.一种基于LVDS高速传输的接口优化设计[J].电测与仪表,2016,53(20):80-83.

[4] 薛栋,李杰,张德彪,等.基于LVDS的高速数据回读系统设计[J].中北大学学报(自然科学版),2021,42(2):135-139.

[5] 张波,李杰,张海鹏,等.基于FPGA的LVDS传输链路的可靠性设计[J].电子器件,2018,41(5):1237-1241.

[6] 罗瑶,魏忠义,朱磊,等.STM32CubeMX的高速USB通信模塊设计[J].单片机与嵌入式系统应用,2017,17(9):46-48,54.

收稿日期:2021-12-30

基金项目:本文得到了四川省教育厅科研项目(编号:17ZB0038)资助

作者简介:朱静(1987—),通信作者,男,主要研究方向为电子技术、机器学习;蔡昌勇(1980—),男,研究方向为嵌入式技术。A770A41B-28F9-47F0-8DC2-DE44C06F6493