用于像素阵列扫描控制的低功耗RISCV 处理器

方 倪,徐德利,王 东,沈 凡,龚 祺

(华中师范大学物理科学与技术学院像素实验室,湖北武汉 430079)

随着集成电路技术的快速发展,复杂电路的集成变得可行。高能物理实验中依托于CMOS 像素传感器,像素传感器最重要的指标之一就是像素分辨率,提高像素分辨率可增加高能物理中发现新粒子的概率,因此大阵列CMOS 像素传感器具有极其重要的应用价值[1]。目前国内对于大阵列的拼接主要利用精密压电陶瓷电机完成探测器位置调整,并通过激光测距仪测量以及计算机平面拟合来确定探测器的空间位置,进而实现大规模非连续CMOS 焦平面阵列的机械式拼接[2-3]。大阵列的读出结构主要采用Global shutter[4]、rolling shutter[5]、AERD (Address Encode and Reset Decode)[6]等方式。利用机械方式的拼接可以解决大阵列问题,但是同时也会带来外部连接的问题,阵列读出方式的选择也是该类芯片需要研究的关键问题。文中设计利用开源的RISCV 处理器构建一个可重构的数字读出系统来克服这些问题,通过外部的配置进行读出方式的选择,通过外部接口的设计进行多处理器之间的级联,实现大阵列像素的读出,提高了系统兼容性。

1 系统结构

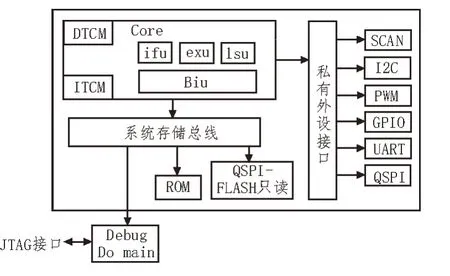

像素阵列扫描控制器主要由3 个部分构成:核心模块、通信接口和像素扫描阵列;核心模块搭载国内开源的RISCV 内核,主要任务是协调各个模块之间正常运转;通信接口主要采用JTAG 接口,利用JTAG 既可以完成核的烧录也可以形成菊花链结构级联多核;像素扫描阵列实现常用的扫描方式及Global shutter &rolling shutter,能够实现两个模式的切换、更改扫描的分辨率以及针对某一指定区域进行扫描。像素阵列扫描控制器的结构示意图如图1所示。

图1 像素阵列扫描控制器的结构示意图

2 系统各个模块的设计

2.1 开源RISCV内核

RISCV 架构主要由美国加州大学伯克利分校于2010年发明[7]。文中设计的内核基于国内开源RISCV处理器——蜂鸟E203[8],内核设计遵循模块化的原则,将处理器划分成4个主体模块单元,分别为系统存储、外设部分、程序Debug 烧录部分以及处理器core。系统存储主要分为ITCM(Instruction Tightly Coulped Memory)、DTCM(Data Tightly Coulped Memory)以及通过QSPI 接口外接其他片外存储;外设部分主要包含了IIC、SPI、UART、GPIO、PWM 和Watch Dog;程序Debug 烧录部分主要通过JTAG 进行实现;处理器core 为处理器核的所有逻辑部分。处理器的内部模块层次划分如图2 所示。

图2 处理器的模块层次划分

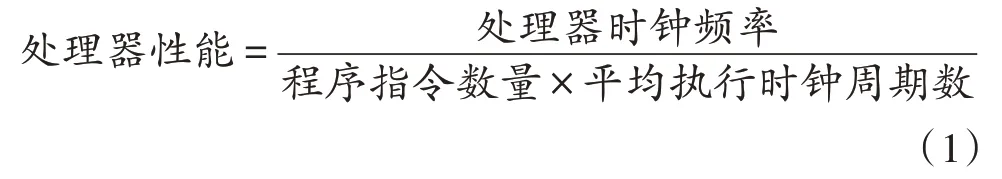

内核采用RV32IMAC 架构,支持32 位通用指令集,兼容16 位压缩指令集以及多周期硬件乘除法单元。RISCV 指令集如表1 所示(仅展示该设计用到的指令集)。原蜂鸟E203 处理器采用深度二级流水线设计,处理器中采用流水线的作用是提升系统整体的运行速度,流水线的本质就是利用面积换取系统性能。微处理器性能的决定因素根据下式[9]体现:

表1 RISCV指令集

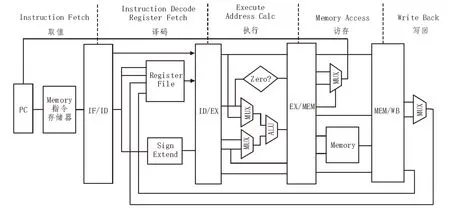

处理器时钟频率主要根据时序电路之间的最大组合逻辑延时得到,流水线是将单周期长的组合逻辑的操作分成多个组合逻辑实现,计算组合逻辑中最大的延时就是当前处理器的时钟频率,由此可以减少时序电路之间的组合逻辑,但带来了寄存器数量的增加,也就是使用D 触发器的数量变多,从而导致系统的面积随之增加。文中设计综合考虑面积和性能,选择经典五级流水线的结构,将取值(IFU)、译码(ID)、执行(EXU)、访存(MEM)、写回(WB)各自作为一级,其流水线结构如图3 所示。

图3 处理器流水线结构

对于处理器而言,不仅仅需要关注性能,还需要关注整体的功耗,该处理器低功耗[10]的设计主要从以下两个方面进行考虑:第一,采用不同的时钟域,速度要求不高的模块放在低时钟域下,以低功耗运行,该处理器分为3 个时钟域,具体如表2 所示;第二,内部单元配备独立的门控时钟(Clock Gate)[11],当该模块或者单元空闲时,使用门控时钟的合理关断来节省动态功耗[12]。

表2 处理器的时钟域

2.2 通信接口设计

通信接口用于实现处理器程序的更新以及多核之间的连接,采用的是JTAG 接口,开源蜂鸟E203 内部采用JTAG 接口进行程序烧录,利用JTAG 支持菊花链[13]的连接模式,从而可以拓展成多核之间的连接。JTAG 接口内部主要由TAP(状态控制器)、数据寄存器、指令寄存器、旁路寄存器以及移位寄存器五部分构成。文中设计采用标准四线接口:TMS(测试模式选择)、TCK(测试时钟输入)、TDI(测试数据输入)、TDO(测试数据输出)[14]。时钟通过TCK 引脚输入,驱动内部时序逻辑运转,通过时钟的上升沿采集TMS 的信号变化,从而改变内部TAP 状态机的变化。测试数据从TDI 引脚输入,输入的是指令和数据,最终通过移位寄存器将数据通过TDO 引脚输出。JTAG 内部TAP 状态转移图如图4 所示。JTAG接口不仅实现对处理器的程序烧录和Debug 操作,还可以起到多核之间的连接作用,采用菊花链的连接模式,通过JTAG 的内部Bypass 透传指令将前一级的数据直接送入到下一级,形成多核之间首尾相接的形式。JTAG 的菊花链连接结构如图5 所示。

图4 TAP状态转移图

图5 菊花链连接结构

2.3 像素扫描接口设计

对像素探测器而言,能够正确有效地得到当前粒子的信息是比较关键的,这就需要依托于设计中的读出系统是否设计合理,目前相机常见的阵列扫描采用的是Global shutter&rolling shutter方式[15]。传统方法通过数字流程设计制作出某一种读出方式,然后集成到像素芯片上,这样就固定了扫描方式,不利于芯片后期的测试以及修改。为了能够兼容多种读出方式,给处理器增加了一个像素扫描外设模块,该模块接口管脚的定义如图6 所示。该模块主要实现了3种功能:第一,实现Global shutter&rolling shutter,并且可以实现两种模式的切换;第二,实现Global shutter &rolling shutter 模式之间对于像素分辨率的切换;第三,实现Global shutter &rolling shutter 模式下对指定像素区域进行扫描。

图6 像素接口设计

3 设计结果

文中处理器开发的软件平台采用Ubuntu16.04系统,硬件开发语言采用Verilog HDL,硬件平台选用Xilinx Artix-35T FPGA 开发板[16],仿真测试工具采用Vivado 以及VCS 软件。

整个验证过程主要分为以下两个步骤:首先对处理器、像素扫描模块以及JTAG 多核级联等模块进行功能仿真,查看仿真波形结果与理论结果是否一致;第二步将整体模块通过Vivado 工具编译综合,将生成的.bit文件烧录到FPGA 开发板中进行硬件测试。

首先对每个模块进行前期功能验证,主要通过编写testbench输入正确的激励得到输出波形,最后比较结果的正确性。处理器的仿真激励通过对内部的ITCM进行写操作,将需要测试的指令通过编译器转换成机械码相当于对ITCM的某些地址写入对应的数据。

测试的指令为ADD 指令,通过编译器将编写好的C 代码转化成ROM 可读的机器码文件,如测试仿真代码中的rv32ui-p-addi.verilog 文件,使用Verilog的readmemh 函数读入文件,初始化ITCM,由Verilog编写的二维数组充当行为模型。最终测试结果如图7 所示。从仿真结果中可以看出,写入到ITCM 中的数据与最终对ITCM 进行读出的数据是一致的,最终数据正确后写回寄存器X3,X3 为“1”则通过仿真检验,最终打印出PASS 结果;否则测试结果有误,打印出Fail字样。

图7 处理器仿真测试结果

测试文件中ITCM 寄存器地址为0x00,需要写入的数据为16′h3405107 30001AA0D,通过仿真控制模块内核查看ITCM 的信号结果,指令地址addr=0000 的数据dout 为34051073_0001AA 0D,符合最终的设计结果。

为了进一步验证该处理器的可行性,进行FPGA原型验证。将模块通过Vivado 工具进行编译综合,生成bitstream 文件,利用开发板进行硬件验证。通过JTAG 调试器将数据送入开发板的Memory 中,然后利用GCC工具链对写好的C程序进行编译,将编译好的程序下载到开发板中,通过串口看出最终的输出结果。以经典的“Hello world”程序为例,对于编写好的C程序,为了更直观地看到其结果,在C中调用串口。以PC端为接收器,配置好对应串口ttyUSB2 以及波特率115 200 bit/s。通过PC 端调用串口指定显示当前串口号下的信息,最终的运行结果如图8所示[17]。

图8 硬件测试结果

目前该系统已经设计完成,正准备进行流片工作,前期针对RISCV 内核进行了一次流片,采用的是商用130 nm CMOS 工艺,主要修改内容是将内部的IP 替换成工厂提供的IP 核。

将芯片进行绑定测试,键合到印制电路板(PCB),焊接后进行测试,测试平台如图9 所示。芯片的外部输入由FPGA 板提供,通过查看信号源以及Vivado硬件仿真波形验证芯片功能。

图9 芯片测试平台

4 结论

文中提出了一种可重构的数字读出系统,主要应用于高能物理像素探测器中,该系统能够兼容多种像素读出方式,并且通过外部接口进行多核连接和多核之间的通信。该内核已经采用商用130 nm CMOS 工艺设计完成,处理器在40 MHz 的频率下静态功耗为5.221 2 mW,动态功耗为53.024 9 mW。