一种小尺寸硅基LED驱动设计

陈文明

(1.中航华东光电有限公司,安徽芜湖 241002;2.特种显示技术国家工程实验室,安徽芜湖 241002)

0 引言

硅基LED是将MicroLED 阵列和硅基背板通过特殊的工艺连接在一起,并能够显示图像的显示设备,由于受到硅基工艺的限制,物理尺寸一般在1"以下。其具有极高的发光亮度、分辨率和对比度,而且响应时间极短。由于硅基LED 是全固态的显示器,还具有工作温度范围宽、抗震性好等优点。随着可穿戴设备的快速发展,作为图像源的硅基LED 受到人们越来越多的关注[1-3]。由于穿戴设备被人们戴在头部,所以对重量、功耗、显示效果、亮度能指标有非常高的要求。硅基LED 的驱动是直接影响其显示效果以及其性能能否充分发挥的关键因素,所以需要对其驱动方式和驱动电路进行研究,以便在产品应用中取得良好效果。常规的硅基LED 驱动方式的研究,仅仅研究了驱动的实现,重点关注屏的点亮方式,并没有过多地关注产品上的工程实现问题。本文以实际的一款硅基LED 显示屏的驱动设计为研究,对产品工程实现中的几个关键问题的解决进行了研究。不单研究了此款硅基LED 显示屏的电气特性,并结合实际穿戴设备中使用中的关键技术指标要求,针对性地设计了驱动电路。对视频传输接口的设计、亮度的调节、gamma 的控制方式等进行了深入地分析,并介绍了具体的实现过程,达到了体积、功耗、亮度调节范围、显示质量等指标的平衡[4-9]。本文的研究成果为其他同类显示屏的驱动设计和相关产品的开发提供了参考和借鉴。

1 显示屏电气特性和系统要求

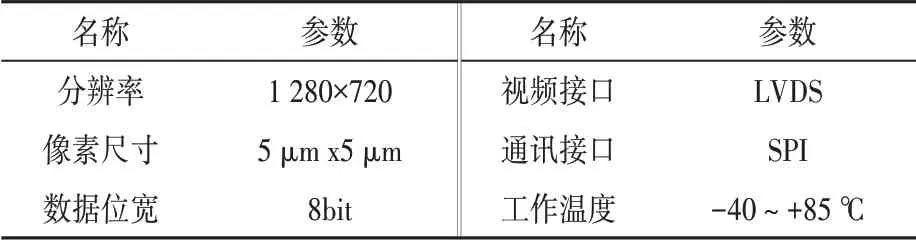

选用的小尺寸硅基LED 是一种有源显示阵列结构,像素大小为5 μm ×5 μm,有效显示面积为1 280×720。此款硅基LED 为电流驱动方式,采用PWM 调节方式实现灰度调节,对应的视频接口为LVDS,数据按bit 形式传输和实现显示,并且通过SPI 接口控制内部寄存器。主要规格参数如表1所示。

表1 硅基LED面板的基本规格

由于此款硅基LED 应用于头戴显示设备上,要求系统具有体积小,重量轻,功耗低等特点。所以选用VESA 标准的LVDS 接口作为驱动板的视频输入接口;上位机需要根据环境需要控制显示屏显示,如亮度控制(最大亮度大于或等于15 000 cd∕m2,最小亮度小于或等于0.5 cd∕m2)、对比度调节、gamma调节等,采用的通讯方式为RS485,考虑到可靠性,采用数据打包方式进行传输;驱动板采用+12 V电源供电,要求最大亮度下,功耗小于2 W。

2 硬件架构设计

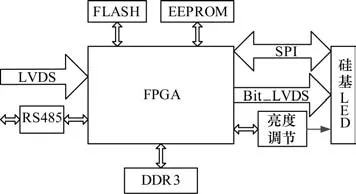

硬件架构如图1 所示。Xilinx 的FPGA 具有支持LVDS 电气特性的差分IO 口,通过其内部的ISERDES、OSERDES 原语能够将串行数据并行化和并行数据串行化,考虑到功耗和PCB 面积的限制,将外部的LVDS 解码器功能通过FPGA 实现。由于此款硅基LED 采用PWM方式进行灰度调节,输入的数据为视频bit面数据,为了显示一帧的视频图像需要通过视频缓存器将数据缓存,然后按bit为读出,组织成屏能接受的格式进行传输,所以需要通过DDR3 进行视频数据缓存。屏之间是有差异的,为了保证产品光电性能的一致性,需要对屏及FPGA内部参数进行相应的调整,以补偿这种差异性,所以采用一颗EEPROM来存储这些参数[10-13]。

图1 硅基LED显示驱动硬件架构

硅基LED 是电流型驱动方式,其发光亮度和流过像素的电流成正比关系,控制宽度最直接的方式就是增加LED 阵列两端的电压,在一定范围内电压增加,电流也会相应增加,所以通过控制LED 阵列的供电电压值来调节亮度。本文采用数字电位器,通过控制电压芯片FB两端的电阻阻值来控制电源芯片的输出电压,电路如图2所示,VLED为LED阵列供电电压。

图2 亮度调节电路

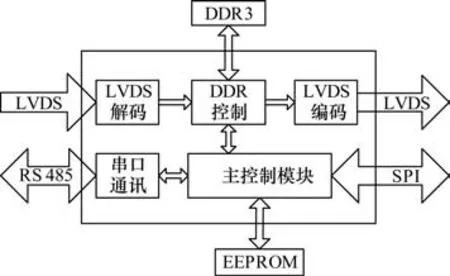

3 硅基LED驱动实现

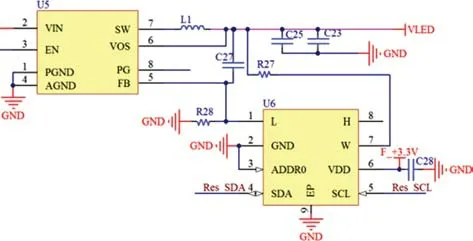

3.1 代码架构

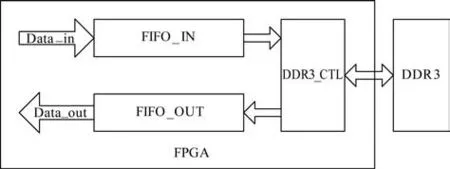

FPGA 是电路中的主控器件,负责视频接口编解码、信号处理、DDR3 控制、通讯、外围电路控制等功能。主要模块组成如图3所示。其中LVDS解码模块完成外部输入的解码,将LVDS 格式信号转化为并行RGB 信号,以便后续处理;并行信号进入DDR 控制模块,被写入外部DDR3 中,并在屏输出时序要求从DDR3 中读出;DDR3输出数据进行LVDS 编码,将数据组织成屏需要的格式,并完成电气转化,以LVDS 信号输出;主控制模块在上电后,实现完成屏的状态配置,然后根据串口输入的命令对系统进行控制和调节,实现亮度控制、对比度、gamma 控制等功能。下面对内部的主要模块功能和实现方式进行分析。

图3 FPGA内部架构

3.2 功能实现

3.2.1 LVDS解码

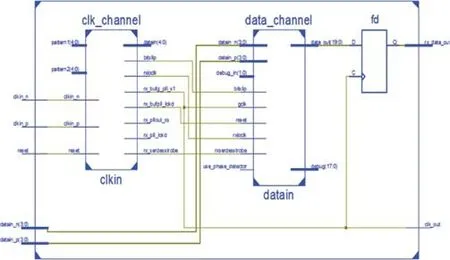

在Xilinx 的Spartan6 系 列FPGA 中,有ISERDES 原语,用来实现数据的串行∕并行转化。为了简化LVDS 解码电路,本文采用ISERDES,IODELAY 以及相位检测电路来实现。由于VESA 标准的LVDS的时钟和串行数据的速率比例是1∶7 的关系,所以需要通过PLL 来产生一个输入时钟7 倍的内部高速采样时钟,来对输入的数据进行采样。由于LVDS 是通过随路时钟来产生数据采样信号和数据对齐模板,所以LVDS 的时钟和数据分开处理。LVDS解码模块的RTL级图如图4所示。

图4 LVDS模块内部架构

输入的一对差分时钟信号经过IBUFDS 原语转化为单端时钟信号后,通过IODELAY 来调节延时,并通过ISERDES 生成数据对齐模块数据,来完成数据通道的数据位对齐。IODELAY 和ISERDES 的控制时钟IOCLK,IOCE 和GCLK 由通过IODELAY 延时的时钟信号输入到PLL,和BUFPLL 转化输出。延时后时钟信号输入到级联的ISERDES 模块,生成数据位对齐模板,当数据不能对齐,由相应的状态机控制时钟通道和数据通道的ISERDES模块的BITSLIP管脚,使数据重新对齐。

输入的4对差分数据信号,分别经过IODELAY和ISERDES模块。此两模块采用MASTER和SLAVE两个模块级联方式。IODELAY 模块的操作过程是首先对MASTER和SLAVE 模块进行校准,其中MASTER 延迟到half MAX位置,SLAVE 延迟到MAX 位置,并且后续始终保持SLAVE 延迟位置为MASTER 位置加half MAX 的关系。延时后的数据分别输入到ISERDES 模块,完成数据并行化,在BITSLIP 信号控制下完成数据位匹配。ISERDES输出的VALID和INCDEC作为相位检测模块的输入,在这两个信号的控制下,调节IODELAY 模块的延迟位置,保证采样时钟在数据位的中间区域采样,确保信号正常采样。

3.2.2 DDR3控制

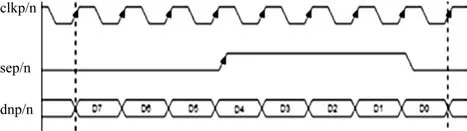

硅基LED 的数据接口为LVDS,数据格式如图5 所示,其中clkp∕n 为传输时钟,上升沿有效;sep∕n 为数据同步信号,用于接收端数据对齐;dnp∕n为数据信号,共4 对,也即一个LVDS 帧传输32 bit 数据,由于一行数据有1 344 个,则在传输一行数据时需要42 个时钟周期,而为了保证实际显示结果的处理,至少需要45 个时钟周期进行一行数据的传输。为了配合屏的数据时序要求,需要通过数据缓存来实现,本文采用的是DDR3 作为数据缓存器。

图5 屏接口LVDS时序

图6 所示为DDR3 的控制模块框图,主要由数据输入、输出FIFO、DDR3 控制模块组成。其中输入、输出FIFO 用于数据缓存、跨时钟同步、数据位宽调整的功能。输入、输出FIFO 在DDR3_CTL 模块的控制下进行数据的读出和写入,DDR3_CTL 模块的主时钟为例化的DDR3 IP 的输出时钟ui_clk,FIFO_IN 的写时钟为LVDS解码后的外部像素时钟,FIFO_OUT 的读时钟为输出给屏的时钟,这里为31.05 MHz。FIFO_IN 的读时钟和FIFO_OUT 的写时钟为ui_clk。FIFO_IN 的输入位宽为8 bit,一个像素数据量,输出为DDR3的控制位宽128 bit,而的FIFO_OUT 的写入位宽为128 bit,其读出位宽为256 bit,这是因为输出给屏的一个LVDS 帧对应的是32个像素。这样直接通过FIFO 转化,能够显著减小控制复杂程度,并和后续模块进行无缝对接。

图6 DDR3控制模块

DDR3_CTL 模块是DDR3控制模块的核心,主要完成数据的读写控制以及读写仲裁。读写控制采用状态机控制,对图7所示的3类FIFO接口进行控制,其中p0_cmd_XXX为读写命令输入接口,p0_rd_XXX 为读数据通道接口,p0_wr_XXX为写数据通道接口。状态机执行过程中,在命令写入、数据写入、读出中要时刻关注对应端口的FIFO的状态,在p0_cmd_full=‘1’时要停止命令写入,直到p0_cmd_full=‘0’;在p0_rd_empty=‘1’要停止数据读使能,直到p0_rd_empty=‘0’;在p0_wr_full=‘1’要停止数据写入使能,直到p0_wr_full=‘0’。数据读写采用猝发方式实现,考虑到数据数量以及操作复杂度,单次猝发长度p0_cmd_bl设置为40,在每次猝发读写命令时都要重新设置起始地址,每次地址自增偏移量为猝发长度的16倍。

图7 DDR IP结构

DDR3 控制模块在下一时刻处于读状态还是写状态,由读写仲裁机制进行控制。由于DDR3 在物理上是单颗芯片,而要实现数据的同时读写,需要在DDR3 中开辟读写空间,采用时分复用的方式,控制读写,一帧数据读写完成后,读写空间交换,保证视频连续输出。为了避免输出视频错乱,优先保证输出数据的量,也即在达到一定的输出数据量之前以读操作为主,达到数量之后,读写操作根据相应标志交替进行,确保数据的连续性。

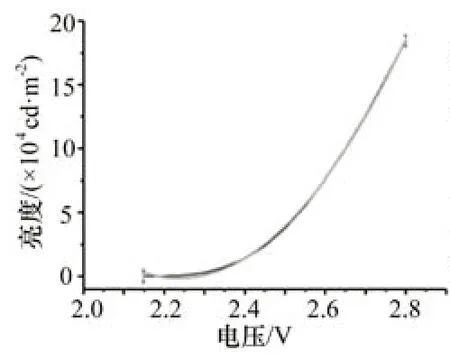

3.2.3 gamma控制

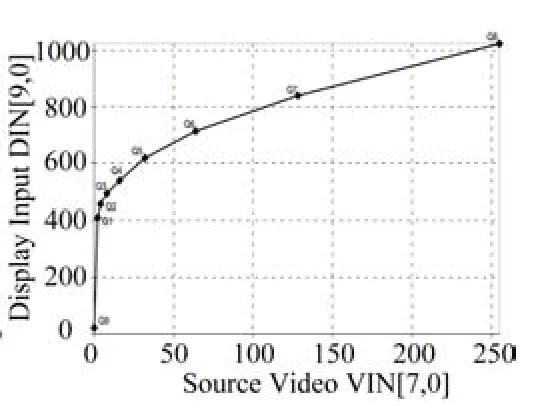

硅基LED 的亮度变化范围为:最大亮度大于或等于15 000 cd∕m2,最小亮度小于或等于0.5 cd∕m2。屏亮度和VLED 之间存在非线性关系,如图8所示,这造成不同亮度下对应的gamma 发生了变化,表现为灰阶画面的层次在不同亮度下有差异。为了克服此问题,提升显示效果,需要动态地调节gamma曲线。

图8 亮度与电压关系

在FPGA内部通过构建LUT,实现gamma曲线的改造。如果每一级灰度对应一个gamma数据,在调光级数比较多的情况下,需要一个容量巨大的LUT来存储所有的数据。为了减小数据量,采用如图9所示的9点法,改造gamma曲线,每一点对应的输入灰度值是固定的,两点之间的值通过线性拟合方式计算得到,这样只需要256×70 bit的空间就能实现256级亮度下的gamma矫正。实现过程如下:

图9 gamma调节示意图

首先,根据亮度级数查找得到对应的Q1,Q2,…,Q7共7个数据;然后,根据这7个数据计算所有0~255灰阶对应的gamma 数据,对应的计算公式为:data_out=其 中Gn≤data_in≤Gn+1,data_in ϵ(0,255);最后将计算的256 个数据写入对gamma LUT中,用于视频数据矫正。

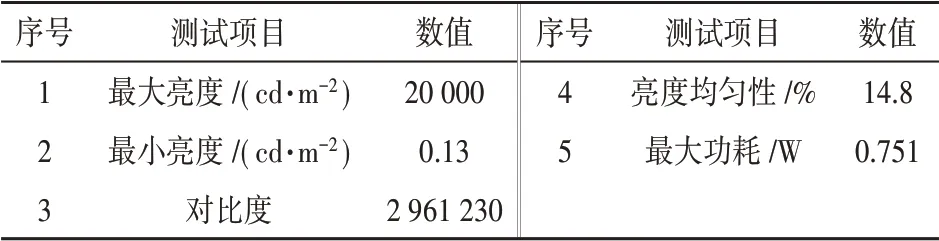

4 性能测试

驱动电路调试完成后,点屏效果如图10所示,实现了预期的各项功能,进一步对主要的光电指标进行测试,主要测试数据如表2所示。由表可知,硅基LED 在亮度,对比度和功耗上均满足要求,驱动设计满足技术要求。主要光电指标和LCD 同类产品相比有明显的优势,所以其在头戴显示类设备上使用有明显的优势。

表2 测试数据

图10 实物显示效果

5 结束语

硅基LED 在穿戴式设备中被越来越多的应用,由于其具有独特的电气和光学特性,使其在穿戴式设备中应用还有一些关键的问题需要被解决,以便实现工程化应用。本文以一款硅基LED 显示屏为研究对象,根据实际的硅基LED 显示屏的电气特性,针对性地进行了驱动电路设计。本文设计的驱动电路实现了LVDS 数据解码、显示控制(亮度调节、对比度调节、gamma 等)、通讯控制等功能。并对设计的驱动进行了测试,得出了关键的性能指标,通过测试数据的分析,其在亮度、对比度和功耗等指标上均满足设计要求。本文的研究为硅基LED在头戴显示类设备的使用提供技术积累和设计参考。