碳化硅器件封装进展综述及展望*

杜泽晨,张一杰,张文婷,安运来,唐新灵,杜玉杰,杨 霏,吴军民

(全球能源互联网研究院有限公司先进输电技术国家重点实验室,北京 102209)

1 引言

随着我国的能源占比和能源消费方式由以化石能源为主转变为以电能、氢能等清洁能源为主[1-2],2020年9 月,习近平主席在联大宣布:中国将采取更加有力的政策和措施,二氧化碳排放力争于2030 年前达到峰值,努力争取2060 年前实现碳中和。2021 年3 月,中央财经委员会第九次会议提出构建以新能源为主体的新型电力系统[3]。

碳化硅(SiC)禁带宽、临界击穿场强大、热导率高,是第三代半导体的典型代表,SiC 材料、器件已经列入国家“十四五”科技规划,其具有电压高、损耗低、耐高温工作等优势,对于电力电子装备高效化、小型化具有重要作用[4-5]。

SiC 材料的这些优良特性,需要通过封装来实现功率和信号高效可靠的连接,才能在电力电子装备中得到完美展现,而传统的硅基器件封装技术在应用于SiC 器件时面临着如寄生电感过高和高温下性能退化等问题。本文总结了几种低寄生电感封装技术及高温封装技术,并对SiC 器件在新能源电力系统中的发展进行了分析和展望。

2 低寄生电感封装技术

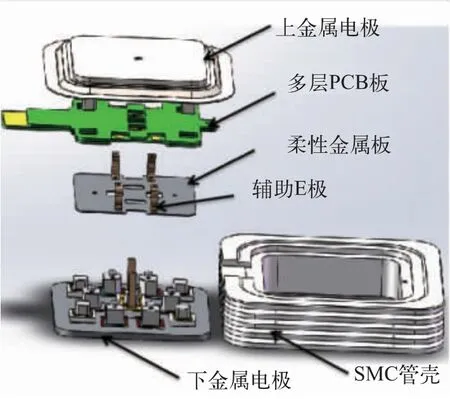

2.1 芯片无应力封装

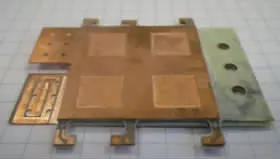

为降低高压SiC 模块的寄生电感,同时消除芯片表面的应力,全球能源互联网研究院提出了一种寄生电感极低的封装结构ZPOC(Zero Pressure on Chip)[6]封装,ZPOC 封装示意图如图1 所示;随后联研院采用ZPOC 封装结构,基于正向参数匹配与芯片并联,研制了6.5 kV/100 A SiC SBD 器件;结合SiC SBD 串联技术,实现6 支器件串联,研制了39 kV/100 A SiC SBD组件,并在24 kV 换流阀功率模块中得到应用。

图1 ZPOC 封装示意图[6]

应用ZPOC 封装技术的模块使用了焊接与压接相结合的封装形式,具有双面散热、易于串联、电磁兼容等优势,可以有效降低模块在封装过程中引入的寄生电感,经实验测得封装寄生电感为3.56 nH,对改善模块的开关特性具有显著优势。

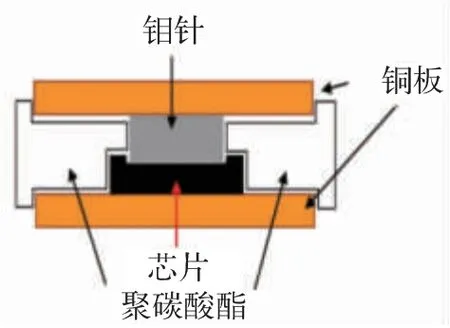

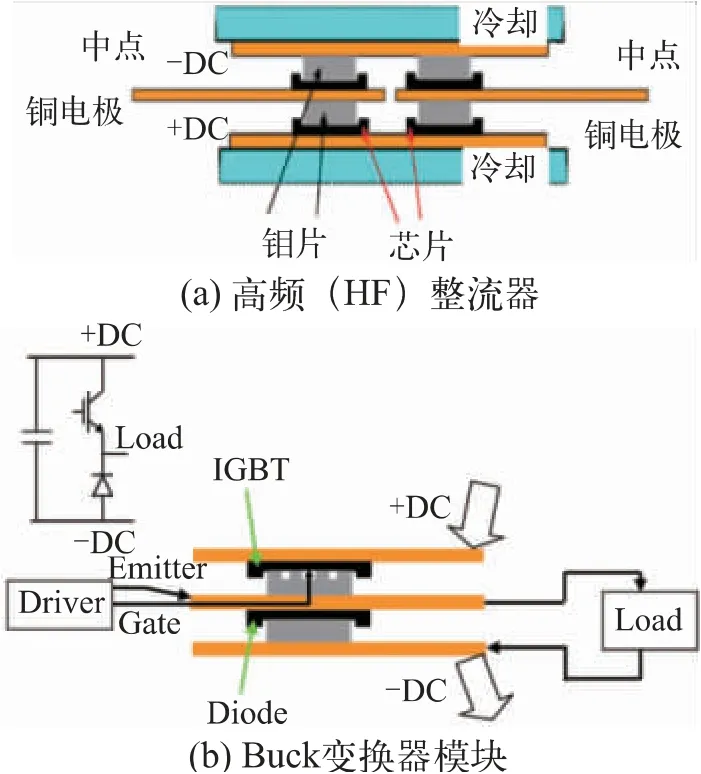

2.2 三维(3D)封装

3D 封装(示意见图2)技术将SiC 模块的上桥臂直接叠加在下桥臂,上下叠加后可以减小桥臂中点的连接线(见图3),该封装技术可将模块寄生电感降至1 nH 以下[7-8]。

图2 3D 封装示意图[7]

图3 采用3D 封装的SiC 器件[8]

2010 年格勒诺布尔电气工程实验室VAGNON[9]利用3D 封装技术搭建了单相400 V/40 A 高频(HF)整流器及Buck 变换器模块。实验结果表明采用3D 封装技术后IGBT 在关断时仅有10%的电压过冲,且在导通时几乎没有欠压。因此3D 封装技术可以基本消除共源极电感,同时共模电流也得到了很好的抑制。

2015 年,欧洲研发中心的REGNAT[10]提出了一种基于印刷电路板(PCB)嵌入式芯片技术的新型3D 封装。利用PCOC(片上电源)技术将SiC MOSFET 芯片嵌入PCB 内部实现较低的电感路径和共模电容。

文献[10]搭建了如图4 所示的模块,该模块具有30 mm×30 mm×2 mm 厚的PCB,上下表面为105 μm铜平面,模块边缘有16 个去耦电容。为了在阻抗测量期间对开关状态下的换向单元进行建模,在前环和后环中未填充的芯片位置通孔的加和减端之间实现了短路。测量连接器位于两个自由边上,因此只需反转模块即可测量前换向环路和后换向洛普阻抗。测量结果为前环的功率环路电感为0.23 nH,后环的电感为0.21 nH,因此采用嵌入式芯片技术的PCOC 模块可实现紧凑、高密度的功率模块,同时可大幅降低回路的寄生电感,使其适用于具有快速导通和关断时间的宽禁带半导体器件(如SiC 等)。

图4 带嵌入式芯片的PCOC 模块[10]

3D 封装技术消除了模块中的键合线,可以有效提高器件的功率密度,充分发挥SiC 器件的高频优势。同时采用3D 封装技术可以降低回路的寄生电感值,减小模块体积,从而推进电力电子器件走向高频、高效、高功率密度。

2.3 DBC+PCB 混合封装

传统焊接型模块封装使用覆铜陶瓷板(Direct Bonded Copper, DBC),芯片只能在表面上布局,大电流回路面积使得降低模块的寄生电感变得非常困难。因此CPES、华中科技大学等[11-12]将DBC 工艺和PCB板相结合,在芯片上通过键合线的连接方式引到PCB板上,这样可以直接在PCB 层间实现控制换流回路,通过减小模块电流回路来减小寄生电感参数。

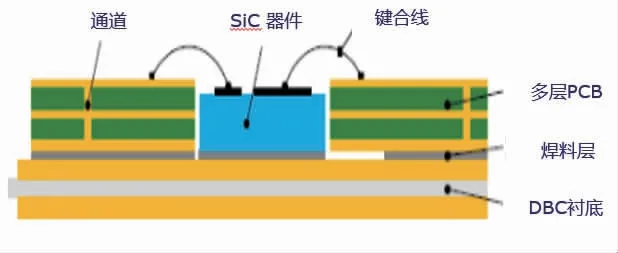

弗吉尼亚理工大学的陈正[13]等人采用如图5 所示的DBC+PCB 混合封装的横截面结构,使用多层PCB来代替原有的聚酰亚胺-铜。通过切割PCB 来嵌入半导体芯片,使得PCB 和器件都可以连接到相同的DBC 基板上,随后使用键合线将器件的顶部电极连接到PCB 上的顶部铜排。

图5 混合封装的横截面结构[13]

与传统工艺相比,DBC+PCB 混合封装具有许多优点。1)封装的PCB 层可以采用标准的PCB 制造工艺[14],并且可以在单个回流焊工艺中与半导体芯片一起焊接到基板上,这大大简化了混合模块的制造工艺。2)通过增加电路板的铜层和使用通孔、盲孔甚至埋孔通孔,可以在PCB 上实现更复杂的布线,使得开关电流路径可以更灵活地控制,同时提供了在模块中嵌入栅极驱动器电路的可能性[15]。3)混合封装技术通过减小电流回路面积来降低寄生电感参数。混合模块的寄生电感仅为分立式TO-247 封装方式的10%~20%。同时与传统的引线键合模块相比,环路电感降低35%,模块体积减小约40%。

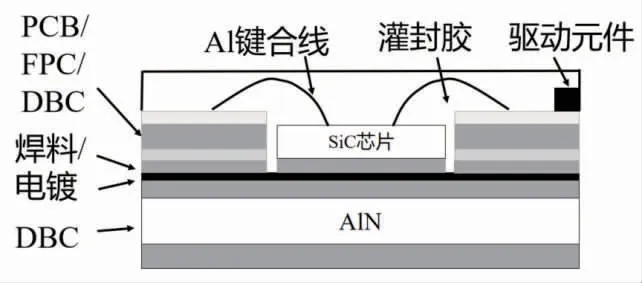

华中科技大学的黄志召[16]设计了如图6 所示的混合模块,该结构包括AlN 陶瓷基板、FPC 和SiC 芯片。芯片通过FPC 上的窗口焊接在底层DBC 上以提升散热能力;芯片和FPC 同时焊接在DBC 上,芯片的上表面电极经由键合线连接在FPC 上,通过过孔来连接FPC 的上下层铜箔。由于换流回路经过的导体存在于FPC 的不同导体层,且电流流向相反形成互感抵消回路;采用薄FPC 增强互感作用,从而可极大地降低主回路的寄生电感。

图6 DBC+PCB 混合封装的SiC 模块[16]

该混合模块通过下管换流回路的阻抗测试结果,由该结果计算出主回路总电感为3.8 nH。同时开通关断的du/dt分别为37.38 V/ns 和37.65 V/ns,可证明使用DBC+PCB 混合封装技术降低了模块驱动回路的寄生电感和共源电感。

两种混合封装形式均可以有效降低模块的寄生电感参数并提升模块的散热能力。

2.4 适用于单芯片的翻转贴片封装

目前商业化的SiC 功率芯片多为垂直型芯片,因此基于BGA 的封装技术,阿肯色大学的SEAL 团队[17]提出了一种适用于单芯片的翻转贴片封装技术,将芯片背面电极通过金属连接件翻转到和芯片正面电极同一平面,使用焊锡固定各自电极(见图7)。

图7 采用翻转贴片封装的单芯片[17]

翻转贴片封装省去了键合线和功率端子,可以有效降低模块的体积,从而减小封装中的材料成本。与常用的TO-247 封装相比,该封装的体积减小至原体积的7.02%,导通电阻降低24%。

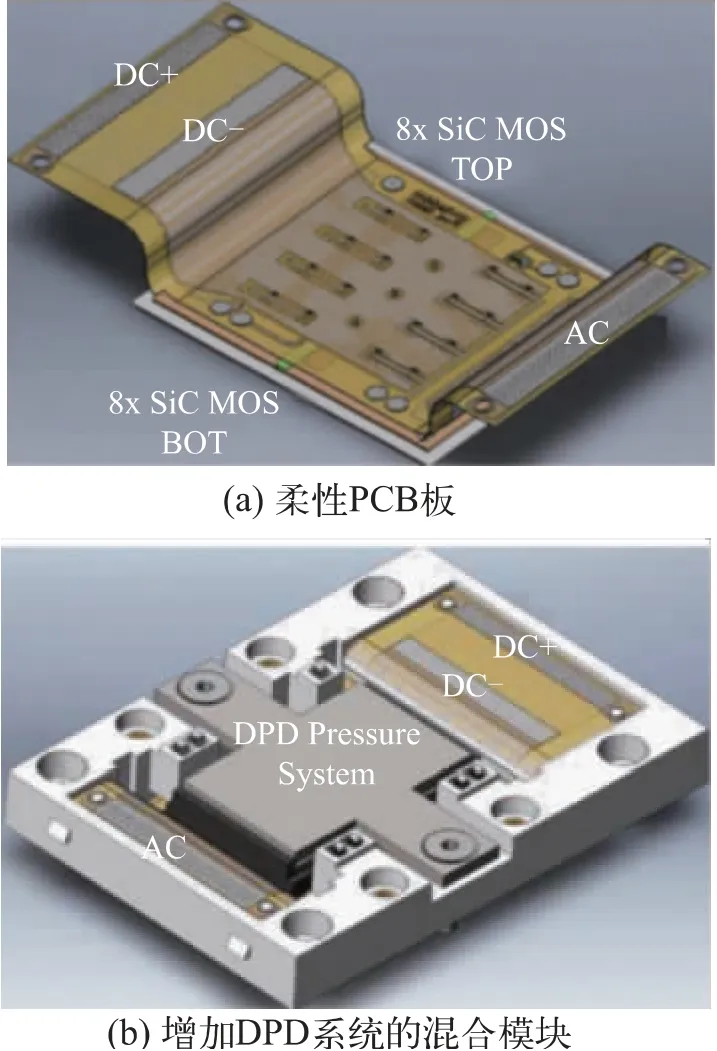

2.5 柔性PCB+双面烧结混合封装

双面烧结技术[18]与传统的芯片焊接和引线键合组件相比可靠性更高。塞米控公司的KASKO[19]通过栅极和源焊盘布局、栅极焊盘位置和隔离、栅极电阻和芯片金属化的调整,组装了如图8 所示的具有极低电感(1.4 nH)的新型1200 V/400 A SiC MOSFET 模块。

图8 柔性PCB+双面烧结混合封装的SiC 器件[19]

混合封装模块中芯片和柔性箔的DBC 间的寄生电感为0.45 nH,柔性箔到带有螺旋弹簧的直流母线的连接间的寄生电感为0.85 nH。

柔性PCB+双面烧结混合封装与相同功率等级的传统模块相比,总寄生电感下降91.3%。而在动态特性方面,混合封装模块开通关断过程中的du/dt和di/dt分别为53 kV/μs 和67 kA/μs。同时与相同功率等级的62 mm IGBT 模块相比,混合封装模块的总开关损耗仅为IGBT 模块的20%。

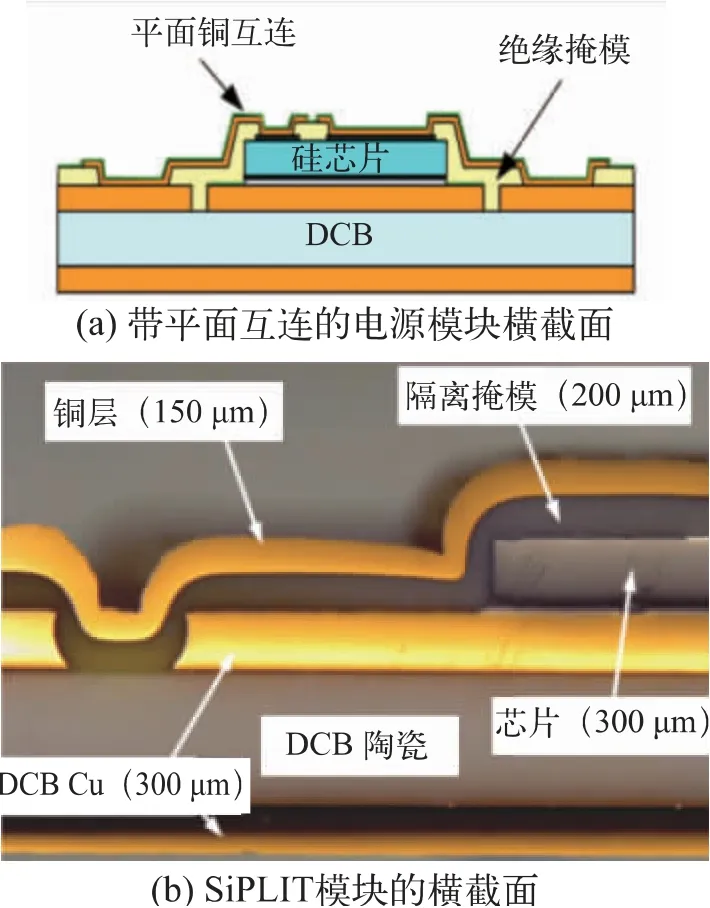

2.6 平面互连技术

为降低器件的导通电阻和寄生电感,西门子公司开发了平面互连技术SiPLIT (Siemens Planar Interconnect Technology)[20]。采用平面互连技术的SiC器件如图9 所示。

图9 采用平面互连技术的SiC 器件[20]

与引线键合方式相比,平面互连技术的芯片接触面积高达90%,并提供了更大的横截面。因此,采用平面互连技术芯片的封装电阻降低了25%;此外与引线键合跨越的环路相比,互连的共面结构仅覆盖了很小的电流环路区域,从而使互连的寄生电感降低了50%。SiPLIT 技术能够克服厚铝线键合带来的性能和可靠性限制。实验结果证明该技术可以有效降低封装中的电阻、电感和热阻,并有效改善EMI 性能。

3 高温封装技术

3.1 双面散热技术

双面封装工艺通过在模块芯片上下表面均焊接DBC 板或者使用银烧结技术将芯片一面与DBC 焊接、另一面连接铝片来实现更好的散热。双面封装技术不仅可以改善电路板边缘场强分布,还可以降低EMI 及桥臂中点的对地寄生电容,因而在新能源电动车内部的模块中有着较强的应用需求[21]。

株洲中车的王彦刚等[22-23]研发了具有双面冷却的650 V/600 A SiC 半桥DSC 汽车电源模块,将功率芯片的两侧粘合到具有隔离能力的平面部件上,金属垫片直接粘合在芯片顶部,粘接界面通过焊接或银烧结工艺形成。与单面冷却无底板模块相比,热阻减少了30%。

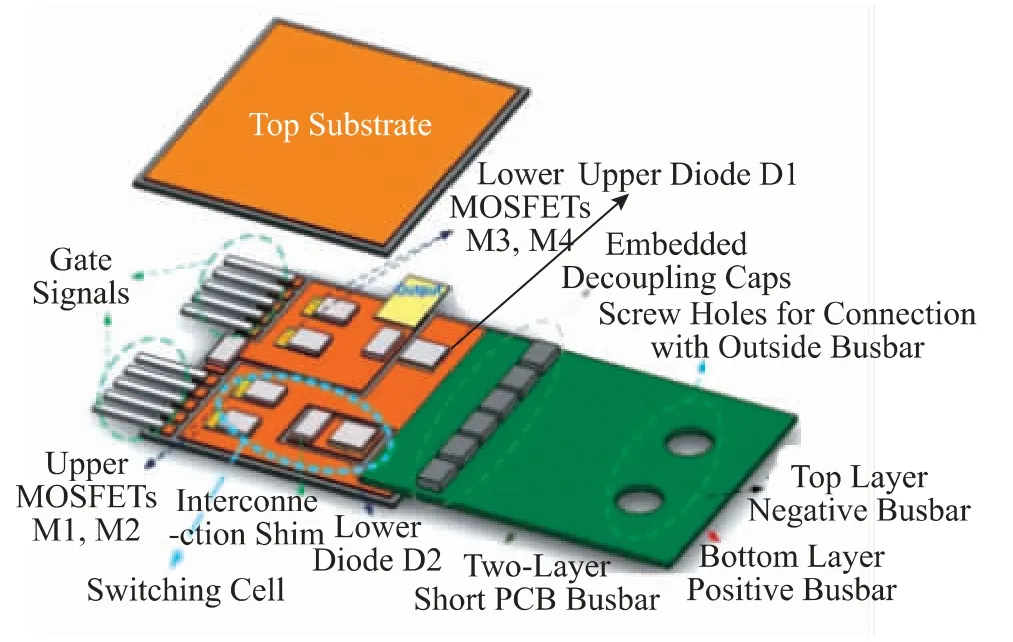

田纳西大学的YANG 等[24]设计了一种具有双面散热的低寄生电感SiC 功率模块(如图10 所示),采用岛式基板布局,与传统封装相比,新封装的功率环路电感从6.59 nH 降低到2.6 nH,降幅达到60%以上。

图10 采用双面散热的低寄生电感功率模块[24]

CREE 的LIANG[25]设计了如图11 所示的双面散热模块,两个冷板(冷却器)直接粘合到这些基板外部,从而允许模块双面集成散热。采用相位桥接线电气拓扑结构的电源开关采用面朝上/面朝下互连配置。与传统模块相比,这一模块将这些寄生效应相关的损耗降低了75%,模块组件的双面散热将比热电阻率降低到0.33 cm2·℃/W,与传统模块相比降低了38%。该模块的电流密度达到220 A/cm2,达到传统模块的1.52倍。

图11 采用双面散热的电源模块[25]

与传统封装相比,双面散热技术的优点在于可以有效降低模块的热阻,从而提升模块的散热能力及电流密度;进而可以有效降低系统中散热组件的体积,提升系统整体的功率密度。

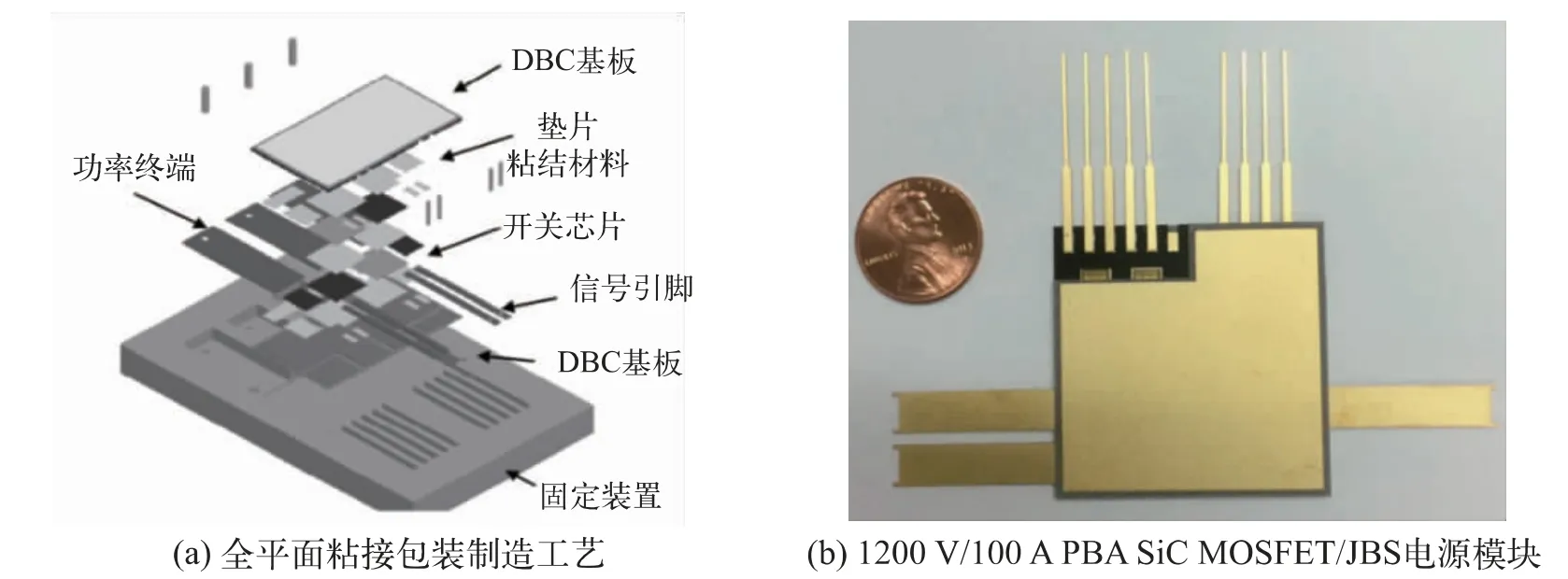

3.2 低压烧结工艺+铜线键合技术

SiC 的高温特性在带来诸多便利的同时,也对封装材料和工艺提出了新的要求。丹佛斯公司的HAUMANN[26]提出了一种低压烧结工艺实现芯片连接,工艺上通过金属化、顶部连接的金属缓冲板(丹佛斯键合缓冲器DBB)以及铜线键合3 种创新解决方案来实现。其中低压烧结过程为:在连接部件间涂上银浆,随后施加压力,在致密银层和连接件(例如DCB基板)之间产生稳固的连接;其次,采用铜线键合使电流容量增加37%。应用该技术的400 V/150 A 模块功率循环能力提高了1.5 倍,达到600000 次循环,极大地提升了模块的可靠性。

目前常用锡片或锡膏作为芯片和DBC 板间的连接剂,其工艺成熟简单,但焊锡的热导率较低且会随温度变化,对于高温工况的SiC 器件适用性较差,焊锡层的可靠性问题易造成模块失效。BOETTGE[27]使用烧结银连接(LTJT)和瞬态液相焊接(TLPS)技术,有效降低了焊料层的空洞率。

高温封装技术采用了铜线键合技术、LTJT 及TLPS 技术,有效提升了模块的电流容量,降低了焊料层的空洞率,从而有效提升模块在各类高温工况下的可靠性。

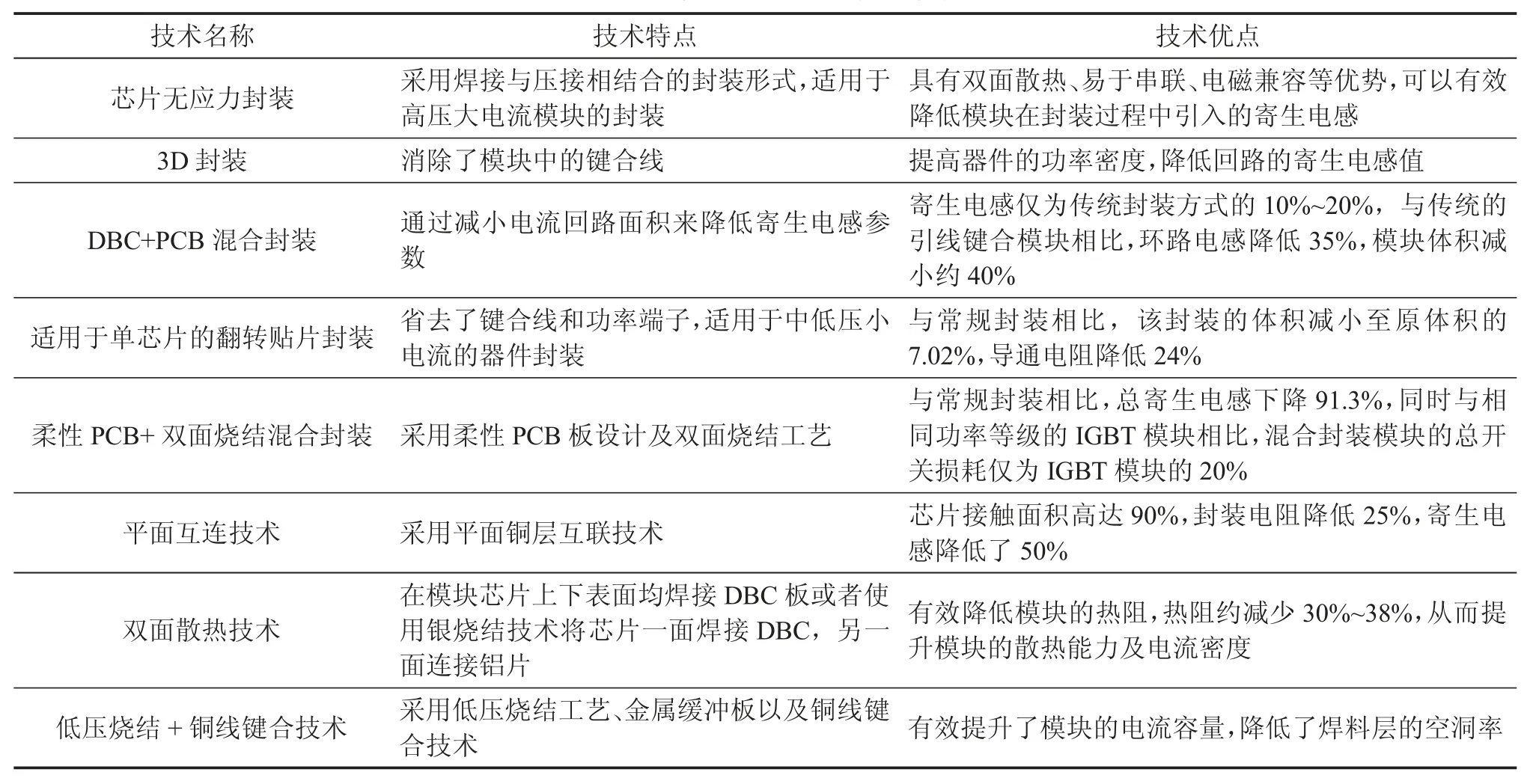

4 新型封装结构和高温封装技术总结

通过分析以上几种低寄生电感的新型封装结构和高温封装技术,可以发现虽然SiC 功率器件的高速开关特性实现了新型电力电子装备的高可控性和低开关损耗(即高转换效率),但是高开关速度的实现依赖于低电感布线等新技术。8 种技术的技术特点及优点如表1 所示。

由表1 可知,芯片无应力封装、3D 封装、DBC+PCB 混合封装、柔性PCB+双面烧结混合封装和平面互连技术均可降低模块的封装寄生电感;其中柔性PCB+双面烧结混合封装技术降低寄生电感的幅度最大,达到91.3%;平面互联技术和反转贴片封装技术均可降低25%左右的导通电阻,双面散热技术可降低30%左右的热阻。

表1 各类封装技术的特点及优点

5 SiC 封装的挑战与展望

随着我国开始构建以新能源为主体的新型电力系统,需要电力电子装备在电力系统各个层面起到关键支撑作用,SiC 器件的应用将大大推动电网柔性半导体化进程,SiC 器件在新型电力系统中应用前景广阔。在可预见的未来,电力电子器件将向高频、高效、高功率密度方向快速发展。

在电力系统领域,随着对高电压、大电流SiC 器件需求的不断增长,业界对于模块的封装寄生电感、导通电阻、开关损耗、热阻等参数也提出了更高的要求,因此在封装层面将需要导热系数和热膨胀系数优良的封装材料,寄生电感更低的新型封装结构,多功能集成封装模块内部抗干扰以及更好的散热方式等,这些要求对未来封装技术的发展指出了方向。传统硅基模块的封装技术在SiC 模块中应用存在诸多问题,随着基于SiC 等宽禁带半导体材料的模块在市场中占比的提升,未来新型的封装技术将重点聚焦于降低模块的寄生电感和提升模块的高温可靠性这两个方面。