30 nm PMOS器件总剂量辐照实验与仿真

张宏涛,曹艳荣†,王 敏,任 晨,张龙涛,吕 玲,郑雪峰,马晓华

(1. 西安电子科技大学 机电工程学院;2. 宽禁带半导体技术国家重点学科实验室: 西安 710071)

当宇宙飞船等航天器在充斥着大量的质子、电子与重离子等各种宇宙射线的宇宙环境中长期运行时,会受到辐照累积的影响,导致电子系统受到损伤乃至损坏,从而无法正常运转,因此要求航天用芯片或器件具有优良的抗辐照性能[1-4]。同时,具有高抗辐照性能的器件与芯片在地面上也有广泛的应用,无论是用于放射治疗的医疗仪器还是核工业中的电子仪器,均长期处于累积辐照环境中,受到大剂量的γ射线与中子的辐照[5-6]。在芯片的制备工艺中,离子注入、干法刻蚀和X-ray光刻等工艺均会引入辐照造成芯片损伤[7-9]。当主流芯片的MOSFET特征尺寸达到纳米量级,还会引入一些新的辐照损伤机制。器件尺寸减小会导致栅氧化层厚度减薄,辐照在栅氧化层引入的缺陷减小,而在浅槽隔离区(shallow trench isolation,STI)的影响更严重。考虑到STI电荷对器件特性的影响,原有的辐照退化理论需要修正。因此,探寻纳米器件的辐照损伤机理,为辐照加固技术提供理论支撑尤为重要[10-11]。本文采用实验与仿真相结合的方式,研究30 nm先进工艺的硅基MOSFET器件的辐照效应规律和物理机制。

1 PMOS器件仿真模拟

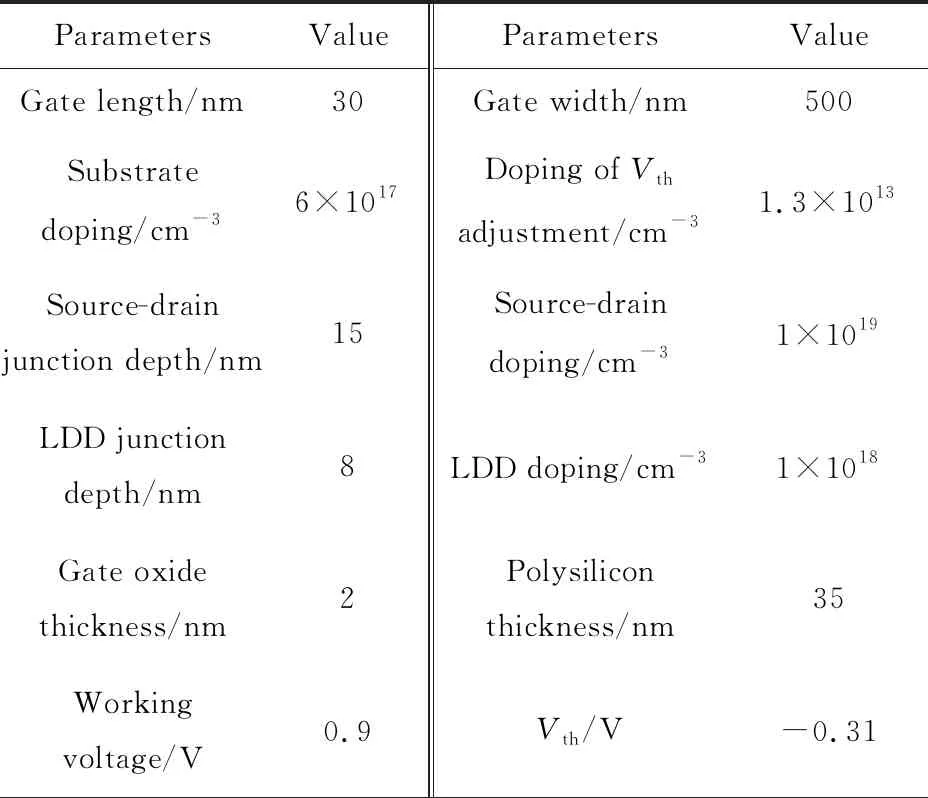

使用Silvaco TCAD软件建立了PMOS器件3维仿真模型,如图1所示。在STI氧化层与沟道界面及沟道与Si/SiO2界面处设置细化网格,网格尺寸为1 nm,其余为20 nm。为提高仿真运算速率,设置网格数不超过软件的上限2 000[12]。该模型结合了表1所列的30 nm工艺PMOS器件仿真参数,通过不断优化调整使仿真中的器件模型尽可能地与真实器件一致,从而提高仿真的可信度。

表1 30 nm PMOS 器件仿真参数Tab.1 Structure parameters of 30 nm PMOS device in simulation

根据PMOS器件模型,仿真模拟得到30 nm PMOS器件线性转移特性曲线,如图2所示。由图2可见,该曲线与实际PMOS器件测试的转移曲线基本一致,证明本文建立的PMOS器件模型可仿真模拟实际器件。

采用加入电荷的方式模拟器件受γ射线辐照影响,通过辐照前后试验数据提取电学参数的变化量,可表示为

(1)

其中:ΔS为亚阈摆幅;ΔDit为界面陷阱电荷变化量;q为电子电荷;Cox为栅氧化层电容。由式(1)可求得界面陷阱电荷变化量,亦可求得氧化层陷阱电荷变化量。加入相应电荷,辐照前后,30 nm PMOS器件线性转移特性曲线,如图3所示。

2 总剂量效应实验

利用60Co作为辐照源,开展累积辐照总剂量为1 000 krad(Si)的总剂量效应实验。实验器件选择在某商用工艺线流片的30 nm工艺PMOS器件,器件的栅介质是HfO2与SiO2组成的高介电常数介质,HfO2与SiO2的厚度分别为1.63,1.48 nm,同一器件经多次重复测量,特性重复性较好,同一型号不同器件之间特性测试一致性较好,表明器件有稳定的特性,能保证实验的有效性和可靠性。为得到不同辐照总剂量下器件的退化数据,分别在辐照总剂量D为250,500,750,1 000 rad(Si)时,将器件从辐照源取出,对各个器件进行测试,得到不同剂量辐照下30nm PMOS器件线性转移特性曲线,如图4所示。

由图4可见,器件线性转移特性曲线随着辐照的剂量增大负向漂移,表明器件在辐照过程中产生了均为正电的氧化层陷阱电荷与界面态陷阱电荷,使器件需要更大的负电压才能抵消辐照引起的负漂移。采用固定漏电流法提取器件的阈值电压,可表示为[13]

(2)

其中:W为栅宽;L为栅长;Vg为栅电压;Id为漏电流,μA。由式(2)可知,该方法提取的阈值电压由器件的尺寸决定。提取阈值电压后,计算每个辐照阶段与前一阶段的阈值电压差值可更清晰地了解每一阶段陷阱电荷对器件阈值电压的影响,阈值电压变化量ΔVth随辐照剂量的变化关系如图5所示。

由图5可见,阈值电压负向漂移,且随着辐照总剂量的增大,漂移量也在增大。2种陷阱电荷变化对器件的阈值电压的影响可表示为[14-15]

(3)

其中:tox为氧化层厚度;ΔNot为氧化层陷阱电荷数密度变化量;ΔNit为界面陷阱电荷数密度变化量;ε0为自由空间的介电常数;εox为SiO2的介电常数。图6 为STI区域陷阱电荷对器件影响示意图。随着器件尺寸缩小,栅宽缩小,栅氧化层厚度减小,栅氧化层能引入的陷阱电荷微乎其微,此时,STI区域引入的电荷逐渐起主要作用,靠近STI区域的寄生导电沟道也会引起器件退化。为体现STI区域的影响,引进不受栅控制而受STI控制的栅宽变化量ΔW,同时由于器件栅宽减小,ΔW/W增大,因此,ΔW的影响也不可忽略。

本文实验的器件沟道长度仅为30 nm,由于沟道受STI区域陷阱电荷的影响,器件ΔW部分的长度不可忽略。对式(3)进行修正,得到

ΔVth,short=ΔVot+ΔVit=

(4)

式(4)考虑了器件ΔW部分,适用于器件沟道长度极短时阈值电压的变化情况,因此,短沟道器件浅槽隔离区域的氧化层正电荷陷阱是造成器件退化的主要因素。

3 仿真与实验结果的比对验证

在图1所示模型上修改得到仅有STI区域陷阱电荷的PMOS器件仿真模型,仿真得到阈值电压随辐照总剂量的变化关系,如图7所示。

由图7可见,仅加入STI区域陷阱电荷的阈值电压与实验测试的阈值电压偏差小于-0.001 V,验证了阈值电压的退化原因主要是STI区域内的陷阱电荷引起的,造成差值是因为500 krad(Si)总剂量辐照后产生了足够多的界面态陷阱电荷,而仿真过程中忽略了这一影响因素。

4 结论

本文使用Silvaco TCAD软件建立了γ射线总剂量效应退化模型,通过仿真验证了30 nm工艺PMOS器件受总剂量效应的影响。并通过实验验证30 nm工艺PMOS器件的阈值电压随着辐照总剂量的增大而负向漂移。受器件STI氧化层陷阱电荷库仑作用的影响,器件有效沟道长度减小。通过仿真与实验比对,验证了STI氧化层陷阱电荷是造成纳米级PMOS器件在γ射线辐照下退化的主要因素。