基于Hi3559 的多路HD-SDI 视频传输系统

王 毅,张 禹,钱宏文

(中国电子科技集团公司第五十八研究所,江苏 无锡 214072)

0 引言

HD-SDI(高清数字接口)标准最早由电影与电视工程师协会(SMPTE)提出,协议规定了利用YCrCb 的色彩空间采用4:2:2 的采样格式传输高清无压缩的SDI 视频信息[1],HD-SDI 由亮度和色度两个单元组成,每个单元分别为10 bit 的数据信息。SMPTE 通过制定标准的274M 和296M[2],包含了常见的不同速率和分辨率的视频格式。HD-SDI 主要用来传输1080P 或720P 的高清视频信息[3],速率为1.485 Gb/s 或1.485/1.001 Gb/s 两种。串行数字接口的特点是采用了无损和非压缩的传输原理,在同轴线缆上传输高清无损视频,具有传输原理简单可靠、视频清晰度高、链路延迟小、实现容易等优点。HD-SDI 视频分辨率高,动态范围广,在对比度、亮度、白平衡[4]等方面具有显著的优势,在各种电视广播、监控安防和高清传输领域使用愈加广泛。

Hi3559 作为华为海思推出的一款强大片上系统(System on Chip,SoC)芯片,不仅具有丰富的视频和各种外围接口,而且内部集成了很多视频图像处理模块,处理器支持不同格式视频的编码和解码、图形的畸变校正、去噪,以及镜像、旋转和色彩的增强等,可用于多路Sensor 视频的输入,内部集成H.265 编解码处理单元,能够支持高清的RAW 原始码流视频的输出,SoC 内部含有高性能图像信号处理器(Image Signal Processor,ISP)[5],SoC 使用了低功耗的架构和工艺技术,支持多路全景硬件拼接[6],为使用者提供了高性能的硬件平台。

近年,视频监控在国内外发展很快,已广泛应用于汽车电子、工业现场和安防监控领域。为了解决单个摄像头在获取监控场景时存在的视场不够的问题,多路摄像头进行视频的采集和传输系统发展越来越来越重要。多路视频传输系统能够将目标物体四周的场景进行无盲区显示[7],在车载辅助驾驶、大型活动现场、高清视频监控、全景地图[8]等各种视频监控场所和领域有着广泛的需求和应用。

Hi3559 的视频接口虽然支持多种Sensor 接口,但Sensor大多是基于移动行业处理器接口(Mobile Industry Processor Interface,MIPI)接口,无法实现长距离传输,同时也没有现成的可以同时对接多路HD-SDI 摄像头的输入方式。因此,本文设计开发了一种基于Hi3559+FPGA 的硬件设计方案,通过软硬件的开发和验证,该设计实现了8路HD-SDI 视频图像的采集、传输和处理,最终通过使用显示屏实现了8 路HD-SDI 视频的实时监控和整体显示。

1 系统设计

1.1 系统框架和工作流程

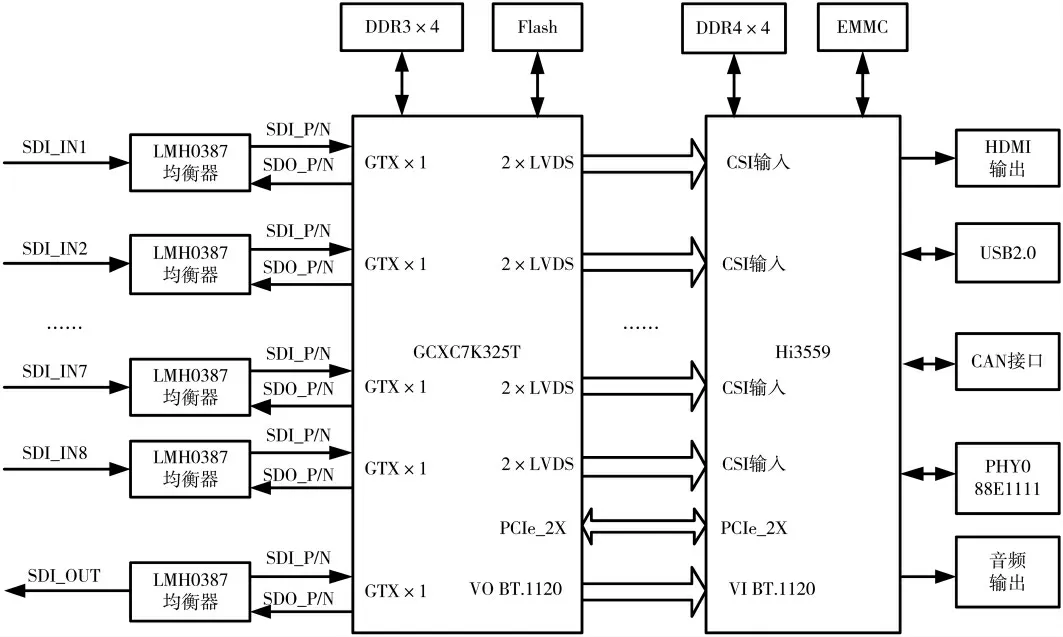

多路HD-SDI 视采集系统采用CPU+FPGA 硬件架构实现,核心器件选用国产化器件,系统主要由国产化的CPU、国产FPGA、SDI 均衡器、DDR4、DDR3、SPI Flash、EMMC 以及时钟和电源组成,系统整体框图如图1 所示。

图1 多路HD-SDI 视频传输系统框图

传输系统的主要工作流程如下:

(1)均衡电路接收外部摄像头的HD-SDI 格式视频信号后发送给FPGA 的GTX 接口;

(2)FPGA 内部通过IP 核进行解串,获取到标准的20 bit 的HD-SDI 视频数据信息[9];

(3)FPGA 将多路HD-SDI 视频数据,通过LVDS 接口将有效的数据和效应区数据信息统一发送给CPU(黑白按照8 bit 传输亮度信息Y,彩色时按照16 bit 传输亮度Y[10]和色度Cb/Cr[11]);

(4)Hi3559 的输入接口通过识别固定的同步码和解析行场信息,获取到有效的视频流数据和视频的宽和高后,通过视频处理子系统(Video Process Sub-System,VPSS)抓取相应的视频码流。

(5)VPSS 接收到视频流后通过内部处理或传递给其他硬件单元进行处理,处理完成后送入视频输出通道,利用视频输出接口HDMI 进行输出和显示。

1.2 系统硬件构成

CPU 选择华为海思的Hi3559 处理器,主要用于完成多路视频的接收和传输,以及后期的算法处理、视频数据处理后的输出,并且扩展了2 路千兆以太网接口用于对外通信和数据的传输。

FPGA 选择国产高性能的GCXC7K325T,该器件封装小、资源多,具有强大、可灵活配置的逻辑编程资源,含有数字信号处理资源(DSP)、36K 的双端口可配置RAM、内建FIFO、10 个时钟管理资源,内含高精度模数转换单元(ADC),支持AES 和SM4 的加密,有16 个GTX 高速接口[12],可配置IO 为500 个,可通过软硬件配合选择设置为多种不同的电平接口。本次设计主要通过GTX 和低电压差分信号(Low-Voltage Differential Signaling,LVDS)进行扩展和传输,GTX 在系统中主要作用是接收均衡电路之后的视频信息然后通过内部IP 核进行数据的解串,LVDS 接口主要是用于与Hi3559 之间进行视频数据的传输和交互。

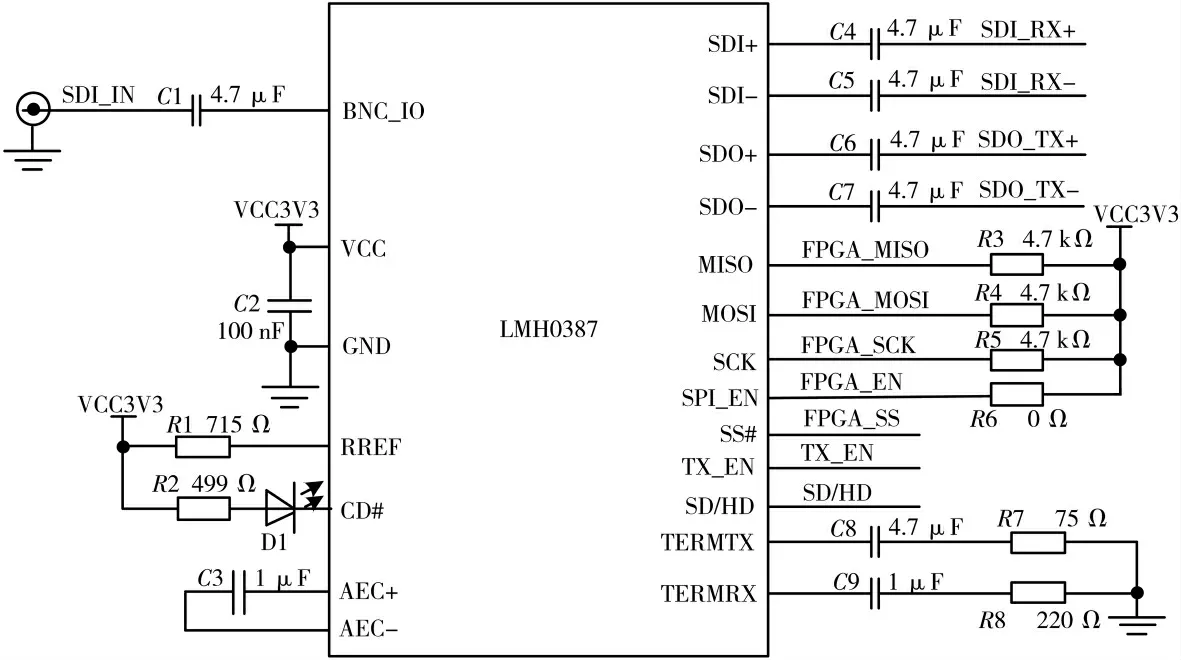

均衡电路[13]采用TI 公司的LMH0387 均衡芯片,该芯片输入输出方式可配置,通过软件配置既可以作为SDI视频输入时的均衡器,又可以作为SDI 视频输出时的线缆驱动器。本次设计采用LMH0387 主要是为了用作输入时接收摄像头的HD-SDI 视频信号,然后发送给FPGA的GTX 的RX。该电路即实现了单端转差分和电平匹配,也增加了摄像头视频数据的接收距离。LMH0387 与FPGA 之间的视频信息由高速接口进行接收或发送,数据参考时钟分开,采用交流耦合的方式对接,电平标准为LVDS (低电压差分信号),本次均衡电路设计原理图如图2 所示。

图2 均衡电路设计原理图

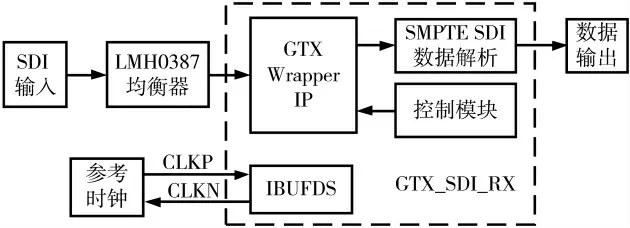

1.3 基于GTX 的SDI 接收模块

目前在SDI 视频传输和处理时,主要有两种方式:(1)通过SDI 视频解串芯片将高速非压缩视频[14]信号进行解串,转化为低速并行数字信号,然后发送给FPGA或者其他SoC 系统进行接收和处理;(2)另外一种方式是通过FPGA 硬件的资源和高速收发器进行解串,直接将不同速率的SDI 视频信号通过同轴电缆传输,并且利用均衡芯片进行均衡和串并转化后对接到GTX 的RX接收,该设计方法相比解串芯片方式从硬件成本和板卡集成度上具有更大的优势,软件一次开发,后期可以重复多次使用。因此,本次设计采用高速GTX 接口实现串并转换,GTX 模块设计框图如图3 所示。

图3 GTX SDI 接收模块框图

控制模块的主要功能包括GTX 收发器的主复位、GTX 内部的PLL 复位、发送器复位、接收器复位以及HD-SDI 速率识别检测(判断HD-SDI 接收的数据速率是1.485 Gb/s 或者为1.485/1.001 Gb/s)。

根据HD-SDI 的协议标准,SDI 数据采用NRZ(归零码)编码格式[14]。因为SDI 的视频数据中不包含时钟信息,因而NRZ 数据码流中很容易出现连续的“0”或“1”信息,连续的“0”或“1”会使得数据流信息含有的低频分量所占比例变大,电平跳变的数量减少,以至于时钟信息极少。为避免这种问题出现,HD-SDI 的信道编码方式根据SMPTE 协的议规定,采用了非归零码[14],非归零码主要通过利用多项式对视频的数据流进行加扰处理,加扰之后:

加扰后的串行数据流中连续“0”或“1”就变得很少[15],电平跳变信息变得多样,使得在接收端变得容易提取和获得时钟相关的信息,在调整图像采样后可输出Y 分量和C 分量。接着,就是对两个分量进行序列检测[16],即提取分量中的定时基准码(TRS)。最后,利用提取的TRS 判断视频格式、分辨率及帧频以及数据的稳定性。在稳定后,可从中提取有效的像素数据。这就是SDI 信号传输的基本原理和解码流程。

1.4 视频传输接口设计

Hi3559 使用MIPI Rx 接口(Mobile Industry Processor Interface Receiver)作为视频传输的数据通道,MIPI Rx 只完成接口的时序转换,不处理图像的数据格式。MIPI Rx可以支持MIPI D-PHY、LVDS、HiSPi 等串行视频信号输入,串行视频接口可以提供更高的传输带宽,增强传输的稳定性。为设计使用的广泛性,将MIPI Rx 配置为LVDS 功能作为Hi3559 与FPGA 之间的多路视频传输的数据通道。

本次设计采用LVDS 电路,LVDS 只约束了电气传输规范,没有时序和数据格式方面的标准协议,LVDS 电路由于相比主流的MIPI 的CSI[17]具有更大的优势,它不需要FPGA 提供额外的IP 核和其他外围电路,只需要进行直流或者交流耦合对接,然后通过利用不同的同步码信息来区别像素的行场消隐区和有效的数据区域。在LVDS 传输模式中,行场同步码的信号是集成在视频的数据流信息中进行传输。

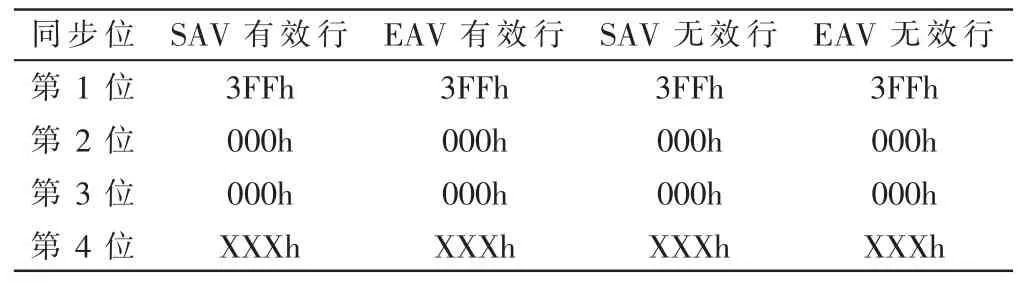

LVDS 模式下需要配置RAW DATA 类型、数据大小端、同步方式、WDR 类型和图像宽高等寄存器。LVDS 模式依靠同步码识别帧的行同步信息,根据RAW DATA 类型的不同,同步码可以分为8/10/12/14/16 bit[5],10 bit 的LVDS 同步码如表1 所示。

表1 10 bit 的LVDS 同步码列表

在同步码中,第4 位由摄像头的厂家决定,本次设计由FPGA 采集到SDI 摄像头为YUV4:2:2 SP 数据格式,通过FPGA 将像素信息按RAW 数据格式重新排序将YUV4:2:2 数据伪装成RWA 数据送海思处理。

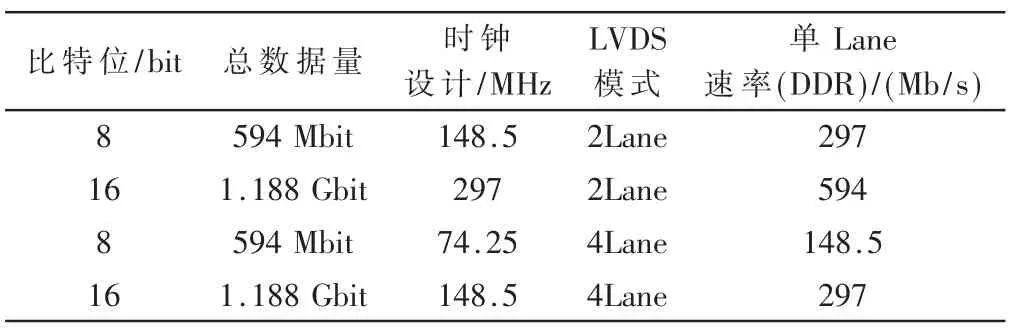

根据SMPTE 292 的标准协议,在传输1 路标准的HD-SDI 视频(1080P@25 Hz)总像素为:2 640×1 125×25×20 bit=1.485 Gbit,因此不影响输出效果下,为了减少数据量并且提高传输的效率,设计在采用LVDS 传输通道时,每个像素由8 bit 像素(彩色选择16 bit)来表示,此时每秒的总像素为:2 640×1 125×25×8 bit=594 Mbit,因而采用2Lane 的LVDS 数据通道,在采用DDR 采样传输时,参考时钟应该设计为148.5 MHz,每Lane 的数据速率为297 Mbit 即可实现8 bit 的LVDS 数据的传输。因此,本次设计采用2Lane 的LVDS 方案可以满足HD-SDI系统传输带宽的需求。其他配置模式下,LVDS 的时钟和数据传输设计已经过验证均可实现,如表2 所示。

表2 时钟和数据传输方式配置

2 系统测试与验证

多路HD-SDI 视频传输系统,利用8 路HD-SDI 摄像头作为视频源的输入,将视频采集程序烧录FPGA内,通过逻辑分析和仿真软件可以判断视频信号是否锁定和成功接收。GTX 获得视频信息后进行解析和处理,然后再利用FPGA 增入相应的同步码信息进行打包处理,通过LVDS 接口将视频数据发送给CPU,通过串口调试输入视频同步的命令可以检测8 路视频的同步和格式,CPU 经过接收和处理后将多路视频采用九宫格的方式输出至HDMI 接口,使用显示屏进行显示。

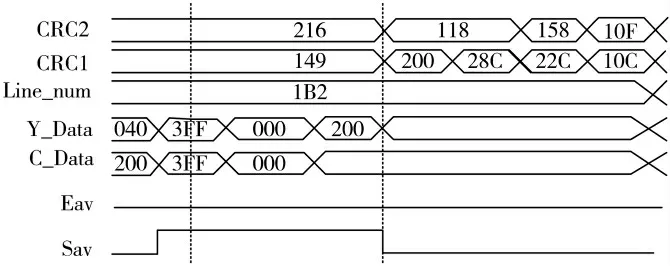

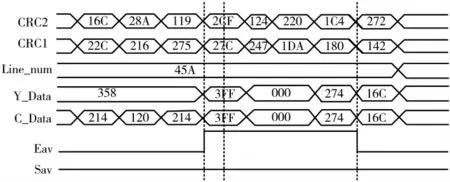

HD-SDI 摄像头按照标准的SDI 数据格式发送出相应的数据信息,FPGA 接收通过同步码信息识别有效信息的行起始和行结束,10 bit 同步码的行起始的时序波形如图4 所示,行结束时序波形如图5 所示。

图4 行起始(SAV=1)时序

图5 行结束(EAV=1)时序

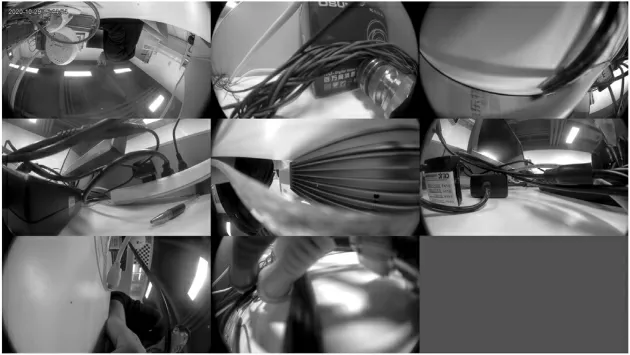

FPGA 通过GTX 成功识别和接收SDI 数据信息后,解析获取有效的HD-SDI 视频信息。将8 路1080P@25 Hz的HD-SDI 摄像头作为输入,利用本次开发的Hi3559 的多路HD-SDI 视频传输系统平台,验证将8 路HD-SDI视频信号进行同时采集、接收、传输、处理后将接收到的视频图像通过HDMI 显示器进行图像显示。通过该视频采集系统处理后,正常8 路HD-SDI 视频图像处理后显示结果如图6 所示。

图6 8 路HD-SDI 视频图像处理后显示结果

3 结论

本次研究通过采用Hi3559+FPGA 架构,设计完成了多路HD-SDI 高清视频传输系统的开发和验证,该系统能够在Hi3559 上实现8 路HD-SDI 视频图像的采集、传输、处理以及全景显示。经过开发和测试验证,该系统能够满足HD-SDI 视频传输的协议标准和速率要求,能够支持长距离的传输,工作稳定可靠。对于想要利用Hi3559 实现多路高清视频的采集、远距离传输以及智能算法等方向具有较高的推广和参考应用价值。