刚挠印制电路板的参考层设计对阻抗值稳定性的影响研究

王宏瑞 党新献 刘新发

(惠州中京电子科技有限公司,广东 惠州 519029)

0 前言

市场上高端消费类及工业类电子产品的刚挠结合印制电路板(刚挠板)对阻抗匹配要求越来越多,当发射端、传输线以及接收端的阻抗相匹配时,讯号损失最小,传输到接收端的讯号最好。以我们日常生活中常见手持扫码设备为例,如果扫码枪内扫描头转接板与主板之间的阻抗不匹配,就会发生扫描传输漏码等问题。为了保证刚挠板线路的阻抗匹配一致性,本文主要针对影响阻抗值稳定性之因素参考层(屏蔽层、接地层、ground)进行了探讨。通过改变参考层,可较大提升阻抗线宽及其阻值稳定性,在介质层厚度及阻抗线调整区间有限的情况下,对于参考层网格的调试是刚挠结合板阻抗控制变异最大的因素。

1 阻抗影响分析

1.1 阻抗影响因素

阻抗匹配是信号完整性的重要组成部分,阻抗影响因素包括绝缘的介电常数Er、介质厚度H1/H2、走线宽度W1(线底)、W2(线顶)和铜厚T1等,如图1、图2所示。分析研究表明,对阻抗影响最大的是介质厚度。

图1 SI90000模拟界面(25 μm PI基材差分阻抗模拟)

图2 SI90000模拟界面(25 μm PI基材特性阻抗模拟)

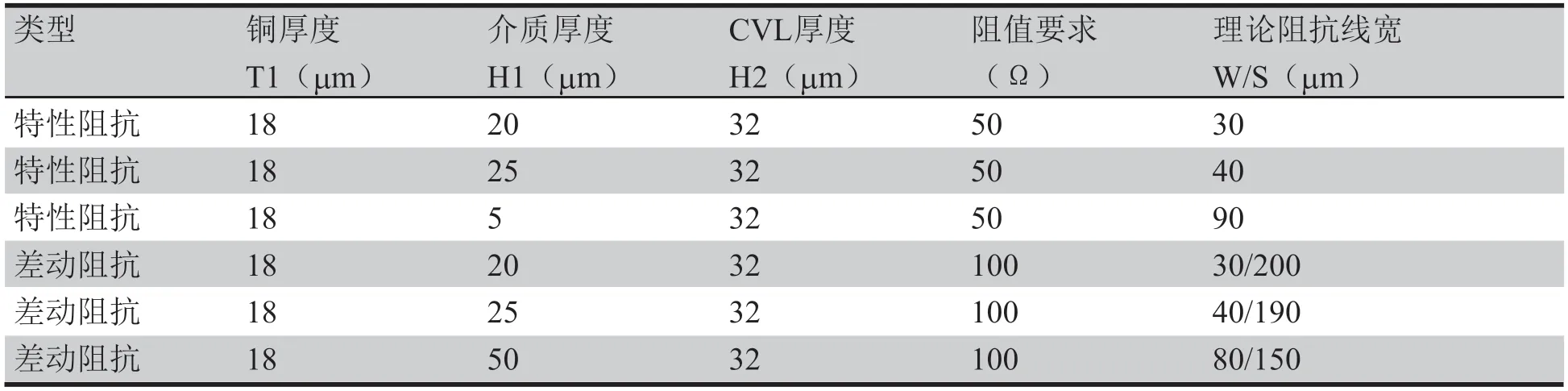

在屏蔽层为实铜阻抗模拟时,50 Ω特性和100 Ω差分阻抗介质厚度H1≥50 μm才能满足实际生产需求;例如使用常用H1=25 μm的介质厚度来测算时,模拟得出线宽仅为40 μm,无法满足部分产品高电流承载度的最小线宽要求,或考量到刚挠板组装后软区耐弯折性能,且细线路制程良率成本较高。如表1中不同介质厚度在参考层为实铜时的阻抗线宽对比。

表1 参考层为实铜时不同介质厚度模拟理论线宽结果对比表

1.2 刚挠板阻抗参考层网格设计原因

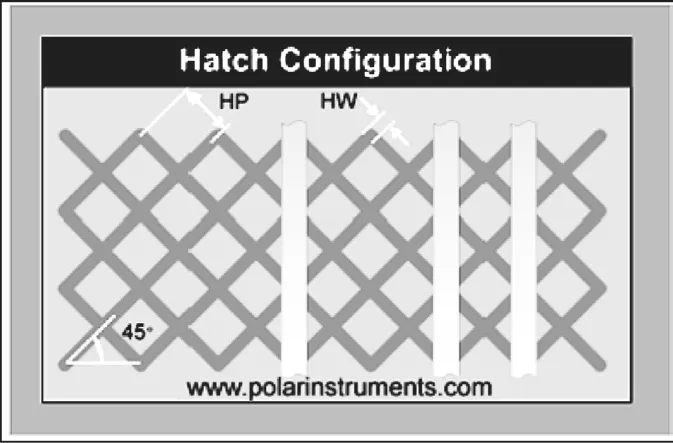

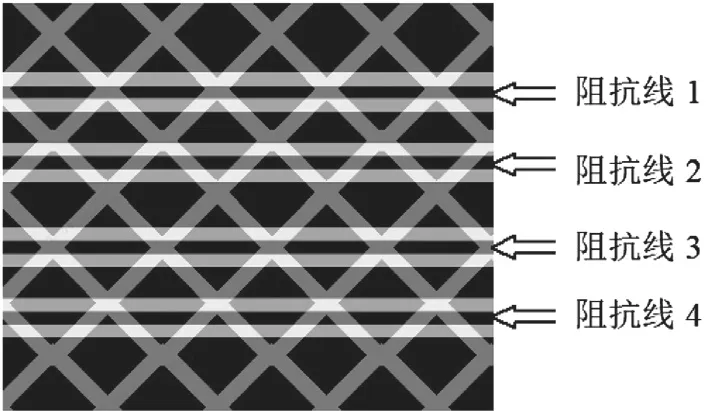

由于刚挠板设计时为了提升其弯折性能,在选材和产品成本考量上尽量要求薄,普通消费类电子产品选材通常选PI厚度≤25 μm的FCCL(挠性覆铜板),产品既要满足软、薄,又要满足阻抗需求,于是诸多线路设计者选择了阻抗网格参考地层设计方案。如图3所示目前业界网格交错阻抗设计均为斜45°阵列方形网格,当阻抗线贯穿网格空隙时,该段阻抗会突变,传输延时会变大,所以理论上在满足制造条件下,网格密度越大阻值越高。

图3 斜45°阵列方形网格图

如图4所示,有6根阻抗线通过网格,但有3根线(1,3,5),刚好在网格上方,也就形成实铜效应;而另外3根线(2,4,6)则是网格形式,这会形成1-3-5的阻抗明显低于2-4-6的阻抗。参考层为45°网格也会有此现象。

图4 不恰当的网格分布图

2 实验部分

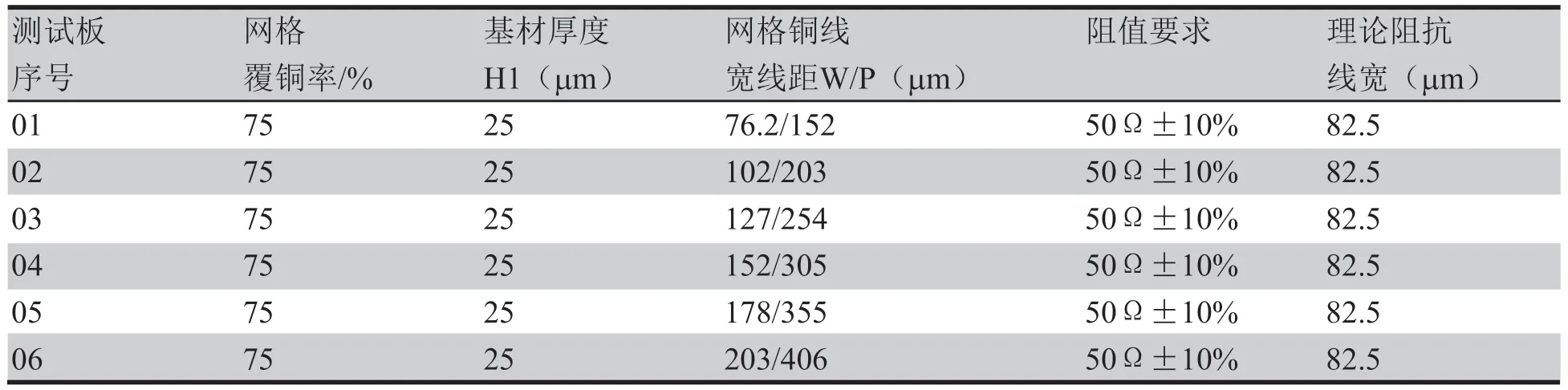

2.1 参考层网格密度对阻抗值的影响

行业内调试阻抗设计都是在确定产品叠构方案与Polar软件模拟理论阻抗值后使用变化参考层网格设计密度来调试阻抗值,下面的测试首先来验证阻抗线参考层网格覆铜率相同的情况下网格密度对阻抗值的影响,使用表2中条件进行测试:

表2 测试条件表

实验小结:表3所示为阻抗线宽82.5 μm的实测阻值随网格密度变化趋势图,测试结果显示在对应参考层网格铺铜率不变的情况下阻值均无明显的变化趋势。网格密度对阻值影响较小。无法完全通过调整网格密度来达到调试阻抗的目的。

表3 82.5 μm阻抗线宽在不同网格密度下阻值测量结果表

2.2 阻抗线参考层屏蔽面积对于阻抗值的影响

由于上述测试结论,即无法完全通过调整参考层网格密度来达到阻抗匹配一致性。因此以下通过刚挠板常见的多组阻抗线阵列设计的实验案例来测试说明。行业常规的45°角方形阵列网格会造成每条阻抗线对应的参考层屏蔽面积不一致,导致多组阻抗线并排设计时各组之间阻值差异性大,图5所示为4组对应网格不同位置的相同差分阻抗线贯穿不同网格位置,并对其阻抗进行实测分析。

图5 45°角阵列方形网格

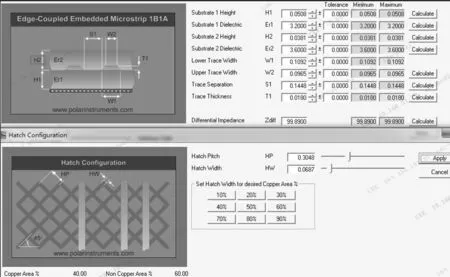

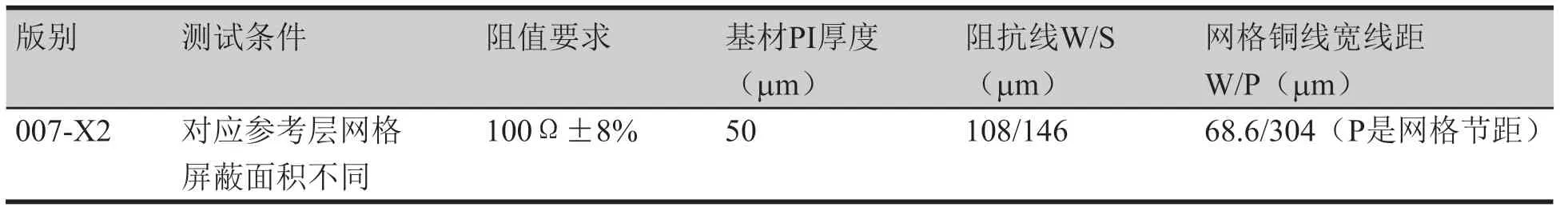

如表4所示测试条件通过软件模拟成品阻值100 Ω,得出阻抗线W/S=108/146 μm,网格W/P=68.6/304 μm。如图6所示模拟图。

图6 SI90000网格阻抗模拟界面图

表4 测试条件表

实验小结:如表5所示的测试数据表明,参考层45°角方形阵列网格对于阻抗线屏蔽位置不同,参考面积存在明显差异,导致阻值波动范围极差11.3 Ω,实际生产当中无法精准管控阻抗稳定性。参考网格对应多组阻抗线贯穿位置不同会导致阻抗线屏蔽面积存在差异,对于阻值的影响较大。

表5 四组相同阻抗线在对应网格屏蔽面积不同时阻值测量结果表

2.3 解决阻抗走线对应网格屏蔽面积不一致问题

为了解决多组阻抗线对应参考层网格屏蔽面积不一致的情况,现在对网格进行重新设计,其他设计要素均不做改变,只把阵列网格改为错位互补网格(如图7所示)。

图7 45°角阵列错位互补网格图

错位互补网格看成由一个个菱形错位组成,把每个方框基材区域做上标识,通过计算得出:1/2/3面积之和等于3/4/5面积之和,且1/3/5面积之和等于2/4/6面积之和。不管阻抗线位置如何变化,面积之和的总值不会改变。多组阻抗设计如图8所示,阻抗线阻值测量结果见表6所示。

图8 45°角互补方形网格图

实验小结:表6中测试数据分析表明,错位互补网格由于网格的互补性,走线贯穿网格时,任意位置网格屏蔽面积均一致,测试成品阻值极差1.1 Ω,阻值波动控制在5%范围内,满足实际产品需求,可实现对刚挠板多组阻抗值的稳定控制。

表6 四组相同W/S阻抗线在网格屏蔽面积相同时测量结果表

3 结论

综上实验结果可以得出,为保证刚挠板的阻抗匹配一致性,在复杂阵列形多对阻抗调试过程中,通过改变参考层网格设计,达到阻抗规格要求及阻值管控稳定性。

在介质性能、线宽等阻抗影响因子受结构及产品应用限制时,错位互补网格设计相比传统的阵列网格,可改善板内阻抗极差偏大现像,降低生产过程中阻抗超差风险,减少客户端电子产品的不良返修概率。