基于数字锁相环的FPGA多通道频率测量系统设计

金 鑫,田文杰,刘 迪,陈福彬

(北京信息科技大学传感器重点实验室,北京 100101)

0 引言

传统的高精度频率计一般电路复杂[1]、灵活性和可升级性较差且通常情况下可测量的通道数较少。随着可编程逻辑器件FPGA的发展,可以将大量逻辑功能的电路集成到FPGA中,增强了频率测量模块的集成度,FPGA构成的电路是现场可升级的,提高了测量模块可维护性[2]。

目前基于FPGA的频率测量通常采用直接测频[3]和等精度测频[4-5]的方法来计量待测信号。这两种测量方法,在遇到对测量时间有特殊要求时,存在各自的缺陷。同时,随着传感器的发展,多通道信号的应用也越来越广泛[6-7],为了确保数据收集的完整性和实时性,需要对多路的频率信号同时进行测量。本文基于数字锁相环[8],设计一种多通道高速的测量方案,通过对自适应数字锁相环模块、数据采集模块和串口通讯模块进行优化开发,实现对被测信号的数据采集和发送。通过实验验证了系统的可靠性,并将该设计应用于集成式石英谐振器的频率采集和测量,有效地提高了数据采集的效率和实时性。

1 频率测量原理及整体结构

频率测量方法有直接测频法、多周期同步测频法、等精度测频法、双混频法等,各种测频方法应用场景及实现方式不同,直接测频法、等精度测频法在FPGA频率测量系统中应用较广泛。直接测频法的工作原理为闸门信号以时钟信号为基准,设置闸门时间为T,在闸门开启的时间内得到被测信号计数结果Xin,则被测信号的频率即为Xin/T。等精度测频法的工作原理为将数个被测信号作为闸门时间的开关,当被测信号计数达到Xin时,测得当前时钟信号的计数为Xs,根据系统时钟信号的频率fs和fx=(Xin/Xs)fs就可以得到被测信号的频率。直接测频法闸门时间较长,测量速度较慢。等精度测频法的闸门时间与被测信号有关,在设置好闸门计数后,测量高频和低频信号所需的时间相差较大。

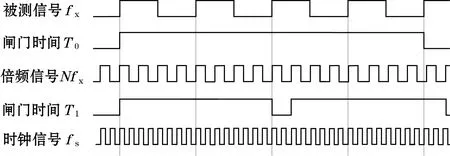

为了应对以上2种测量方法的不足,本文提出了一种新的测量方式。其测量原理是:通过FPGA的数字锁相环对被测信号fx进行倍频调制,得到放大整数倍的倍频信号Nfx。然后通过减少对时钟信号fs的计数,将闸门时间缩小为T1=T0/N。计数模块对倍频信号计数就可以得到与被测信号fx频率相同的值,如图1所示。

图1 采集原理波形图

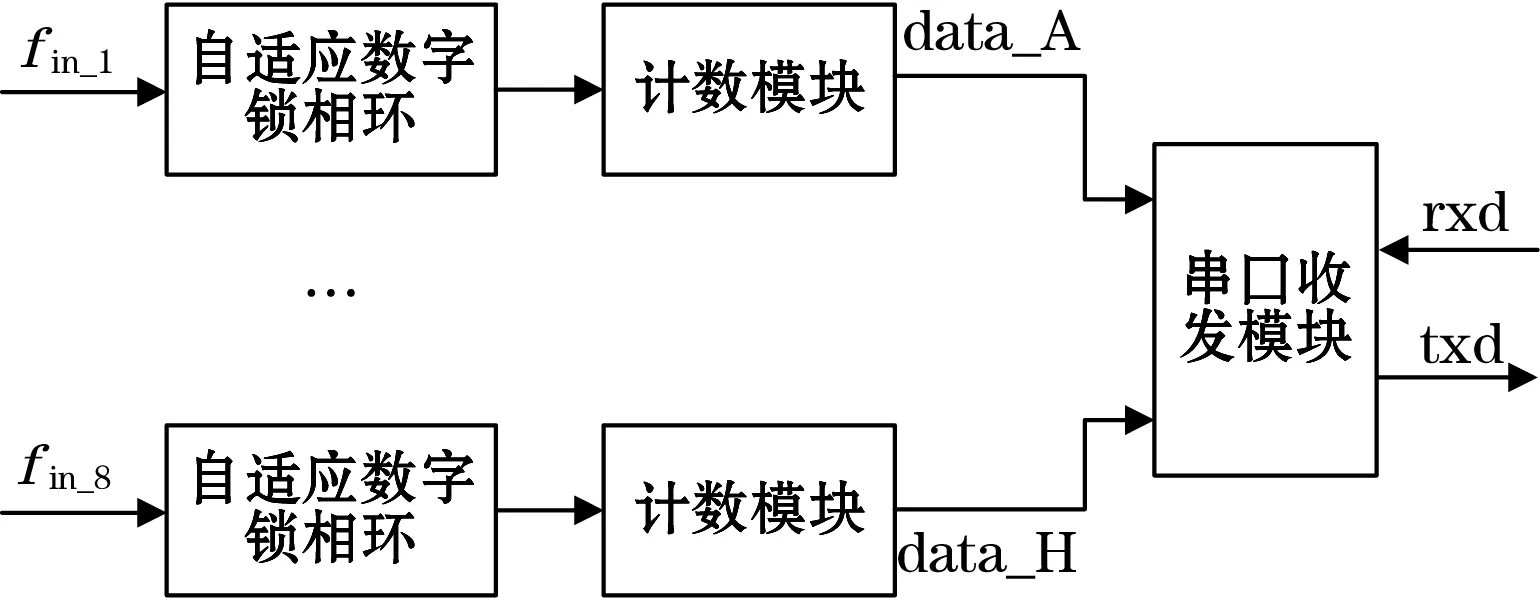

根据上述原理,以FPGA作为信号采集、发送和处理控制系统的核心并结合串口通讯,设计了一种多通道的高响应频率测量系统,框架结构如图2所示。将8路的输入信号基于独立的自适应数字锁模块经倍频处理后得到8路倍频信号,然后通过独立的计数器测得倍频信号的频率值并保存在寄存器中。FPGA通过串口模块输出TTL标准的串口信号,与PC计算机或嵌入式设备进行通讯,并根据读取到的数据帧选取对应通道的频率值,通过串口输出。

图2 系统整体结构框图

2 自适应数字锁相环模块

2.1 数字锁相环模块

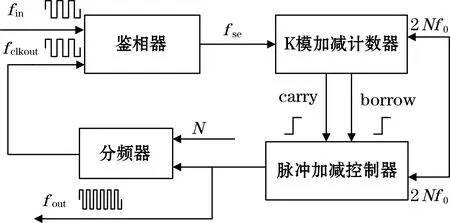

数字锁相环由鉴相器、K模加减计数器、脉冲加减控制器与分频器组成,如图3所示。鉴相器通过输入信号fin和环路反馈信号fclkout进行比较并输出两者的相位差信号fse。然后K模可逆计数器再根据相位差信号的逻辑电平输出进位脉冲carry和退位脉冲borrow,脉冲加减控制器根据进位、退位脉冲对模块时钟的频率进行跟踪和调整,输出生成的倍频信号fout。

图3 数字锁相环原理框图

2.2 自适应时钟模块

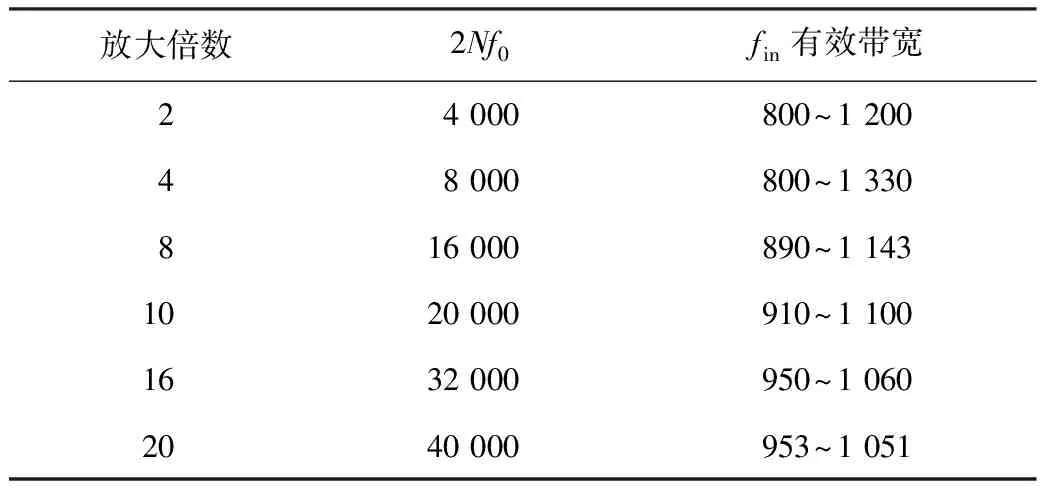

由于数字锁相环模块的输出信号受到2Nf0和fse的影响。在实际应用时,数字锁相环存在一定的工作范围,且放大倍数越大时,其工作范围越小,如表1所示。在2Nf0不变的情况下,若要保证fout=Nfin,fin就必须在有效的带宽范围内。

表1 放大倍数与倍频有效带宽 Hz

从系统整体的性能角度考虑,在一个变化较大的工作频率下工作时,如果数字锁相环采用固定模块时钟2Nf0就不是最优解。所以就需要根据输入信号自适应得到一个数字锁相环所需的模块时钟。自适应时钟模块框架结构如图4所示。

图4 自适应模块结构图

图4中,实验板中的晶振频率为50 MHz,使用FPGA芯片的锁相环IP核ALTPLL把晶振频率倍频到400 MHz作为系统时钟。在输入信号fin的8个周期时间内计量系统时钟的周期数并求其平均值得到n_cnt,然后根据需要放大的倍数N来设置锁存器的范围。随后任意正整数分频器模块根据输入的n_final进行分频得到数字锁相环所需的时钟信号2Nf。

2.3 自适应数字锁相环仿真

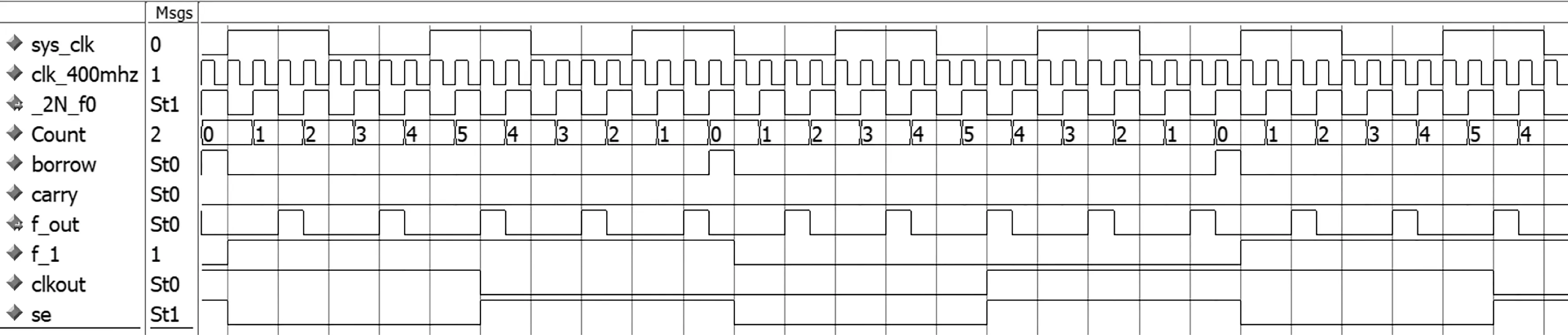

通过自带Altera库的时序模拟软件ModelSim Altera进行仿真验证,可以直观的看到各个节点信号时序图,以及产生的信号是否有效,如图5所示。

图5 自适应锁相环时序图

首先,在TestBench测试文件中对信号进行定时循环翻转生成10 MHz的输入信号和50 MHz的系统时钟信号。然后将生成的信号与自适应数字锁相环模块的输入端进行绑定并运行仿真程序。从图5中看出sys_clk经过ALTPLL倍频后生成了400 MHz的时钟信号clk_ALTPLL。自适应模块根据输入信号f_1生成了自适应模块时钟2N_f0。当前输入信号和分频信号clkout相位差信号se的占空比为50%完成了锁相,此时K模可逆计数器在0~5之间变化,当计数值到0时会产生借位信号borrow的脉冲,受到借位脉冲的影响,脉冲加减控制器产生了频率为输入信号10倍的输出信号f_out。

3 数据采集与输出

3.1 频率采集模块

频率采集模块由8个独立的频率计数模块组成。该模块内部设计了2组计数器,一组计数器对倍频后的400 MHz标准时钟进行计数,另一组计数器对经数字锁相环模块处理后的倍频信号进行计数。以时钟信号的计数值作为本次的闸门信号,完成对标准时钟的计数后输出当前倍频信号的计数值,并将该值保存到8个32位寄存器中。然后清零2个计数器,重新进行下一次测量。每次的测量时间仅为1/N秒,所以对倍频信号进行测量比对原始待测信号的测量速度提升了N倍。由于倍频信号是由400 MHz的时钟经过处理后产生,所以倍频信号的上升沿必然是时钟信号的上升沿,一定程度上消除了对被测信号测量时产生的1周期误差。

3.2 数据输出模块

串口通讯是一种设备间常用的串行通讯方式,因为它简单便捷,大部分电子设备都支持该通讯方式。为了保证数据传输和显示的效率,传统的LCD显示方案难以满足,所以选择串口通讯作为频率测量系统的数据输出方式。

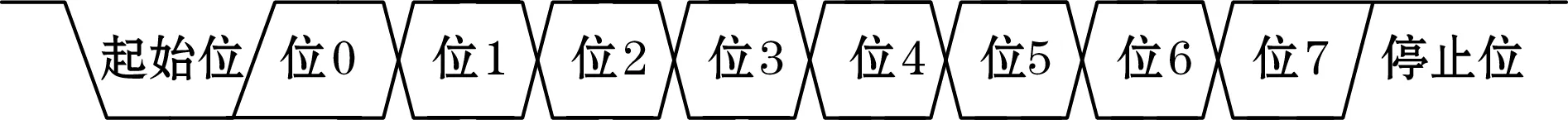

根据串口通讯使用的电平标准,分为TTL、RS-485及RS-232等,在通用的电子器件中,TTL电平的应用非常广泛,选择TTL电平可以减少电平转化电路。本次使用的数据格式如图6所示,采用1位起始位,8位数据位和1位停止位。

图6 数据收发格式图

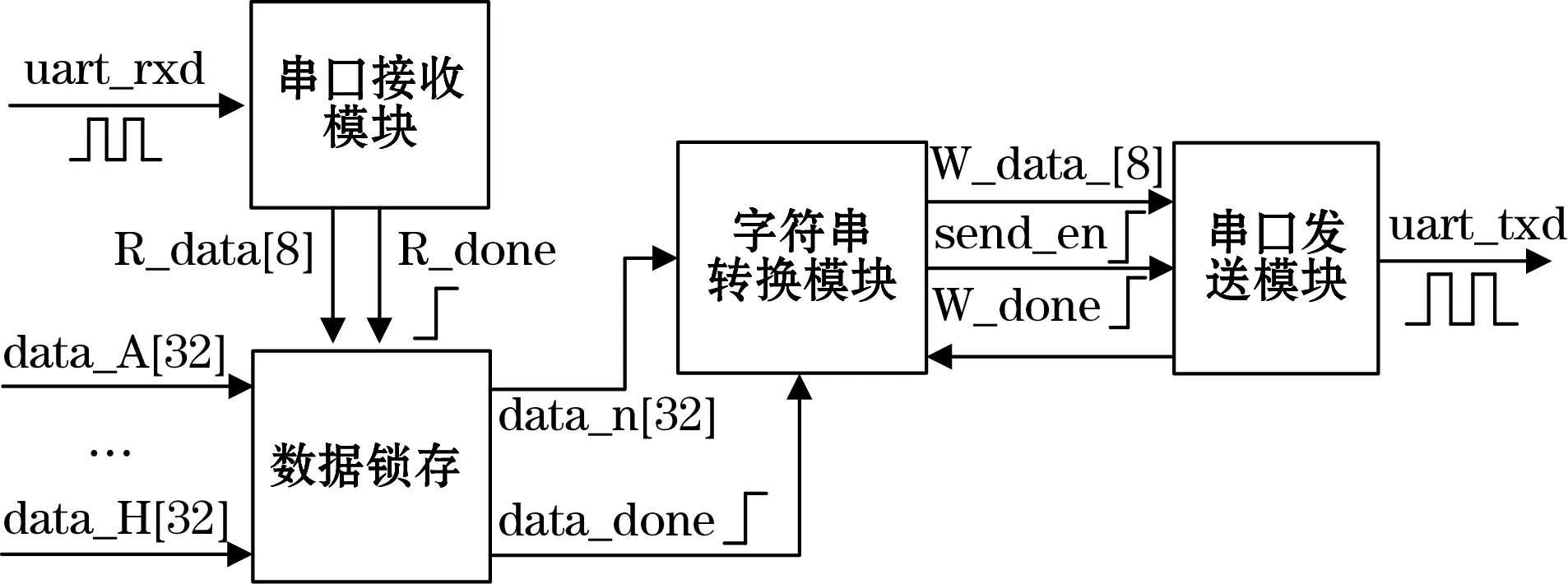

数据输出模块由串口接收模块、数据锁存模块、字符串转换模块和串口发送模块组成,负责接收读取命令和发送频率测量结果,如图7所示。

图7 串口收发结构图

串口接收模块通过接收端uart_rxd接收数据,将8位的串行数据转换成并行数据R_data并传递给数据锁存模块。接收模块在接收到停止位后,向数据锁存模块发送1个完成的脉冲信号R_done。数据锁存模块与频率采集模块中存贮结果的寄存器相连接。在接收到脉冲信号时,根据R_data的值将寄存器中对应通道的频率输出值锁存到data_n中,并向字符串转换模块发送1个脉冲信号。字符串转换模块在接收到脉冲信号后,将32位的频率值分解成4个8位的数据帧,并向串口发送模块发送使能信号send_en和第1个数据帧。串口发送模块接收到发送使能时,将8位数据帧转换成串行信号通过发送端uart_txd发出。在完成1个数据帧的传输后,字符串转换模块会接收到发送模块返回的脉冲信号W_done,随后向串口发送模块发送下一帧的数据和使能信号,直到数据发送完成。

3.3 串口模块测试

串口收发模块的验证需要接收发送串行数据,为了确保该模块能与外界正常的收发数据,所以采用Quartus II中的SignalTap II工具来验证数据输出模块的时序关系。由于系统时钟的信号为50 MHz,为了更便捷地观察输出模块的时序,在模块顶层通过对系统时钟进行处理得到115 200 Hz的时钟信号并在SignalTap中将其绑定为采样时钟。然后再筛选出待观察的信号,并选择接收端uart_rxd的下降沿作为本次测试的唯一触发条件。完成设置后,编译、下载到实验板并运行。

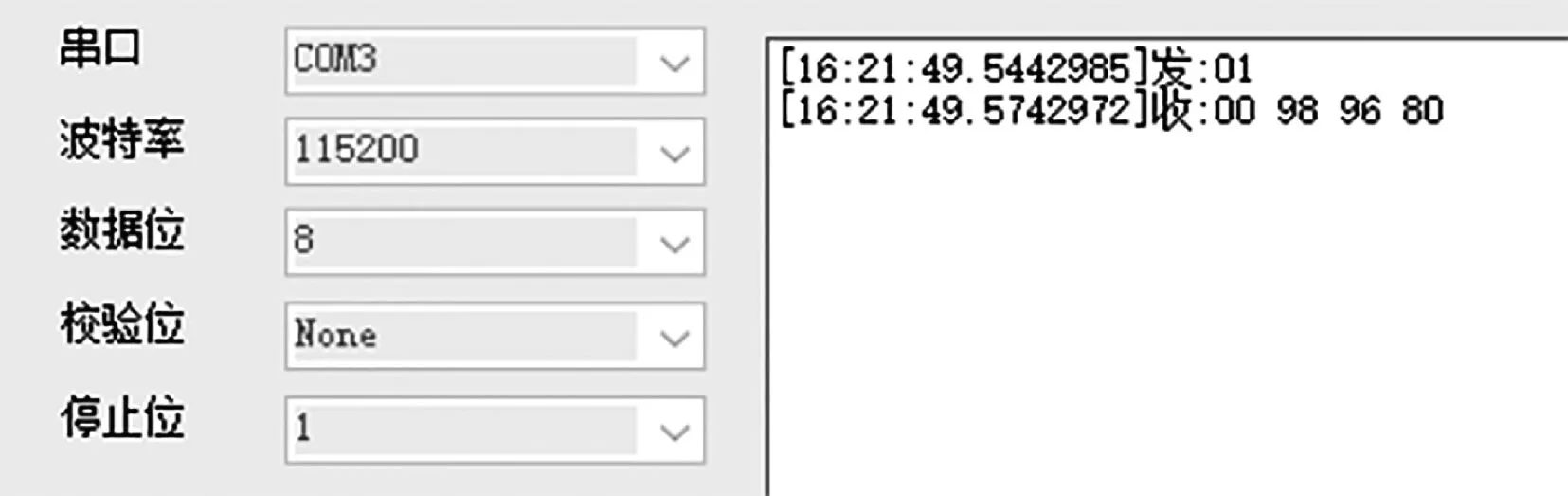

通过USB转TLL转换器将PC计算机与FPGA实验板相连接,在计算机的串口软件中选择对应的COM口,并将波特率设置为115 200 bit/s,数据位设置为8位,校验位设置为None,停止位设置为1,并将显示和发送的数据格式设置为十六进制进行数据接收发送。完成设置后,在发送的文本框中输入第1个通道频率测量值的读取命令“01”并点击发送按钮。此时在SignalTap界面中就可以看到数据的传输,如图8所示。

图8 SignalTap仿真图

图8中,第1个周期是数据的起始位,此时接收端uart_rxd从高电平变为低电平。第2个周期到第9个周期为数据帧的位0到位7,位0为高电平,其他位为低电平,数据为十六进制的“01”。根据接收到的数据判断此时应该发送通道1的频率值data_A。经过字符串转换模块依次输出4个8位data_byte。可以看到图8中,发送端uart_txd的第9到49周期4个数据帧转换成串行信号并输出。测试结果如图9所示,此时计算机上就能收到FPGA的返回值“00 98 96 80”。将其换算成十进制值即为10000000,其值为通道1信号的频率。

图9 串口软件测试图

4 系统测试与应用

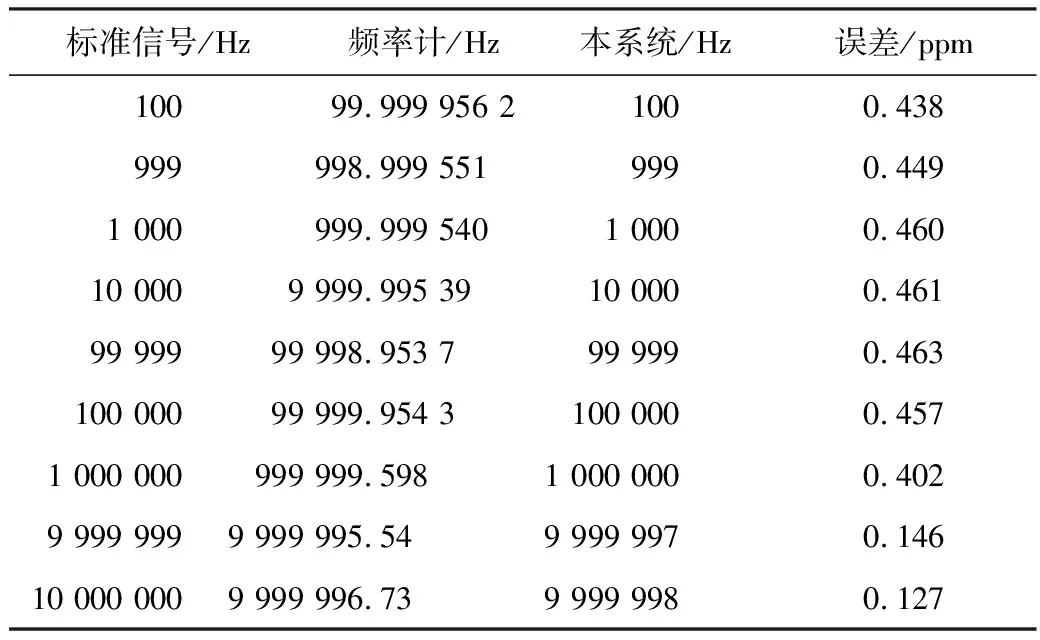

为了检测所设计的多通道频率检测系统的频率测量精度,用KEYSIGHT的33500B信号发生器对Agilent的53132A频率计和本系统进行对比实验。将本系统放大倍数设置为10倍,即每次测量频率的时间为100 ms。对频率为100 Hz~10 MHz、占空比为50%的方波信号进行测试,测试数据如表2所示。

从表2可以看出,在响应时间缩短到100 ms的情况下,本系统的测量灵敏度为1 Hz,与标准频率计53132A的测量结果的相对误差<0.5 ppm。

表2 频率测试数据表

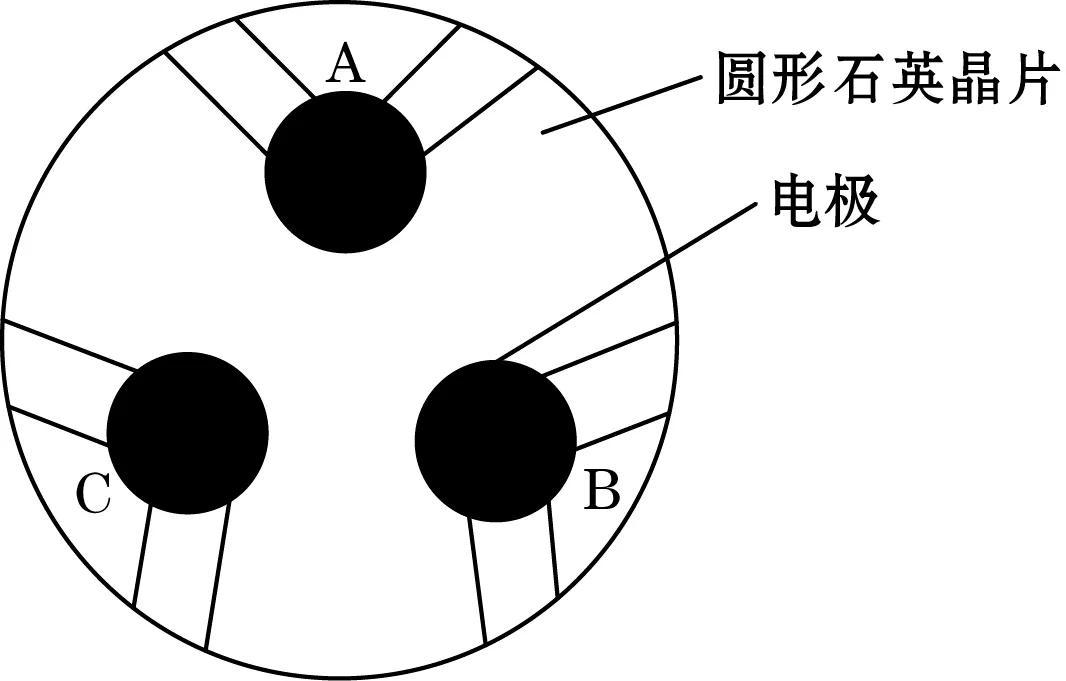

将该系统应用在如图10所示的集成式石英谐振器中来验证测频系统的实际使用价值。集成式石英谐振器是以AT切石英晶片为基片,晶片上含有3个输出正弦信号的谐振器。当受到外力作用后,3个谐振器会出现不同的频率变化,将这3个谐振器的谐振信号经电路互作差频处理,可得到多路差频信号,通过各路差频信号的变化就可以分析集成式石英谐振器的受力情况。根据该现象可将集成式石英谐振器应用在高精度加速度计和姿态测量中。

图10 集成式石英谐振器结构示意图

由于该敏感元件的电极数量较多,测频时若采用硬件电路就需要较多的电子元件,复杂的测频电路会带来噪声且导致信号衰减。采用本文的方案就可以有效地解决测频电路导致的问题,并可以提高测量速度。通过本文设计的系统和标准频率计同时测量集成式石英谐振器的各路差频信号,测试结果如表3所示。

表3 集成式石英谐振器各路差频信号测试表 Hz

由于集成式谐振器激励电路和差频电路存在电路噪声、干扰等因素,导致输出的差频信号占空比会在50%附近波动,所以会导致自适应倍频电路锁相模块中的鉴相器输出抖动,使得测量结果出现偏差,由于差频信号的频率较小,所以与标准频率计相比误差<1 Hz,满足测量需求,同时100 ms就可以采集到3路差频信号,增强了测量的时效性。

5 结束语

本文在已有的测频方式基础上整理优化,设计了基于数字锁相环的FPGA多通道频率检测系统,通过频率计采集模块和串口收发模块将采集部分和传输部分结合,增强了系统的整体性。并通过标准信号发生器和集成式石英谐振器进行了测量实验。实验结果表明,设计的多通道频率检测系统能够在保证稳定和精确的基础上,更快速地采集多个输入信号的频率。在集成式石英谐振器等需要采集多通道频率信号的情况下具有广泛的应用价值。参考文献:

[1] 张新海,雷勇.基于单片机的宽带高精度频率计设计[J].噪声与振动控制,2008,8(4):158-160.

[2] 姜志健,庄建军,陈旭东,等.基于FPGA的高精度频率计的设计与实现[J].电子测量技术,2017(5):41-46.

[3] 丁然,陈金鹰,赵雨.基于FPGA实现简易数字频率计的设计[J].中国集成电路,2012(6):30-33.

[4] 黎山峰,杨雷,孙建军.基于NiosⅡ的FPGA频率计设计与实现[J].仪表技术与传感器,2016(8):105-108.

[5] 徐伟,吴静,杨阳,等.等精度信号参数测量仪设计[J].实验技术与管理,2018(6):100-104.

[6] 刘欢,董浩斌,葛健,等.基于Overhauser效应的磁场梯度探测器[J].仪器仪表学报,2015(3):592-600.

[7] 田文杰,陈福彬,佟盟,等.不同电极数石英谐振器集群力敏特性分析[J].中国惯性技术学报,2019,27(4):516-523.

[8] 李锐,田帆,邓贤君,等.基于FPGA的全数字延时锁相环的设计[J].现代电子技术,2019(6):69-71.