电荷泵锁相环电路建模与仿真

曾兆权,龚立娇,2,李红跃

(1.石河子大学 机械电气工程学院,石河子832000;2.石河子大学 农业农村部西北农业装备重点实验室,石河子832000;3.新疆天富检测有限公司,石河子832000)

锁相环(phase-locked loops,PLL)是利用负反馈控制原理实现频率及相位的控制系统[1]。其作用是将电路输出的信号与其外部的参考信号保持同步,当参考信号的频率或相位发生改变时,锁相环会检测到这种变化,并且通过其内部的反馈系统来调节输出频率,直到两者重新同步锁相。

锁相环的分类具有多样性。按照其实现技术可分为模拟锁相环和数字锁相环[2-5]。按照其反馈回路的特点可分为整数倍分频锁相环(Integer-N PLL)和分数倍分频锁相环(Fractional-N PLL)。按照锁相环鉴频鉴相器的实现方式,可以分为电荷泵锁相环(Charge-Pump PLL)和非电荷泵锁相环。按照其环路的带宽,它可以分为宽带锁相环(Wide band loop PLL)和窄带锁相环(Narrow band loop PLL)[2-5]。

电荷泵锁相环是一种鉴频鉴相器适用于方波输入信号的锁相回路。该类型锁相环的特点是可以快速的锁定到输入信号的相位,达到很低的稳态相位误差[1]。因此,该类型锁相环被广泛地应用于各类型电子设备中,成为音频、视频、通信、导航等各种装置的重要组成部分。

电荷泵锁相环电路具有负反馈闭环系统所具有的系统状态多、工作特性复杂的特点,其设计与仿真分析一直是电子设备时钟系统的难点问题[4-5]。

针对上述问题,本文研究了电荷泵锁相环电路的设计步骤与仿真分析方法。首先,推导电荷泵锁相环各模块的数学模型;其次,建立了各模块电路仿真模型,仿真分析了环路稳定性以及各模块对环路整体性能的影响。研究结果为电荷泵锁相环电路的设计与仿真提供了理论依据,对实际电路设计具有一定参考价值。

1 电荷泵锁相环数学模型

如图1所示,电荷泵锁相环鉴频鉴相器(PFD)、电荷泵(CP)、环路滤波器(LP)、压控振荡器(VCO)以及1/N分频器(Divider)构成。

图1 电荷泵锁相环系统框图Fig.1 Charge pump PLL system diagram

参考信号ϕref与输出信号经过鉴频鉴相器比较得到的两路信号分别控制电荷泵开关S1与S2,根据频率相位比较结果对环路滤波器内电容C1与C2进行充放电进而改变VCTRL的大小,控制VCO 产生和输入参考信号同频率同相位的输出信号。

1.1 鉴频鉴相器与电荷泵

鉴频鉴相器是电荷泵锁相环输入信号所进入的第一个模块,它将锁相环输出信号与输入参考信号进行频率相位比较得到控制信号。如图2所示,电荷泵锁相环的鉴频鉴相器由2 个D 触发器以及1个与门组成。其中,REF 为输入参考时钟信号,DIV是经由分频器进行1/N降频后反馈至鉴频鉴相器的时钟信号。当REF 领先于DIV 时,UP 端输出高电平,DN 输出低电平;当DIV 领先于REF 时,UP 输出低电平,DN 输出高电平。PFD 的作用是输出一个和REF 与DIV 之间相位差成线性关系的电压误差信号E(t),即:

图2 电荷泵锁相环鉴频鉴相器Fig.2 Charge pump PLL PFD

式中:KPD是PFD 增益;Φref(s)是参考时钟相位;ΦDiv(s)是随时间变化的反馈时钟信号相位。需要特别说明的是,E(s)与Φref(s)-ΦDiv(s)之间的关系严格意义上说是非线性的。当Φref(s)-ΦDiv(s)=2π 时(REF 领先DIV 一个周期),E(t)的平均值为1;当时Φref(s)-ΦDiv(s)=-2π(REF 落后DIV 一个周期),E(t)的平均值为-1。Φref(s)-ΦDiv(s)介于[-2π,2π]之间时,可以近似地认为Φref(s)-ΦDiv(s)与E(t)的关系是线性的,即式(1)E(s)≈KPD(Φref(s)-ΦDiv(s))。如上所述,可得到PFD 传输函数为

为了将PFD 所产生的相位误差信号E(s)(数字逻辑信号)转化成能控制压控振荡器工作的电压信号(模拟信号),需要在PFD 与VCO 之间加入滤波模块。PFD 的输出E(s)直接输出给电荷泵,电荷泵再给后续电阻电容滤波网络(C1,C2,R)进行充放电(积分),实现逻辑量到模拟量的转换。对于相位量而言,电荷泵(不包括后续的环路滤波器电容)仅作为一个增益模块,提供一个值为ICP大小的增益。因此,PFD 与电流泵相结合的总传输函数为

1.2 环路滤波器

如图2所示,环路滤波器由旁路电容C1和RC滤波器R,C2构成,根据电阻电容串并联计算方法,环路滤波器的S域传输函数为

1.3 压控振荡器

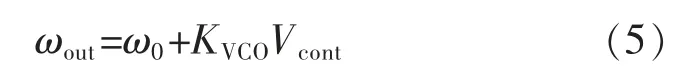

理想的VCO 输出一个周期振荡的信号,且该周期信号的频率ωout与输入控制电压Vcont成线性关系,即:

式中:ω0是VCO 的固有频率,即VCO 输入控制电压为0 V 时输出信号的频率;KVCO是VCO 增益,其单位为rad/s·v-1。VCO 作为一个线性时不变系统,控制电压Vcont作为系统的输入,固有频率成分信号所对应相位之外输出信号的相位Φout(t)作为系统的输出。因此,对Vcont在时间上积分可以得到:

由1.1 节可知,Vcont是由PFD 产生,经过环路滤波器滤波后的控制电压信号,也与频率ω 和相位有关,因此,对式(6)两边同时做拉普拉斯变化,根据拉普拉斯变换在时域积分的性质得到VCO 的传输函数为

1.4 分频器

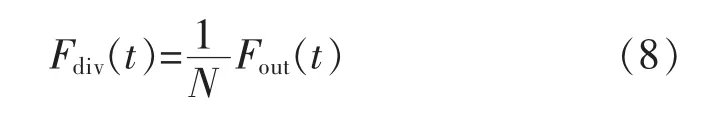

分频器的功能是将VCO 的输出信号频率降为其原有频率的1/N,再反馈给PFD。

分频器本质上是一个计数器(counter),即计数到N后触发产生一个脉冲。N为分频倍数,即输出频率为输入频率的1/N,本文中N为一个正整数。Out(t)为VCO 的输出信号,分频器的输入信号,Div(t)为分频器的输出信号。

分频器的输入与输出频率在时域上满足以下关系:

式中:Fdiv为分频器的输出频率;Fout为VCO 的输出信号频率。对式(8)两端在时域上进行积分可得到分频器输入与输出相位的关系为

因为分频器是对输入频率和相位进行一个1/N的变换,因此,在S域上分频器的传输函数为

1.5 环路增益与相位裕度

由式(3)、式(4)、式(7)和式(10)可以得到电荷泵锁相环的环路增益(Loop Gain)为

进一步根据反馈系统闭环增益的定义可得到电流泵锁相环的闭环增益为

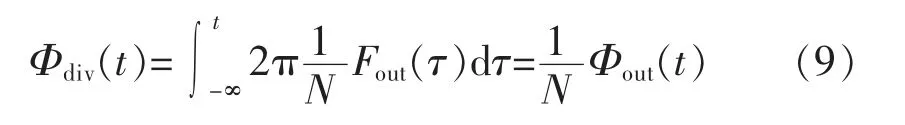

由式(11)可知,电荷泵锁相环共有3 个极点和1 个零点[6]。令式(11)分子为0,求得零点频率为;令式(11)分母为0,求得两极点频率为0,即ωp1,p2=0。第3 个极点的频率为。因此,可以得到电荷泵锁相环幅频相频特性波特图,如图3所示。其中,ωz为零点频率;ωUGB为单位增益带宽频率,即环路增益为0 dB 时所对应的频率;ωp3为第3 个极点的频率;ΦM为相位裕度。

图3 电荷泵锁相环幅频相频特性波特图Fig.3 Bode diagram of charge pump PLL

由式(11)可知电荷泵锁相环有2 个频率为0的极点,再根据波特图的性质,这2 个直流极点使得环路增益从0 Hz 开始以-40 dB/dec 的速度下降(如图3),直至经过第一个零点频率ωz。同样根据波特图的性质,这两个直流极点使得环路相位从-180°开始(如图3)。零点(ωz)可以在幅频上贡献+20 dB/dec,在相频上贡献+90°,使得幅频和相频特性曲线上翘。第3 个极点在幅频上贡献-20 dB/dec,在相频上贡献-90°,再次使幅频特性曲线以-40 dB/dec 下降,相频特性曲线再下移90°[6]。观察图3 可知,为了使电荷泵锁相环这个三阶系统稳定,第3 个极点的频率ωp3必须高于单位增益带宽频率ωUGB。

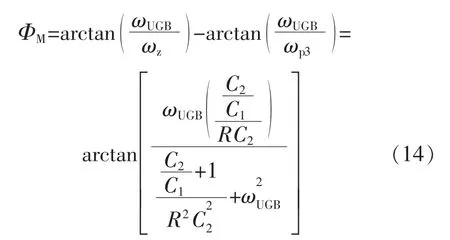

根据波特图相位图的定义以及相位裕度的定义,可以得到电荷泵锁相环的相位裕度(phase margin,PM)为

式中:第1 项-π 是由2 个直流极点所引入的相位偏移;第2 项是由零点ωz引入的正相位偏移;第3 项是由第3 个极点ωp3引入的负相位偏移;最后一项-(-π)则是相位裕度的定义规定的。根据三角函数的性质arctanA-,式(13)可以进一步展开为

对式(14)中ωUGB求一阶导数,并令其为0 可得到:

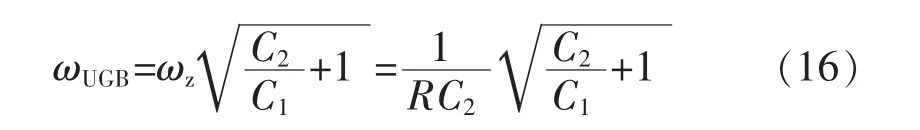

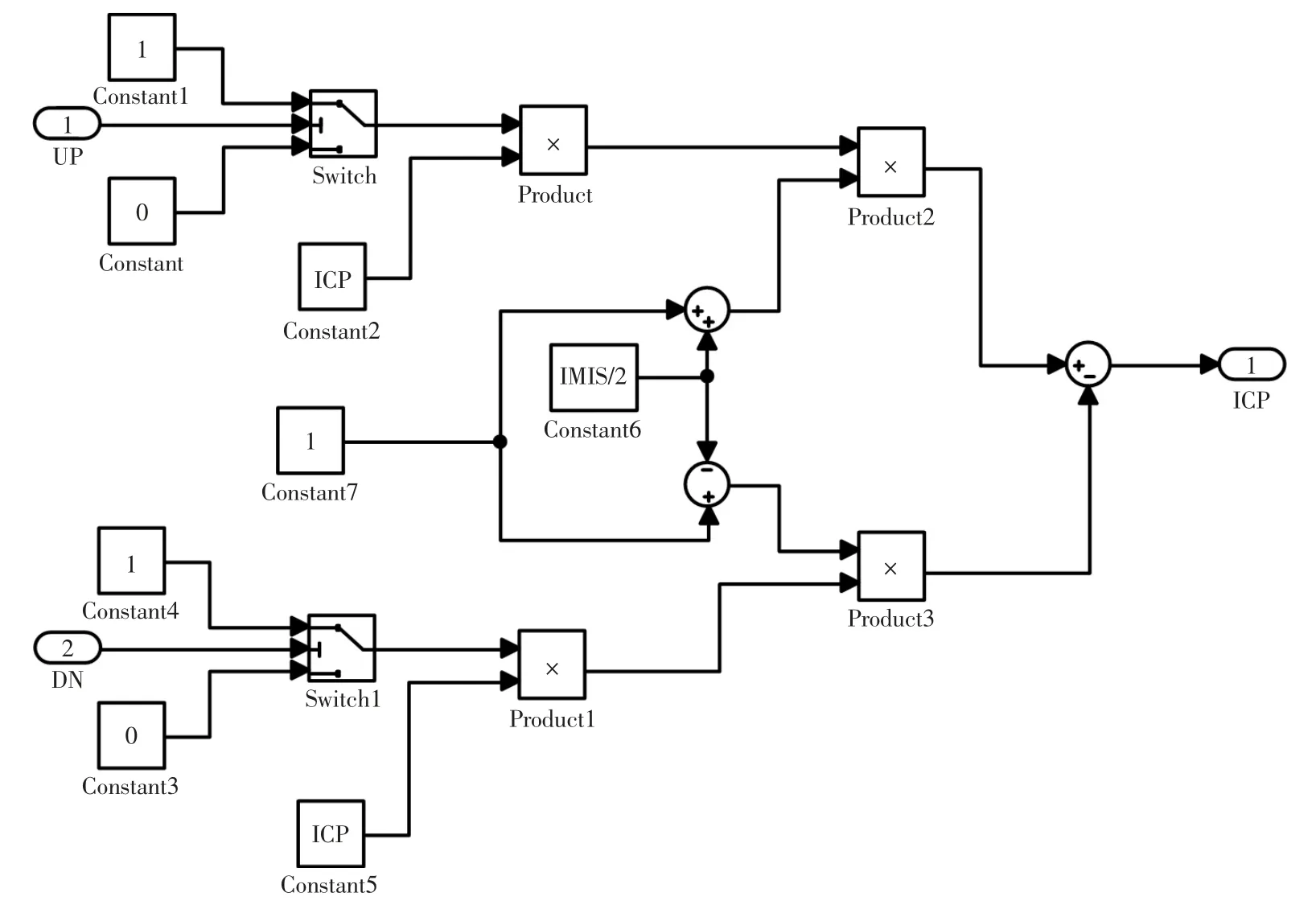

求解式(15)可得到相位裕度ΦM最大时所对应的单位带宽增益ωUGB为

将式(16)代入式(14)中,可得到最大相位裕度为

进一步可得到和的关系为

至此,若给定单位增益带宽ωUGB和相位裕度ΦM,以及N和KVCO,即可通过式(11)、式(16)、式(17)和式(18)求得R,C1,C2以及Icp的值。

1.6 电荷泵锁相环设计步骤

用于某高保真数字音频系统时钟的电荷泵锁相环参数如表1所示。

表1 高保真数字音频系统电荷泵锁相环参数Tab.1 Parameters of charge pump PLL in high-fidelity digital audio applications

根据第1.5 节所推导的电荷泵锁相环数学模型来计算参数N,R,C1,C2使得电荷泵满足设计要求且稳定,设计计算步骤总结如下:

步骤1计算分频器倍数=16。

步骤2单位增益带宽频率ωUGB一般为锁相环输入参考频率Fref的1/20。因此可得。

步骤3由图3 可知,电荷泵锁相环的相位裕度ΦM主要受位于原点的2 个直流极点以及1 个零点所影响。为简化计算过程,忽略图3 中第3 个高频极点的影响,因此式(14)可简化为

步骤4电容C1主要用于滤除电荷泵输出电压的细小波纹,对整个环路的稳定性影响较小。因此,为了简化计算过程,可以暂时忽略C1。式(11)中锁相环环路增益可简化为进一步对式(20)取模可得

将ωUGB=2π·2 MHz,ICP=100 μA,KVCO=626 MHz/V及RC2的值代入,可得R≈2.8 kΩ。

步骤5将式(21)中结果代入式(18)可以得。

步骤6由式(18)计算可得C1的值选择约为C2的1/10,即C1=0.1,C2=5 pF。

至此,一个三阶电荷泵锁相环电路的系统设计完成。

2 电荷泵锁相环计算机建模与仿真

按照上文推导电荷泵锁相环数学模型所搭建的电流泵锁相环Simulink 仿真模型,如图4所示,由脉冲产生器、鉴频鉴相器(PFD)、电流泵(CP)、环路滤波(LPF)、压控振荡器(VCO)、示波器、反馈回路分频器组成。其中仿真模型中的参数与表1所示参数值相同。

图4 电荷泵锁相环Simulink 仿真模型Fig.4 Simulink model of charge pump PLL

2.1 鉴频鉴相器仿真模型

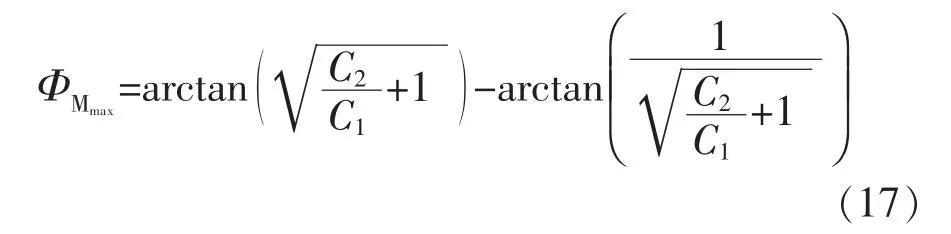

鉴频鉴相器Simulink 仿真模型如图5所示。由2 个D 触发器(D Flip-Flop)和1 个与非门(NAND)以及1 个记忆单元(Memory)构成。其中CKREF 为参考时钟信号,CKFB 为经过分频器输出的反馈时钟信号,记忆单元用于模拟鉴频鉴相器环路的延迟。

图5 鉴频鉴相器Simulink 仿真模型Fig.5 Simulink model of PFD

2.2 电荷泵仿真模型

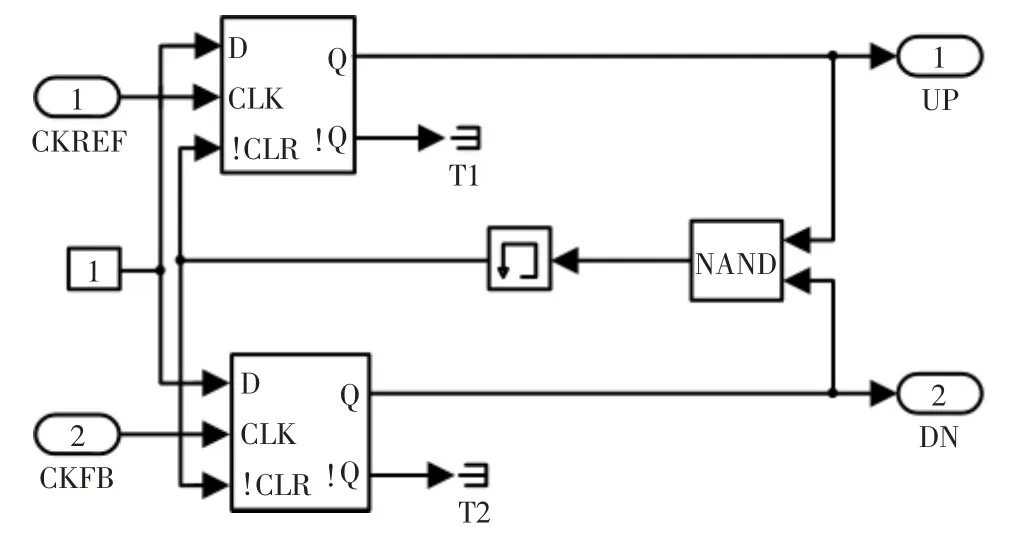

电荷泵Simulink 仿真模型如图6所示,由加法器、减法器、二选一开关(Switch)、乘法器(Product)构成。其中Constants 为Simulink 中的常数模块,常数ICP 代表电荷泵的电流值(Icp=100 μA),IMIS 代表电荷泵的失配参数,理想状况下IMIS值为0。

图6 电荷泵Simulink 仿真模型Fig.6 Simulink model of charge pump

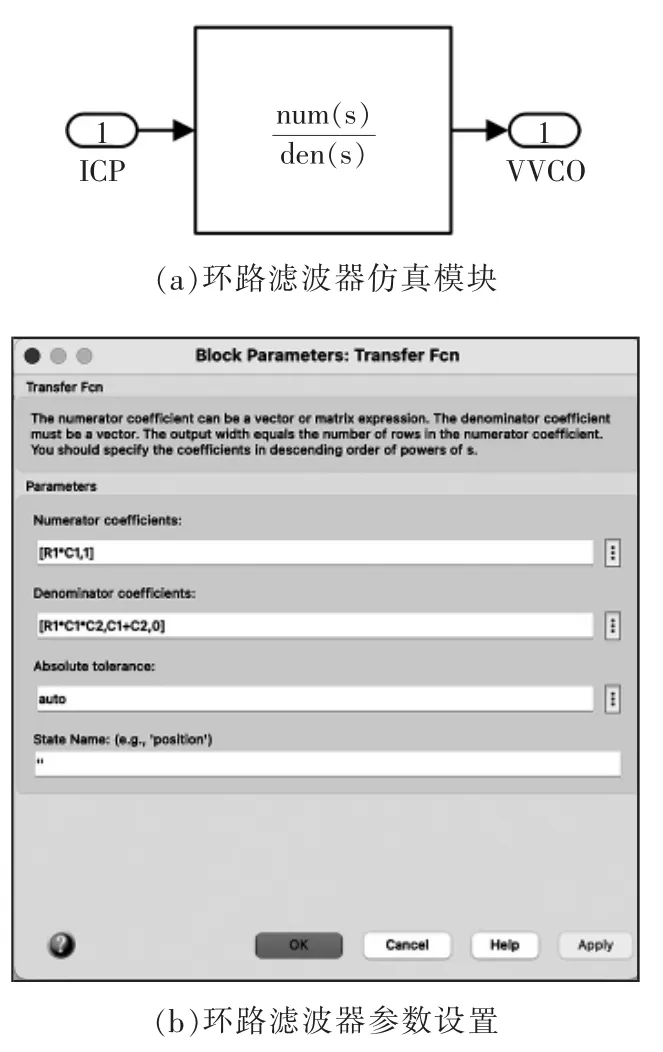

2.3 环路滤波器Simulink 仿真模型

环路滤波器Simulink 仿真模型如图7所示,采用Simulink 中的传输函数模块(Transfer Function),传输函数与式(4)相同,数值与1.6 节中步骤4~步骤6 所得到数值相同。

图7 环路滤波器Simulink 仿真模型Fig.7 Simulink model of loop filter

2.4 压控振荡器仿真模型

压控振荡器仿真模型如图8所示,其中常数VTH 为VCO 的开启电压(Turn-on Voltage),一般设置为中值电压的一半,在此即为0.75 V。增益Gain为VCO 增益KVCO=626 MHz/V,常数Fint为VCO 的空跑频率即中值自由震荡频率,由表1 可知为450 MHz,增益Gain2 为VCO 运行电压的一半,即1.5 V。输入给VCO 的电压信号VVCO首先减去VTH 判断是否达到开启电压,随后乘以VCO 增益,再加上Fint得到VCO 运行频率。运行频率再通过增益Gain1,积分器(Integrator),以及正弦波产生函数(Trigonometric Function)转变为VCO 运行频率所对应的正弦信号,之后通过量化模块(Sign)和增益Gain2 转变为方波输出VCOCLK。在此过程中,FVCO 为VCO 输出信号的频率信息,VCOFB 为输出给分频器模块的VCO 输出相位信号。

图8 压控振荡器仿真模型Fig.8 Simulink model of VCO

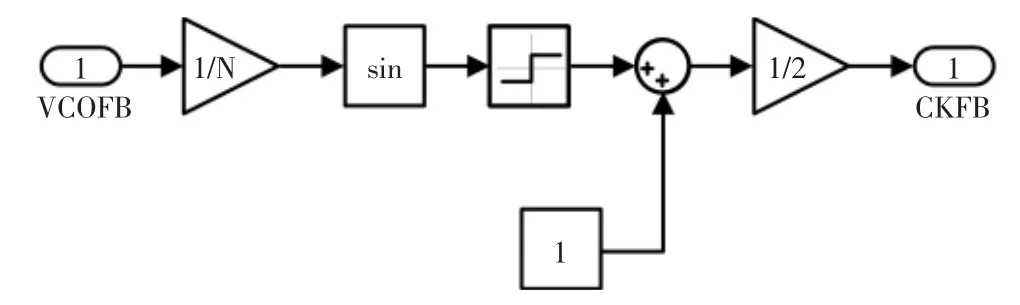

2.5 反馈回路分频器仿真模型

分频器Simulink 仿真模型如图9所示,VCO 输出的相位信号VCOFB 首先除以分频倍数N=16,随后通过正弦波发生模块(sin)和量化模块以及1/2 增益模块转变为输出方波时钟信号CKFB。

图9 分频器Simulink 仿真模型Fig.9 Simulink model of frequency divider

3 仿真结果

如图10所示,电荷泵锁相环环路滤波器输出信号在初始1.5 μs 左右稳定,表明锁相环环路达到锁定状态。

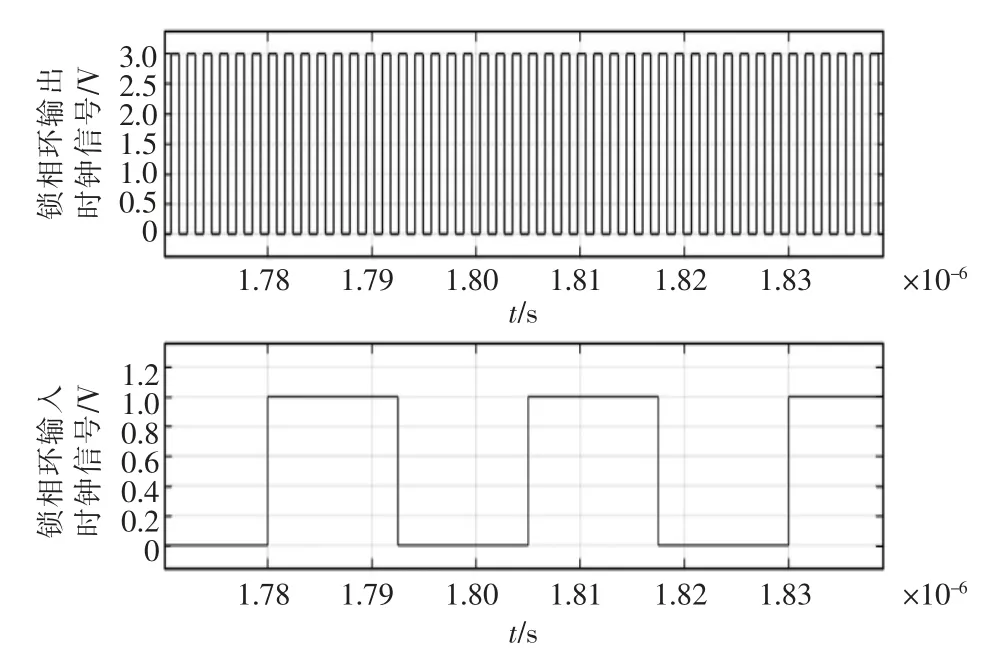

如图11所示,经测量锁定后电荷泵锁相环输出时钟信号的周期约为1.56 ns,即输出时钟频率为640 MHz,与预期设计指标相吻合,表明电荷泵锁相环达到设计要求。

图11 锁定后电荷泵锁相环输出时钟信号与环路滤波输出信号Fig.11 Locked output of charge pump PLL and loop filter

如图12所示,电荷泵锁相环输出信号频率是输入信号频率的16 倍,即输入信号频率40 MHz,输出时钟频率640 MHz。

图12 电荷泵锁相环输出时钟信号与输入时钟信号对比Fig.12 Comparison of charge pump PLL output and input clock signal

4 结语

电荷泵锁相环电路的设计与仿真分析是电子设备时钟系统的重难点。本文针对典型电荷泵锁相环,推导了其各模块以及整体系统的数学模型,在此基础上,建立了各模块电路仿真模型,最后仿真验证了环路稳定性。仿真证明了所建立电荷泵锁相环数学模型的正确性,对电荷泵锁相环实际电路设计具有一定参考价值。