多通道波特率自适应CAN总线监测系统

何 鑫,张会新,刘文怡,熊继军,洪应平

(中北大学,仪器科学与动态测试教育部重点实验室,山西太原 030051)

0 引言

随着信息技术、人工智能技术、传感器技术的发展,无人机机载电子设备及传感器的数量也越来越多[1-3]。为了降低布线的复杂性,无人机机载设备与传感器一般采用现场总线进行通信,CAN总线是其中一种[4]。同时,为了保证通信的可靠性,使用多个CAN总线进行冗余通信,且不同数据量的设备使用不同波特率通信[5-6]。为了在飞行任务结束后能对飞行器各设备工作情况进行分析,需要对总线上的数据进行监控与记录[7]。现有的数据记录器一般只能对单个CAN总线进行数据采集及记录,且通信波特率由内部程序固化,不能对通信波特率进行自动适配,不满足无人机的多通道、多波特率数据记录要求。

针对以上问题,设计了一种具有自动波特率的多通道CAN总线实时监测系统,该系统能够自动识别总线通信波特率,并记录通信数据。在无人机飞行完毕后,可读取内部记录的数据重新转化为有效信息,为无人机的飞行状况、故障信息分析提供数据。

1 总体方案设计

如图1所示,系统采用模块化设计,可降低系统设计的复杂度[8-9]。系统包括电源模块、FPGA控制模块,以太网通信模块、CAN监视模块、数据存储模块,计算机及数据解算上位机软件为额外部分。系统上电后,首先对FLASH进行坏块的检测与标记,同时查找上次数据存储记录,将数据写指针偏移至空白地址,确保已存储的数据不会被新数据覆盖。CAN总线监视模块采集到的数据经过FPGA的封包处理后,冗余存储到FLASH中。使用W5300实现以太网接口,计算机可通过以太网总线直接与记录器进行通信,完成数据的读取以及相关参数的设置工作,无需通过测试台中转。

图1 系统整体框图

2 硬件设计

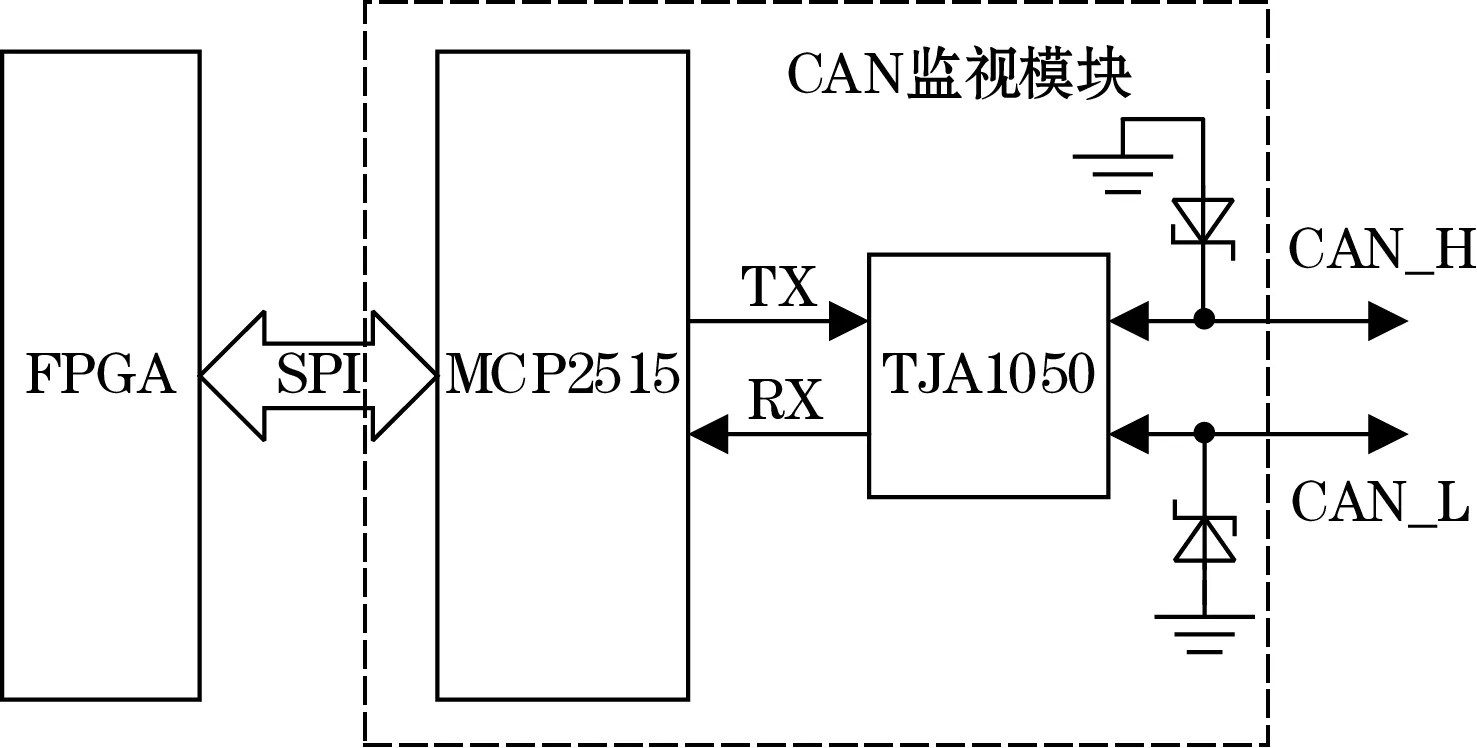

2.1 CAN总线监视模块

CAN监视模块能够实时监控4路总线通信数据,支持的通信速率最高可达1 Mbit/s。同时内部留有扩展接口,支持对CAN总线进行通道扩展,理论可扩展总线通道数只受系统资源限制。如图2所示,使用MCP2515作为CAN总线控制器,该芯片是独立的CAN协议控制器,完全支持CAN2.0B标准,FPGA通过SPI总线实现对该芯片的控制,操作简单可靠。CAN收发器使用TJA1050。考虑到无人机内部总线挂载设备较多,以及机舱内部的电气复杂性、记录器自身的稳定性等,同时为了提高系统的EMC性能,使用TVS二极管并接在CAN_H、CAN_L与GND上。当外界干扰信号超过TVS二极管的击穿电压时,二极管将处于钳位状态,将电压限制在一个安全范围,保护电路不受损坏[10]。

图2 CAN总线监视模块功能原理图

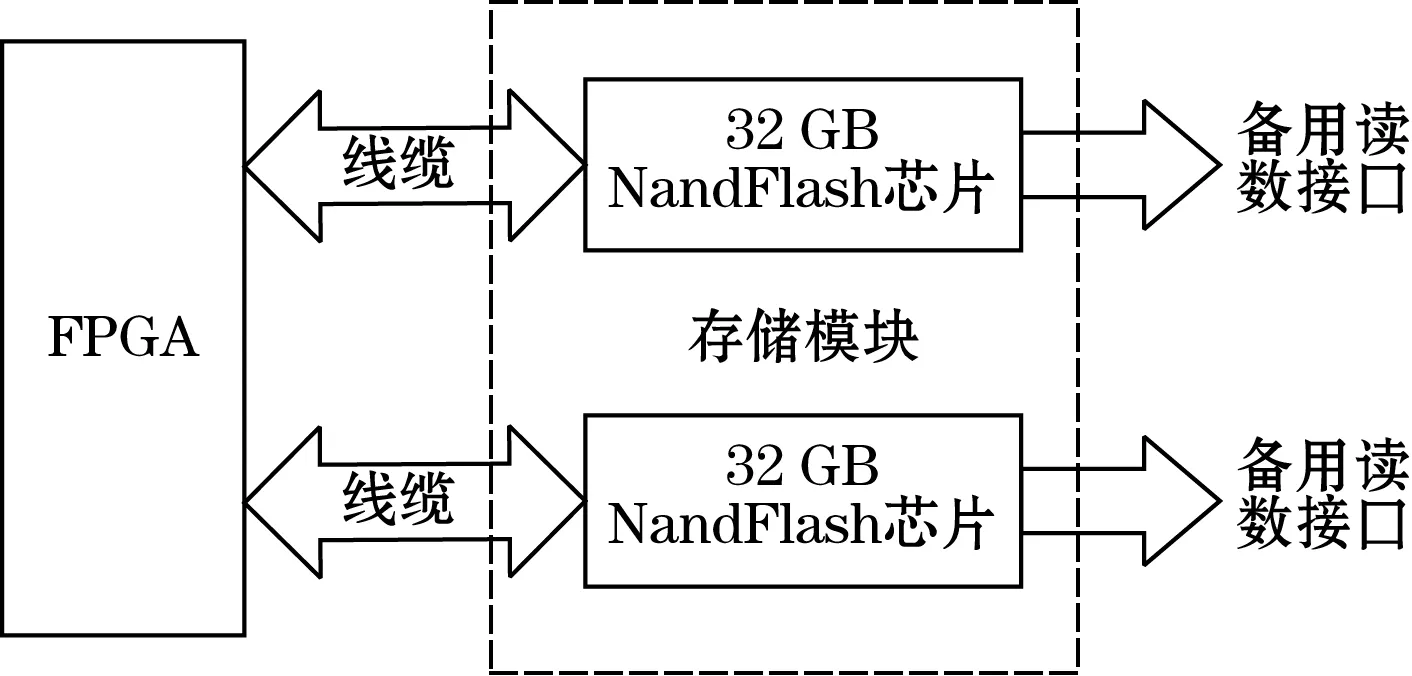

2.2 数据存储模块

现有无人机的滞空时间一般为几h至十几h[11-12]。按16 h滞空时间、四通道CAN波特率1 Mbit/s、带宽利用率60%计算,则所需存储容量为:16 h×4×1 Mbit/s×60%÷8 bit=16.875 GB,因此,数据存储模块选用容量大小为32 GB的NandFlash芯片,可满足无人机不小于16 h的数据记录要求。为保证在意外情况下也能正常回读数据,该部分独立于数据采集模块,使用单独的存储小板设计,放置于抗高过载的合金钢小桶内,仅使用线缆与采集控制模块相连,并设计有备用读数接口,当线缆损坏时可通过备用接口读取数据。图3为存储小板电路逻辑图。

图3 存储模块功能原理图

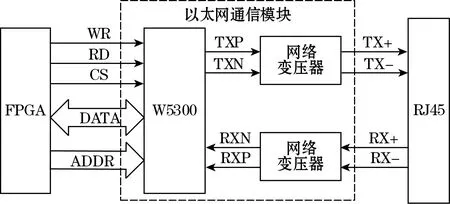

2.3 以太网通信模块

系统使用以太网总线与计算机进行数据传输。接口芯片使用W5300,该芯片内部集成TCP/IP协议和10/100 M的以太网MAC和PHY,支持全硬件通信协议技术,如TCP、UDP、IPv4、ICMP、IGMP、ARP等,其内置通信数据存储器高达128 KB字节,极大程度降低了主控器件对存在资源的需求。如图4所示,W5300使用并口方式与FPGA进行连接,数据线宽度为16 bit,地址位宽度为10 bit,配合WR(写使能)、RD(读使能)、CS(片选信号)对W5300内部寄存器的读写操作,完成数据收发操作。

图4 以太网模块原理图

3 系统逻辑设计

3.1 CAN波特率自适应

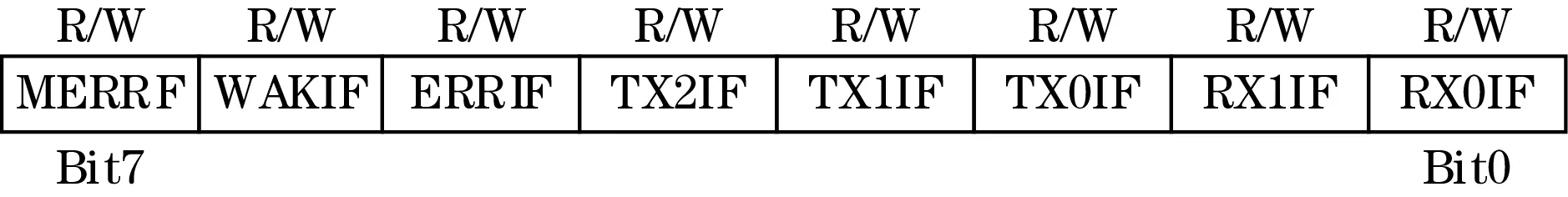

MCP2515是独立的CAN控制器芯片,共有5种工作模式:配置模式、正常模式、休眠模式、仅监听模式、环回模式。控制器具有8个中断源,CANINTF是中断标志寄存器,如图5所示。

图5 CANINTF中断标志寄存器

当中断被使能且有中断发生时,相应的标志位会被置位,通过读取该寄存器的值可判断出中断类型。Bit7为报文错误中断标志位,如果在报文发送或者接收过程中有错误发生,将触发报文错误中断,同时该标志位被置位。Bit0为接收缓冲器0满中断标志,收到正确报文时该标志位将被置位。设计中使用仅监听模式,配合报文错误中断、接收缓冲器0满中断实现CAN波特率的自适应功能。

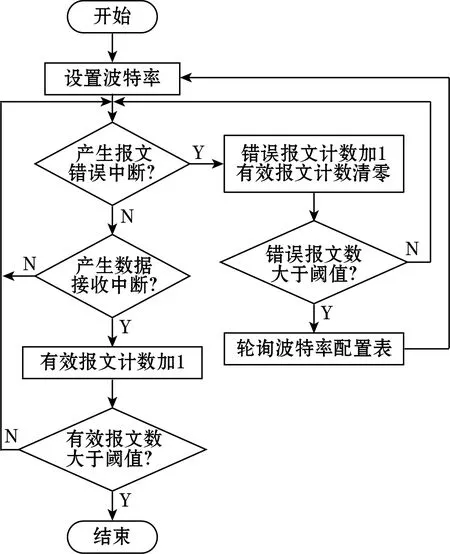

波特率自适应流程如图6所示,在自适应阶段,系统不断读取CANINTF中断寄存器,并对寄存器的值进行判断。如果有报文错误中断发生,则说明可能波特率有误,报文错误中断计数器加1,当报文错误中断计数器值大于设定的阈值时,轮询波特率查找表,重新对波特率进行配置;如果无报文错误中断发生,同时有报文接收中断发生,则说明接收到的报文极大概率为正确报文,正确报文中断计数器加1,当正确报文中断计数器值大于设定的阈值时,说明当前设置的波特率值是正确的,波特率自适应结束。

图6 自动波特率识别流程图

3.2 CAN数据采集

数据采集使用MCP2515的仅监听模式,在该模式下,芯片不会发送任何报文,包括错误标志或者确认信号,此模式能将记录器对总线的影响降到最低。

当MCP2515监听到CAN总线上有数据时,其内部状态寄存器的接收中断标志位会被置位,FPGA通过查询该标志位即可知道数据的接收状态。当有数据被缓存到芯片的内部缓冲器时,使用读RX缓冲器指令快速将数据读取到FPGA内部。相对于普通的数据读取指令,该指令只需发送一次便可以完成数据读取功能,而普通指令则需要间断读取14个寄存器,数据读取更快速,系统实时性更高。

3.3 数据存储

系统采集的数据以帧头、CAN通道、帧记数、帧长、CAN数据、帧校验的形式将数据打包,写入到数据缓存FIFO中。帧校验为和校验,计算方式为除校验位自身外所有数据的字节和,取低8位,用于校验数据的正确性。

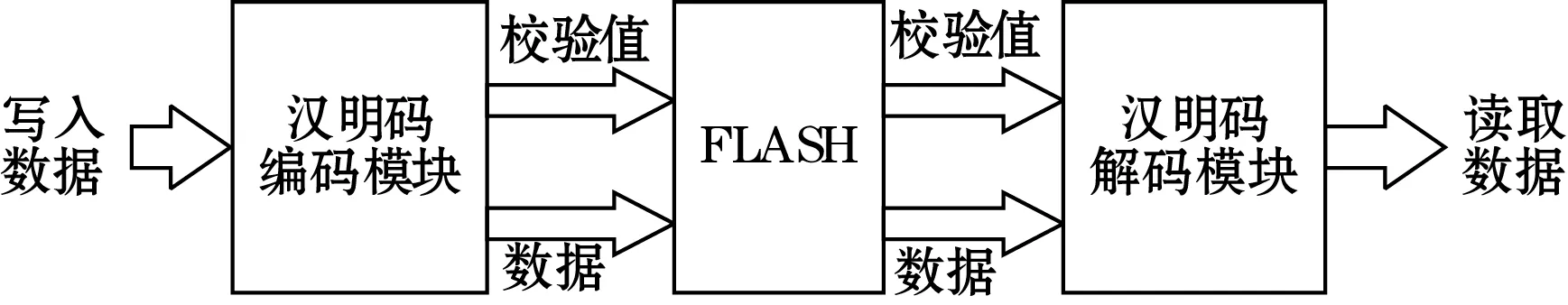

另外,由于电磁干扰的存在,数据在写入、读取或者存储的过程中都可能出现位翻转的情况,从而导致数据出现错误[13-14]。虽然数据有帧校验,但本设计中采用的和校验方式、普通的奇偶校验方式,都只能检查出数据是否有发生错误,不能确定是数据中的哪一位发生错误,也就不能对错误进行修正。因此,为了最大限度确保存储数据的正确性,设计中引入了错误检查和纠正技术(ECC),并在FPGA中实现了基于汉明码(hamming code)的ECC纠错算法。汉明码是一类线性纠错码,最多可以检测2位错误或者纠正1位数据错误[15]。如图7所示,数据在写入FLASH中前,使用汉明码对数据进行编码,将编码得到的校验值写入FLASH芯片的spare area区域。读取数据时,使用读取的数据计算新校验值并与读取的校验值对比。若新计算的校验值与读取的校验值不一致,则说明有数据位发生错误,使用特定算法对2个校验值进行计算即可确定发生错误的数据位,对该位进行取反即可得到正确的数据。

图7 数据存储流程图

3.4 数据读取

计算机通过以太网总线直接读取数据,上位机作为TCP服务器,而记录器作为TCP客户端。上电后,记录器主动寻找服务器并建立链接。在进行数据的传输之前,需要先对W5300进行复位,并配置相关寄存器。复位需要先拉低RST引脚至少2 μs,然后拉高该引脚并等待至少10 ms,直到其内部PLL时钟锁定完成。寄存器配置需要设置TCP服务器IP地址、通信端口、本机IP地址及MAC地址,同时为通信SOCKET分配TX/RX内存空间。由于需要配置的寄存器较多,因此事先将寄存器值写入查找表中,配置寄存器时只需要从查找表读取相应寄存器的值并写入W5300内部寄存器即可。当寄存器配置完成并且TCP链接建立成功后,上位机可发送指令读取数据并保存至计算机。

4 实验结果与分析

本文使用具有多路CAN总线的测试台对系统进行测试,如图8所示。由测试台内部生成多路不同波特率信号源,发送周期为10 ms的递增数。其中通道1波特率为100 Kpbs,标准远程帧;通道2波特率为125 Kbps,标准数据帧;通道3波特率为250 Kbps,扩展数据帧;通道4波特率为1 Mbps,扩展远程帧,数据记录时长为16 h。

图8 多路CAN总线测试台上位机

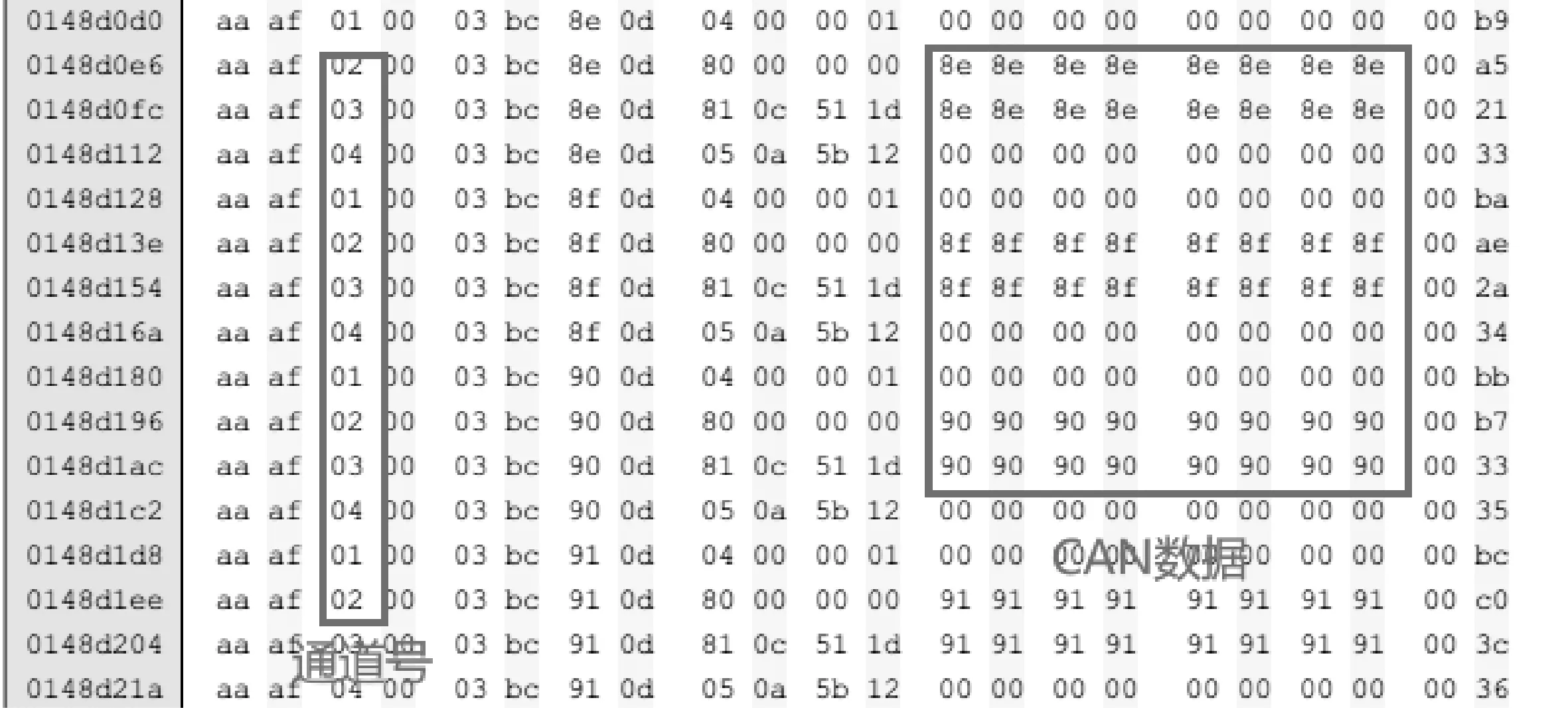

在测试完成后,使用记录器配套的上位机读数软件读取存储的数据,数据读取完成后,使用Hex Edit软件进行数据格式分析,由图9可以看出,系统采集存储的数据格式与设计好的帧格式一致,各个通道的帧记数有序排列,不同波特率CAN通信数据都被正确采集与存储。结果表明本系统能够正确自动地识别CAN通信波特率,并采集存储数据。

图9 部分数据结果

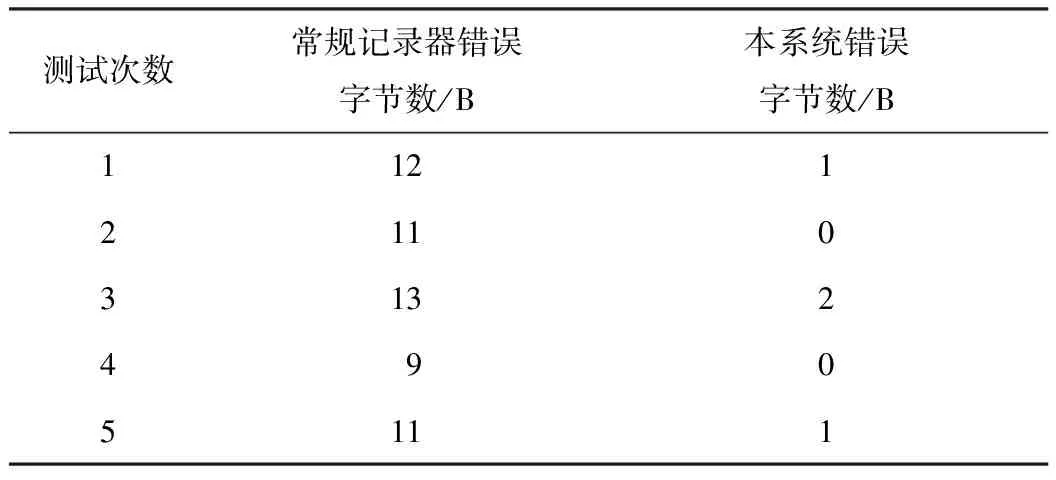

另外,分别对未使用ECC纠错算法的记录器和本系统进行5次数据存储与分析实验,每次存储与读取2 GB数据,测试两者的错误字节数,测试结果如表1所示。

表1 误码率测试对比表

分别计算两者的误码率,未使用ECC纠错算法的常规记录器平均误码率为5.21×10-9,本系统的平均误码率为3.72×10-10。由测试结果可以看出,在引入ECC纠错算法后,相对于无纠错算法的记录器,本系统数据误码率下降了1个数量级,可靠性、稳定性更高。

5 结束语

本文设计的CAN总线监控系统的创新点是波特率自适应和ECC数据纠错算法的引入,多通道数据并行记录也是本系统的亮点。实验表明,本文系统性能稳定、通用性高,数据误码率低,可以满足无人机多通道、多波特率CAN总线数据记录要求。