基于AD73360转换器在级联场景下应用的关注与思考

石东耀,王苏南

基于AD73360转换器在级联场景下应用的关注与思考

石东耀1,王苏南2

(1. 中国空空导弹研究院,河南 洛阳 471009;2. 深圳职业技术学院 电子与通信工程学院,广东 深圳 518005)

本文以AD73360为例,讨论了模数转换器在级联使用时容易遇到的共性问题.首先分析了在电路板设计时,对于功能相同性能又各自独立的电路功能模块在EDA布线时采用公共回路的地线噪音给系统稳定性带来的影响;随后讨论了级联模式下导致串行数据线误码问题的可能原因,并提出在EDA布线阶段对上述问题的解决方案及建议.

模数转换器;级联;电流回路

1 引 言

5G技术的推广,有效地解决了通信管道这个瓶颈问题.特别在物联网领域,由于5G-SA组网,可以实现1平方公里接入百万个传感器,为多通道信号采集的数据化提供了广阔空间.出于成本因素的考虑,多通道模数转换器的级联使用是硬件方案的较佳选择.

物联网的推广得以实现物与物之间任何时间、地点的互联,物联网产业生态可以划分为硬件、网络连接、平台及各个领域的应用服务等环节.其中传感、模组等硬件是实现物联网运载功能的主要基石,感知信号的采集、数据化及分析是系统运行物理过程的基础.

本文以AD73360为例,分析了模数转换器在级联使用时遇到的问题.

2 问题的提出

2.1 芯片介绍

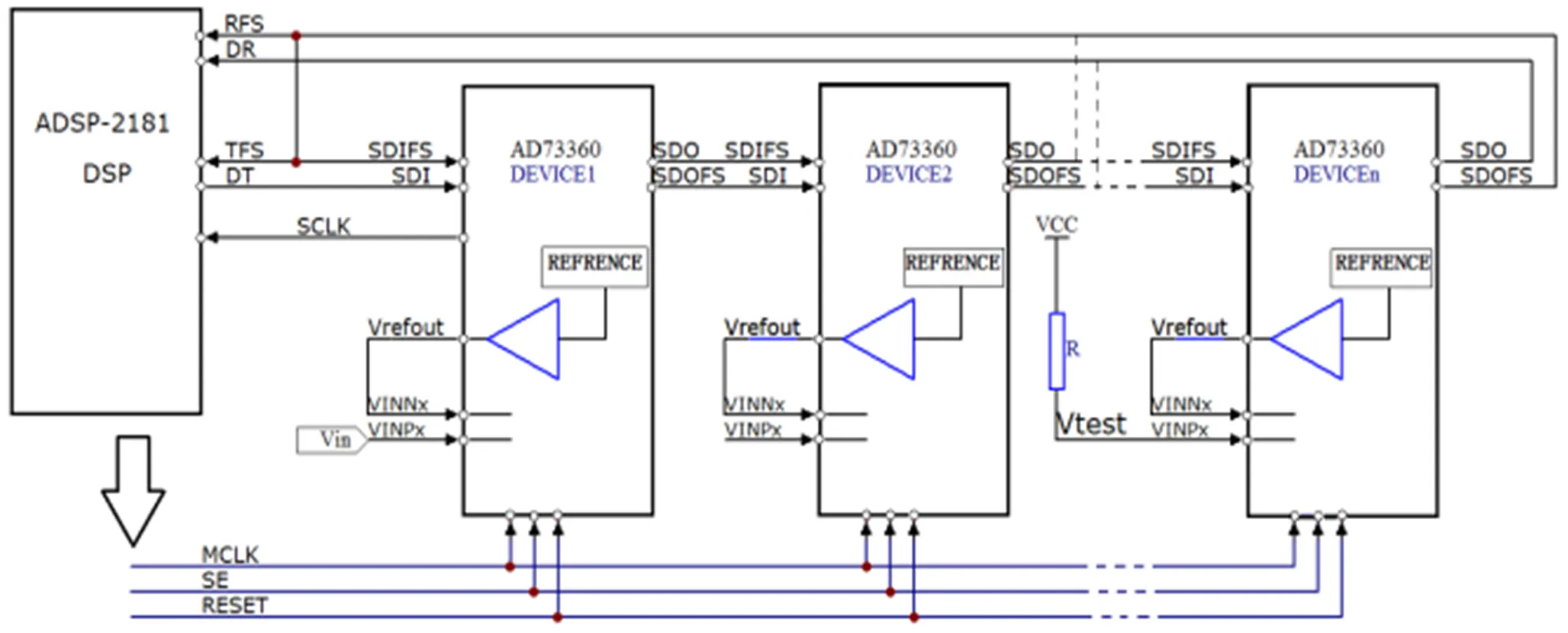

AD73360是一款面向工业计量的6通道模拟输入通用模数转换器,配有6路独立工作的16位A/D转换器,片内自带基准电压.串行端口(SPORT)模式作为数据通道实现多个(最多8个)模数转换器级联使用.

本文只讨论在使用AD73360的级联模式过程中(图1)遇到的一些EDA设计时的共性问题,不讨论该芯片的个性化特性.

2.2 参考电压的差异引发的问题

2.2.1 问题分析

2.2.2 故障现象分析

通过对数据采集通道的前置比例器的比例系数进行调整,没有明显的改善;通过硬件上对其模拟通道信号线的布线的走向、长短及地线简单处理也没有明显的效果.

图1 级联使用的系统框图

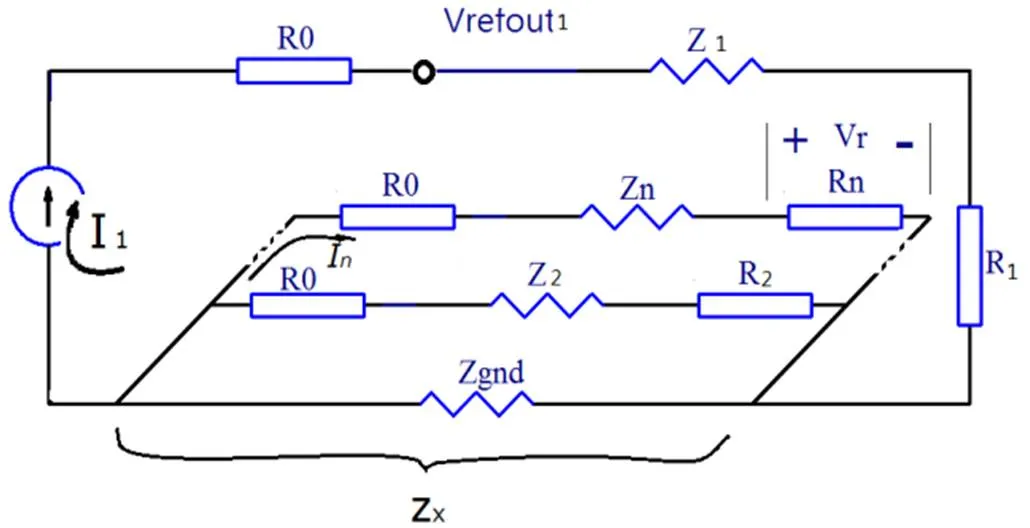

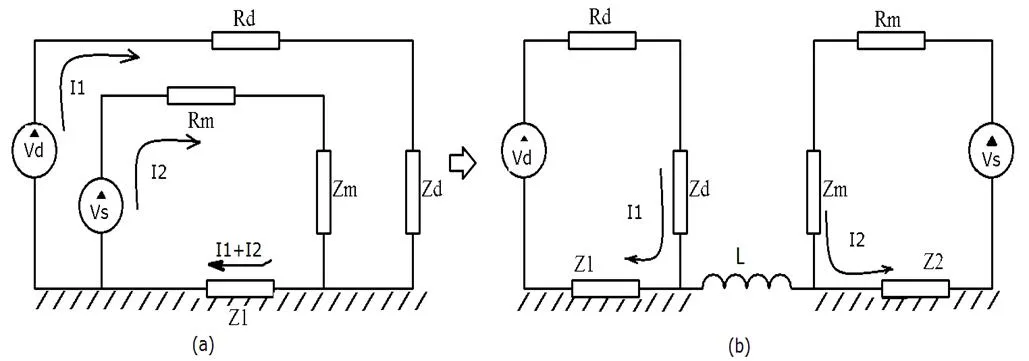

根据芯片AD73360的数据手册的描述,简单构建芯片在级联使用时其参考电压的电气连接关系如图2所示.

首先对芯片自身参考电压(REFRENCE)输的出进行建模.从理论上讲是:通过电压控制的电流源配以较小的输出电阻0来实现参考电压V的量化输出.

为了简化分析,假设系统工作在最简单的单极电压模拟量数据采集工作模式.以这种模式建模,其结构简单且具备代表性.

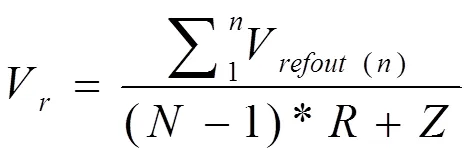

在这种情况下,个模数转换器的模拟量输入通道往往共用一个模拟地平面回路.多层电路板布局模式往往把多层电路板的其中一层规划出一块空间作为PCB的局部共地平面布线模式.如果把这个回路的寄生效应(引线的微电感、电容及电阻)集成近似为Z,如图2所示,芯片各采集端口的参考电压输入端口的输入阻抗假设为R,则R上产生的压降V,这个值实际上是模数转换器参考电压的实际值[1].

图2中,1表示“1号芯片”的任意一采集通道的VINP管脚的输入阻抗,对于AD73360来说,同一芯片的6路相同功能通道的输入阻抗值的一致性是有保证的.1表示芯片管脚外部连接布线的微带阻抗.角码代表第个级联芯片的任意一路采集输入通道.

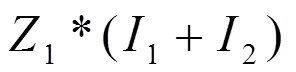

首先用叠加法来分析这个电路,假设不同芯片的采集通道VINP管脚的输入阻抗是相等的(即:1=2=R),由于级联的各路是并联关系,相互间的关联算法也是相同的.在这里只讨论“1号芯片”的V1对其他级联芯片的任意模拟量采集通道参考电压的影响.为了简化分析,在这里可以忽略其他级联芯片参考电压源的低阻抗状态,整个电路可以看作“回路1”(是自身布线阻抗1与输入阻态1及Z(公共阻抗与其他芯片回路阻抗并联后的等效阻抗)的串联电路.等效电路见图3[2].

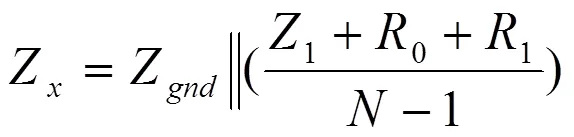

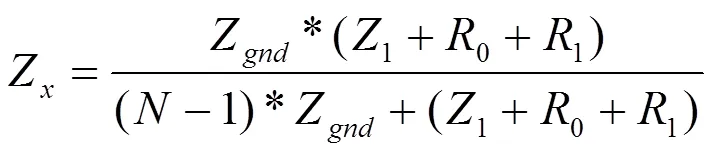

根据电路的基尔霍夫定理,可以建立如下等式:

(2)

图3 等效电路图

对于共地阻抗模式的推算,近似于地平面阻抗与其他芯片的模拟回流回路并联:

可以推导出:

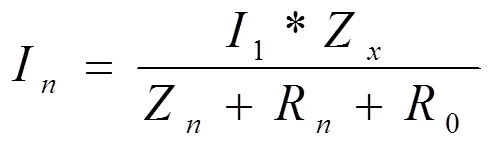

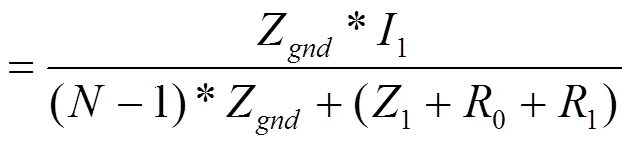

多个回路形成一个分流器,流经其中任意一个回路的电流设定为I,则有:

这个电流在级联的其他的任意通道的VINP管脚的输入阻抗R上产生压降V:

如果考虑到各级联芯片同时工作,单路VINN管脚参考电压值(VINNx)所受到的扰动与其他芯片参考电压输出之和相关,则有:

通过式(5)可以看出,级联A/D芯片参考电压输入端口的电平扰动量变化的相关因素有如下两个方面:

● 与其他芯片的参考电压输出值(V)有关;

● 与级联芯片的数量()相关.

2.2.3 解决方法

通过上面分析,模数转换器级联使用时级联各芯片参考电压值的偏差是导致采集通道数据漂移的原因之一.本案在EDA设计初期由于级联各芯片采用了简单共地模式而形成对“地”的公共回路使得这种扰动有条件产生.

解决方案:在电路板EDA设计阶段,PCB布线时级联各芯片的模拟信号建立独立的回路系统,各级联芯片的模拟地信号单点接入PCB板设定的模拟地平面(如果多层板有条件),这样可以有效抑制各芯片间共地回路产生的串扰.

产品进行装配前,对级联模数转换器进行筛选.尽量保证参考电压值相同的芯片用于同一产品上,这样也可有效降低同一系统中片间串扰.本案就是采取这种方法使得采集系统的稳定性得到了很大的提高.具体方法是在电路板焊接装配前,对模数转换器AD73360的参考电压输出值进行通电测试分类,参考电压值相同的芯片用到同一块电路板上.这种方法有效地解决了某产品在批产中遇到的转换数据不稳定的问题.

2.3 串行口初始化时的误码问题分析

系统启动之初DSP要对模数转换器进行控制字写入,以设置A/D芯片的工作模式.所以系统上电后模数转换器的默认数据传输模式要有较宽泛的兼容性,以适应不同主频的控制器.兼容性越强,相应付出的代价就是牺牲系统的稳定性.

在实际应用中,就发生过DSP对模数转换器初始化失败的案例.

2.3.1 问题分析

模数转换器在级联使用时与主机的通讯一般采用串行口的方式.为了兼容不同主频的数据处理器,在上电或重启后芯片默认的串行口传输波特率都是比较低的,而且要兼顾最多级联芯片的个数,所以默认的写入允许信号有效时间比较长.

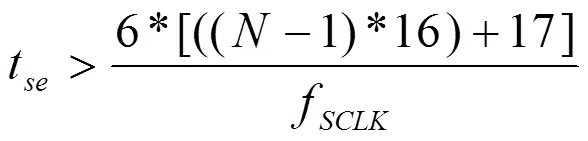

以AD73360为例:当芯片的工作主频为16.384MHz时,系统上电启动时或Reset信号后,芯片默认的串行数据传输时钟SCLK为A/D芯片工作主频的八分频,即:

假设N个模式装换器级联使用,上电后DSP对AD芯片片选信号的有效时间为:

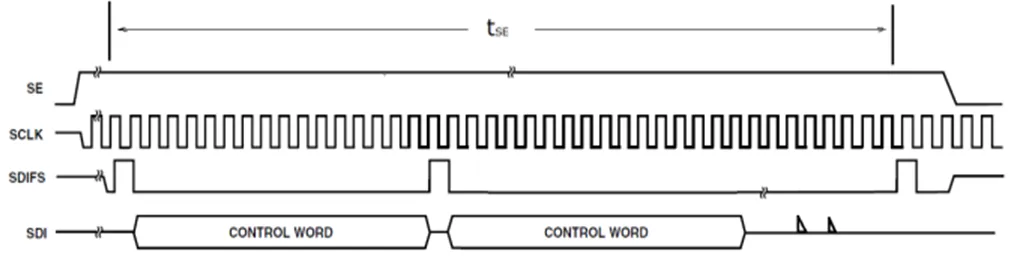

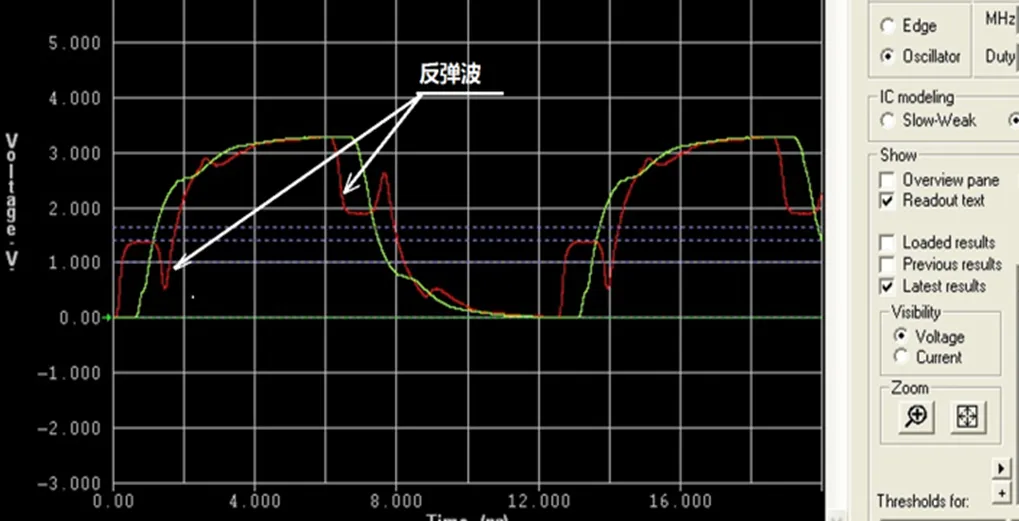

该脉宽最长可达256 μs,长时间的等待使得数据口误读到“地弹”或其他噪音的概率大大增加(图4).

图4 系统上电初始化的控制字写入模式

本案在调试初期就发生初始化失败的现象,并在逻辑分析仪上捕捉到导致初始化失败的脉冲噪音信号.

系统对模数转换器初始化设置成功后,有了固定的读写频率和严谨的时序逻辑,误码读入的概率也相应会降低.

2.3.2 解决方案

通过上述分析,导致初始化失败的可能是如下多种原因的集成:

● 芯片上电默认的读写模式过于宽泛,导致误读噪音的概率增加.

● EDA布线不理想,地线噪音环境污染数据传输线.

● EDA阶段器件布局的限制导致级联数据线布线长度过长及器件的端接“反弹”也是潜在的导致误码的原因.

解决这一问题就要在EDA阶段对电路板布线进行系统考虑.级联的概念意味着通过串联数据方式控制不少于两片模数转换芯片的使用,在硬件上要求尽量将芯片间的数据线的传输阻抗在布局时统筹考虑,例如:设计在同一布线层、如果由于布局限制不能保证两根信号线同一长度,则通过改变线宽度适当调整.传输线阻抗比决定传输线的反射特性.

在这一案例里,“地弹”污染数据信号线的概率较“端接反弹”要高,特别是集“模拟地”与“数字地”于一身的模数转换器芯片.如何有效地解决地线污染问题,除了“模拟地”和“数字地”之间做有效的隔离外,每个芯片在地线布局上形成各自独立的回路,尽量减少功能相同的部件之间的电流回路的串扰.

在电路板的EDA设计的实际应用中,噪音问题是十分复杂的,电路板布线措施也有点“拆东墙补西墙”的味道.此案中,级联的芯片越多误码的概率就越高,优化硬件设计的空间也越小.如果能牺牲一路模数转换器的资源作为检测通道,可以降低误码给系统带来的破坏.如图1所示,将测试通道接入特定值电平信号,系统对模数转换器初始化完成后,把测试通道采样值是否正确作为芯片设置是否成功的判据,否则就重新配置.

3 共性分析及EDA阶段的思考

3.1 关于单点接地原则的理解

关于“接地”的感念往往误导了EDA工程师在电路设计中对“地”的理解.用“回路”的概念去思考则更容易理解[3]7.每一个独立功能的电路模块都有自己独立的回路,不同的功能模块如果简单地通过“某覆铜层”而形成共同回路,则不同模块的信号之间的就会通过共同的“地回路”而产生污染.回路独立是减少功能模块间噪音的有效手段.

典型的用法是在模拟地和数字地之间,跨接一个磁珠,对于不同频率特性电路间串扰信号的抑制有积极的作用,图5(b).

图5 回路与扰动

3.2 串行数据线布线时的完整性思考

本案例中,DSP输出到第一片AD73360的串行信号数据线布线距离比较长(约20 cm),该段走线传输阻抗的估算也较为复杂.通过仿真软件对该段走线的传输特性进行分析,当数据信号上升沿接近2 ns时,传输信号才有端接反弹的迹象,如图6.这一结果表明:芯片复位时默认的波特率(5K)不足以产生端接反弹,端接反弹产生的噪声导致初始化失败的可能性较低[3]183.受总体结构布局的限制,印制板上DSP到模数转换器物理距离较远导致信号线布线空间过长,也存在复杂环境的交互信号线之间串扰发生的概率.

图6 端接反弹仿真结果

建议在EDA阶段,串联使用的数字信号传输线布线时预留串联调试电阻的焊盘,既可调整导线的传输阻抗保持与器件的输入阻抗一致,以降低反弹;又可与带状线的对地电容形成RC回路,抑制某些频段的扰动.经过验证后的阻值参数,可以固化到最终装配工艺中.

4 结 论

本文从EDA设计的角度,分析了模数转换器AD73360在级联使用时遇到的问题,并提出相应的解决方法,实践证明这些方法是有效的.

在EDA的布线规则中关于“单点接地”概念的核心不是“地”,而是“电流回路”.功能独立的电路模块有条件最好能形成各自独立的电流回路,最后通过单点接地来钳定电位.独立的功能模块有相对独立的电流回路,是降低电路间信号串扰的有效手段.

关于串行数据线在电路板布线之初就应该列为关注点.如果串行数据传输有严格的读写节拍,误读概率会很低,节拍本身就是一种滤波方式.本案例中的模数转换器为了适应更大主频范围的DSP,在上电初始默认的写入时钟及逻辑是比较宽泛的,增加了读入异常脉冲的概率.EDA的规则有很多,但难以兼而全之,系统自检软件及自恢复功能可以弥补硬件设计的不足.

[1] 菲利普(Phlips K).∑△A/D转换技术在信号调理中的应用[M].北京:工业技术图书馆,2018:92.

[2] 威廉·J·达利顿,约翰·W·波尔.辛斌,译.数字系统工程[M].北京:科学出版社,2005:262-263.

[3] Eric Bogatin.李玉山,刘洋,等译.信号完整性与电源完整性分析[M].北京:电子工业出版社,2015.

Reflowing After Application of AD73360 at Cascade Model

SHI Dongyao1, WANG Sunan2

()

This article analyzes the common problems existing in cascade model operation of analog to digital converter AD73360 and proposes potential solutions. A mathematical model is established based on kirchhoff’s law. Causes of performance issues such as drifting are rationalized by analyzing parameters varying per PCB layout. A special case of ADC faulty initialization is also addressed and recommendations are made to optimize the design application in EDA layout design.

A/D converter; cascade; current-loop

TP23

B

1672-0318(2022)01-0021-05

10.13899/j.cnki.szptxb.2022.01.005

2021-05-21

石东耀,男,河北邢台人,高级工程师,主要研究方向:机电控制自动化.

王苏南,男,河南洛阳人,副教授,主要研究方向:计算机网络体系结构、网络流量特性分析及检测.

(责任编辑:罗欢)