一种小型化Ka波段收发组件的设计

杨玉章,郭艳敏,陈丹

(中国电子科技集团公司第十三研究所,河北石家庄,050051)

0 引言

随着毫米波在射频前端的广泛应用,毫米波收发组件的发展也越来越受到研究人员的重视,目前毫米波收发组件发展的热点是小型化和高性能[1][2]。

本文通过对整机需求的分析和论证,设计了一种小型化的Ka波段收发组件。收发组件包括4个接收通道和1个发射通道,并且集成了频综单元。

1 收发组件工作原理和功能组成

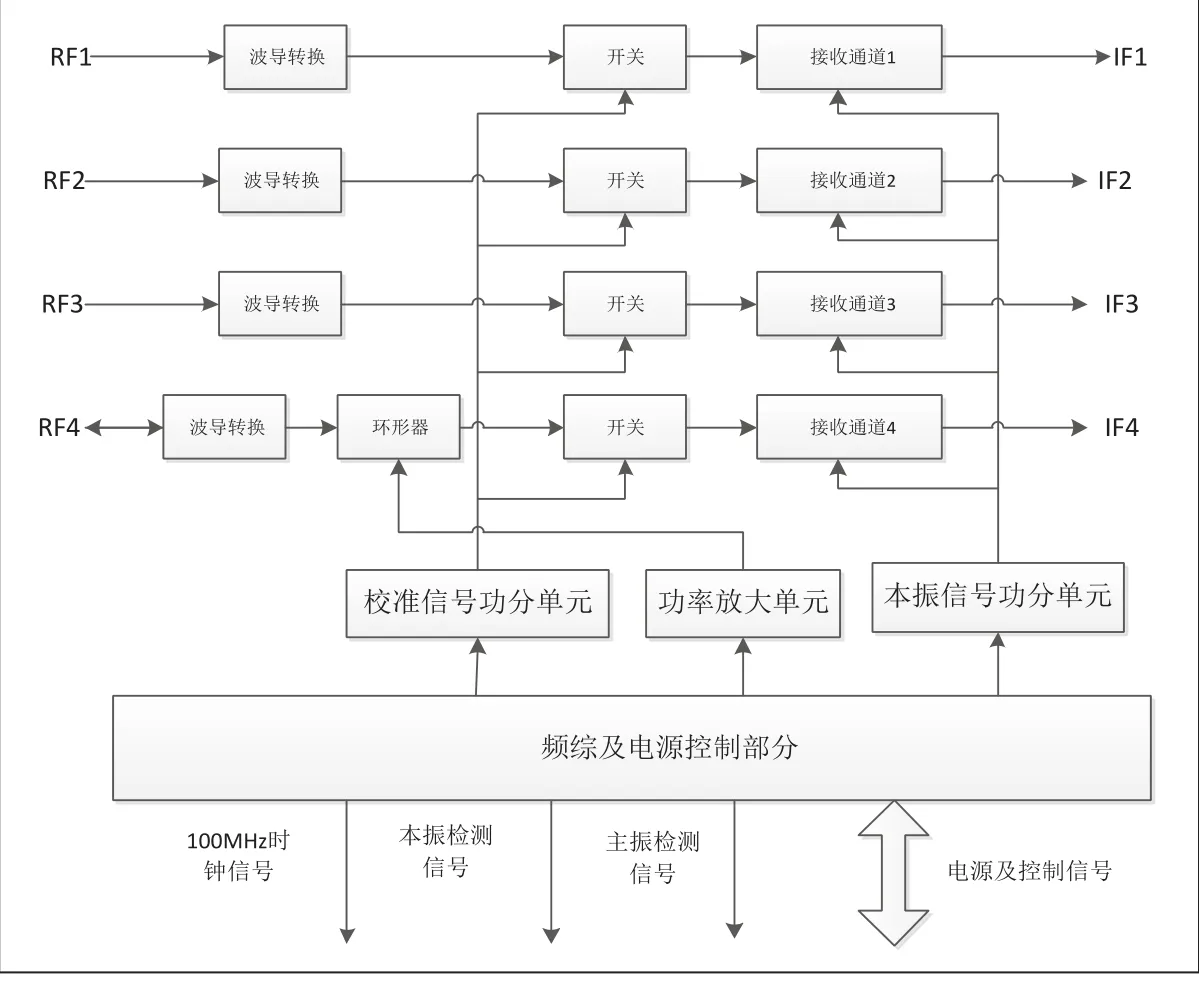

Ka波段收发组件在结构功能上由以下5部分组成:信号接收单元、校准单元、信号发射单元、频综单元、电源及控制单元。原理框图如图1所示。

图1 Ka波段收发组件原理框图

信号接收单元包括4路接收通道,其中1路接收通道与发射通道通过环形器共用射频接口,其余3路接收通道均只有接收功能,并且电路结构相同。接收通道采用一次下变频结构,将接收到的信号下变频至中频供整机使用。

校准单元主要包括开关、放大器和功分器等。主要功能是将频综单元产生的校准信号放大后功分至4路接收通道。

信号发射单元共有1路发射通道,包括一级低噪声放大器、一级驱动放大器和一级功率放大器。发射通道功能是将频综单元提供的主振信号放大发射出去。发射通道中的功放最长工作时间不超过60秒,采用脉冲调制的方式工作且占空比可调,功放最终输出脉冲峰值功率为13W。

频综单元主要包括晶振、数字频率合成器(DDS)和点频源等部分。晶振为频综内各个单元提供参考信号同时为雷达整机提供时钟信号。DDS为频综单元的快速调频提供激励信号。

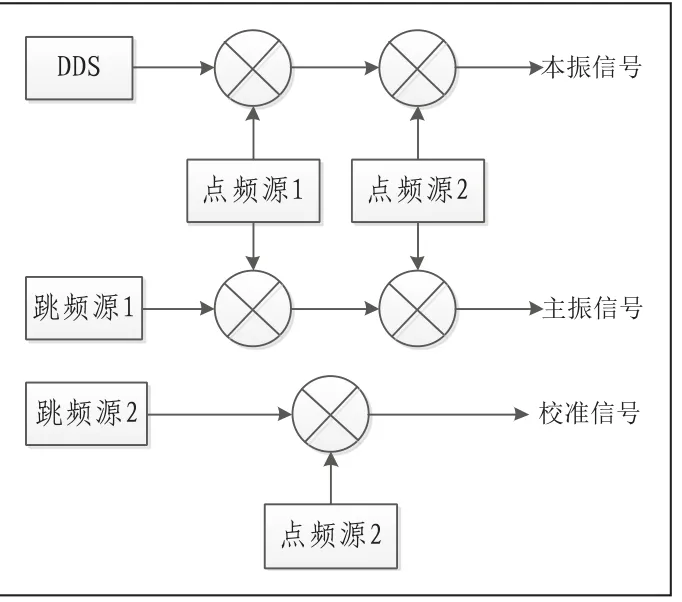

频综单元的原理框图如图2所示。本振信号由DDS和点频源1混频产生的信号再与点频源2混频产生,作为接收通道的本振信号。主振信号由跳频源1与点频源1混频产生的信号再与点频源2混频产生,作为发射通道的主振信号。校准信号由跳频源2和点频源2直接混频产生,作为接收通道的校准信号。跳频源1、跳频源2、点频源1、点频源2均通过锁相环产生,参考信号均为晶振功分产生。

图2 频综单元的原理框图

电源及控制单元包括一级DC—DC稳压模块,多级线性稳压器、单片机、FPGA等电源及控制器件。电源部分为组件提供电源处理、馈电网络。控制部分实现整机与组件的串口通信并对组件内部的各单元工作进行时序控制。

2 Ka波段组件指标设计及优化

2.1 接收通道链路

接收通道的原理图如图3所示,除收发共用的通道外,3路接收通道电路结构上一致,具有限幅、校准、信号切换以及增益控制功能。收发共用通道比其他3路接收通道在结构上多一级环形器。

图3 接收通道原理图

为满足整机对组件的抗烧毁要求,在接收通道的前端增加一级限幅器。通过切换通道前端的单刀双掷开关可以选择接收通道工作在校准模式还是接收模式。同时,为了保证接收通道的动态,分别在射频段和中频段增加了一级数控衰减器,最终可以在5dB步进衰减的基础上实现80dB的最大衰减量。在射频段还增加了一级MEMS滤波器,用来滤除带外的干扰信号和镜像频率。

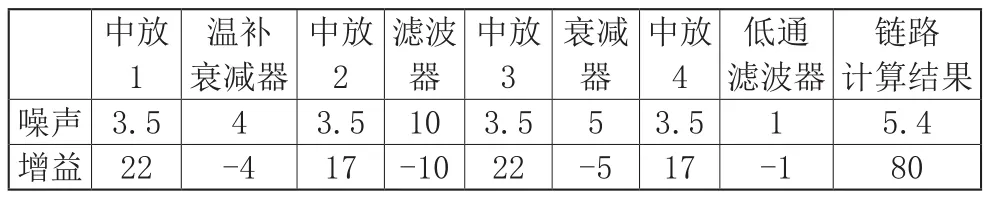

接收通道1~3的变频增益要求为80dB,综合考虑通道的噪声系数、动态范围等要求,射频部分采用两级低噪声放大器(LNA)实现,射频净增益约为24dB,其余56dB增益分配在中频段,采用4级单片放大器实现。设计结果如表1所示,增益为80dB,噪声约为5.4dB。

表1 接收通道1~3链路增益分配和噪声计算

表1(续) 接收通道1~3链路增益分配和噪声计算

接收通道4除在校准开关和波导转换之间增加一级环形器外,其余部分与接收通道1~3电路结构一致,环形器的差损约为0.5dB,因此接收通道4增益约为79.5dB,噪声约为5.9dB。因此1~4路接收通道的噪声系数均可以满足不大于7.5dB的指标要求。

此外,为防止信号之间的串扰,还必须考虑4路接收通道间的隔离度。信号之间串扰主要是通过共用的本振、电源线和控制线之间的串扰。为增加通道之间的隔离度,接收通道的本振采用先功分后放大的方式,这样各本振支路上的放大器可以增加本振信号的隔离度。此外通过增加电感、电容等方式增加电源线和控制线之间的隔离,可以满足通道间隔离度不小于50dB的要求。

2.2 发射通道顶降和调制开关的前后沿

发射机脉冲理论上矩形是最佳的,但是实际中多为钟形脉冲,因此需要大的储能电容,可以满足功率管在工作状态下的瞬间大电流需要。所需储能电容的容量,可由下式估算[3]:

其中△V可近似等于V×电压顶降。

功放电流的峰值电流为3.75A,工作电压24V,最大脉宽80us,脉冲顶降按参照10%设计,需要的电容量为C=3.75×80/(24×10%)=125uF,因此在功率芯片附近采用3只68uF共204uF钽电解电容并联即可满足指标要求。

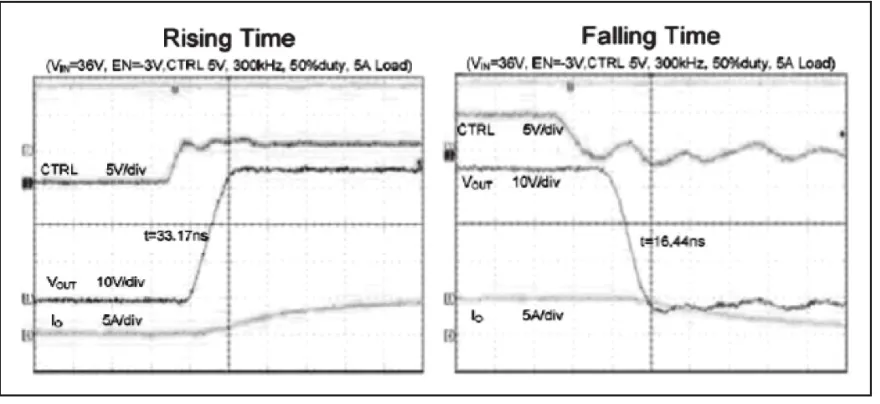

发射机的开关机脉冲前后沿主要与功放电源的驱动有关,选用一款国内生产的驱动器,具体指标如图4所示。

图4 功放芯片驱动的前后沿

经实际测试功放的上升和下降时间分别为37ns和18ns。

2.3 本振信号的低相噪设计

本振源由DDS频综与S波段点频源混频后,再与Ku波段点频源混频产生,相噪由DDS相噪,S波段相噪和Ku波段点频源倍频后的相噪,及混频后的相噪共同决定。

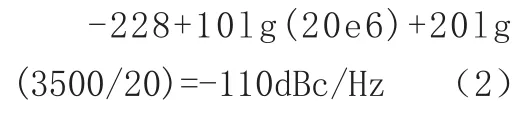

S波段点频源采用锁相环实现,器件底噪为:-228dBc/Hz,鉴相频率20MHz,环路带宽100KHz;

根据器件噪底公式[4]计算,基于鉴相器的的相噪为:

根据晶振恶化的公式计算[5],基于晶振的相噪为:

综合器件底噪和晶振的影响并考虑到工程恶化,S波段点频信号的相位噪声可达-109dBc/Hz@10kHz。

DDS相位噪声由DDS时钟参考信号决定,DDS时钟参考信号由S波段点频源提供,其相位噪声为-109dBc/Hz@10kHz。DDS输出频率最大为650MHz,根据DDS输出信号与时钟参考信号的频率关系,则DDS输出相噪为:

DDS和S波段点频源混频后的相噪为:-108dBc/Hz@10kHz。

Ku波段点频源采用PDRO实现,其相噪为:-103dBc/Hz@10kHz,因此二倍频后的相噪[6]为-97dBc/Hz@10kHz。

本振输出相位噪声由DDS和S波段点频源混频后的相噪,谐波混频后的相位噪声共同决定;DDS和S波段点频源混频后的相噪为:-108dBc/Hz@10kHz,Ku波段点频源二倍频后的相噪为-97dBc/Hz@10kHz,则本振的相位噪声为-96dBc/Hz@10kHz,满足≤-93dBc/Hz@10kHz的指标要求。

2.4 主振信号的低相噪设计

主振源由P波段频综与S波段点频源混频后,再与Ku波段点频源混频产生。相噪由P波段频综相噪,S波段点频源相噪和Ku波段点频源倍频后的相噪,及混频后的相噪共同决定。

P波段频综源和S波段点频源采用锁相环实现,Ku波段点频源采用PDRO实现,采用与本振源相同的方法计算,因此可以得出主振的相位噪声为-96dBc/Hz@10kHz,满足≤-93dBc/Hz@10kHz的指标要求。

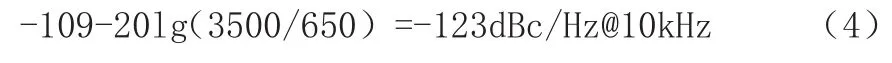

图5 功放工作后热量分布图

2.5 接收机的热设计

收发组件的体积较小且功能多,因此散热要求很高。为保证收发组件的正常工作,采取了以下措施:

(1)进行结构设计时,采用ANSYS软件对盒体进行热仿真,将散热量大的部分采用热接触的方式进行散热,并尽量扩大接触面。

(2)在电路设计时,考虑散热,优先选用功耗小的元器件。

(3)发热量大的元器件尽量分散开,避免热源集中,为电路板上的散热元器件设计导热通孔。

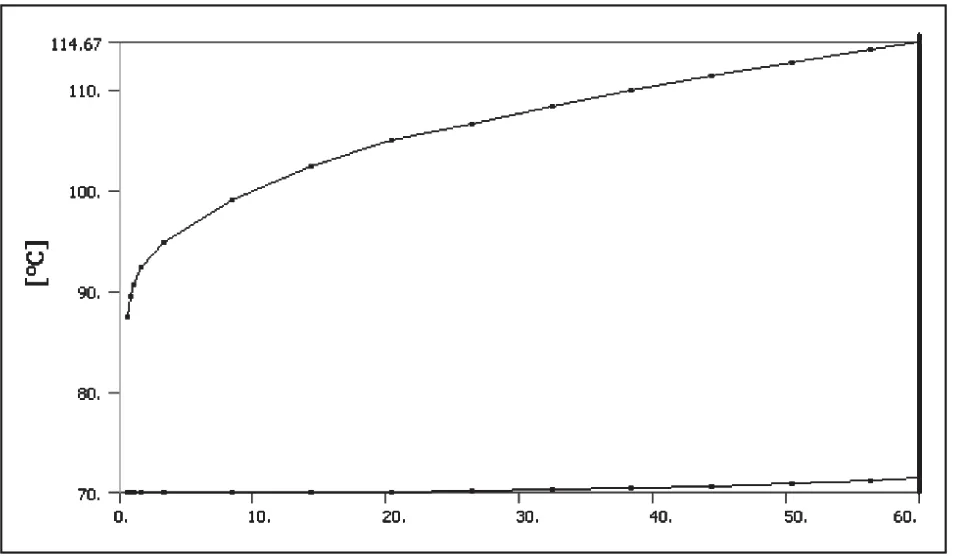

通过以上3方面措施的改进后,经仿真可以看出,组件工作60秒后,最高温度约为114°,不会烧毁芯片,因此组件可以正常使用。

图6 组件工作60秒后组件温升图

3 研制工艺及测试结果

收发组件的功能复杂,体积较小(Ø67mm*90mm),所以在接收机结构设计时需要考虑合理布局,并尽量采用芯片,配合小型化工艺,最大限度的减小组件的体积。

为满足高频接收组件的使用环境要求,盒体采用了防锈铝材料,表面为白氧化处理,采用局部镀金工艺处理,射频部分腔体盒盖采用激光封焊工艺,对内部芯片器件起到保护作用。

表2 收发组件部分指标测试结果

收发组件的工艺过程为芯片共晶,金丝键合、基片烧结、再流焊、手工焊接、总装等工序。表2为收发组件部分指标的测试结果,测试结果表明各项性能指标均达到了整机要求。

4 结束语

本文通过对各性能指标的分析和计算,完成了一种Ka波段收发组件的设计。在研制过程中重点分析了接收通道的链路增益、噪声、发射通道的顶降、本振源和振源的相位噪声等关键指标。

收发组件在完成生产和调试之后,经测试各项指标与设计指标基本相符。