用于卫星载荷数据传输总线的终端IP核设计

刘文婷,万小磊,徐楠,杨童,陈亮亮

中国空间技术研究院通信与导航卫星总体部,北京100094

在通信卫星中,行波管放大器(traveling wave tube amplif ier,TWTA)是有效载荷分系统的重要组成部分[1]。1个行波管放大器通常具有10个遥测量,需要6条遥控指令,如果采用点对点遥控遥测方式,则需要使用大量繁复的低频电缆。国内最新的通信卫星平台中,已采用同步串行总线实现对多个行波管放大器的遥控遥测[2]。通信卫星有效载荷数据传输总线技术的使用极大地减少了卫星通信舱电缆网的数量及重量、简化电缆网的布局,同时还可以减少装配及测试周期,显著提升了通信卫星的载荷能力。

本文提到的通信卫星有效载荷数据传输总线是中国空间技术研究院自有知识产权的一种总线技术[3],主要应用于通信卫星载荷设备TWTA遥测遥控数据传输,其核心包括总线控制器(bus controller,BC)和总线终端(remote terminal,RT)两部分。本文提出了一种可用于该传输总线的终端IP(intellectual property)核的设计方案,并进行了系统仿真验证、FPGA(f ield programmable gate array)验证[4]及流片测试。IP核复用能够有效地缩短产品开发周期并降低成本,提高效率[5]。本设计IP核在代码结构和编译综合上采取了多种优化设计,功能全面、性能优良,可应用于通信卫星地检验证设备或直接应用于卫星有效载荷设备中。

1 有效载荷数据传输总线工作原理

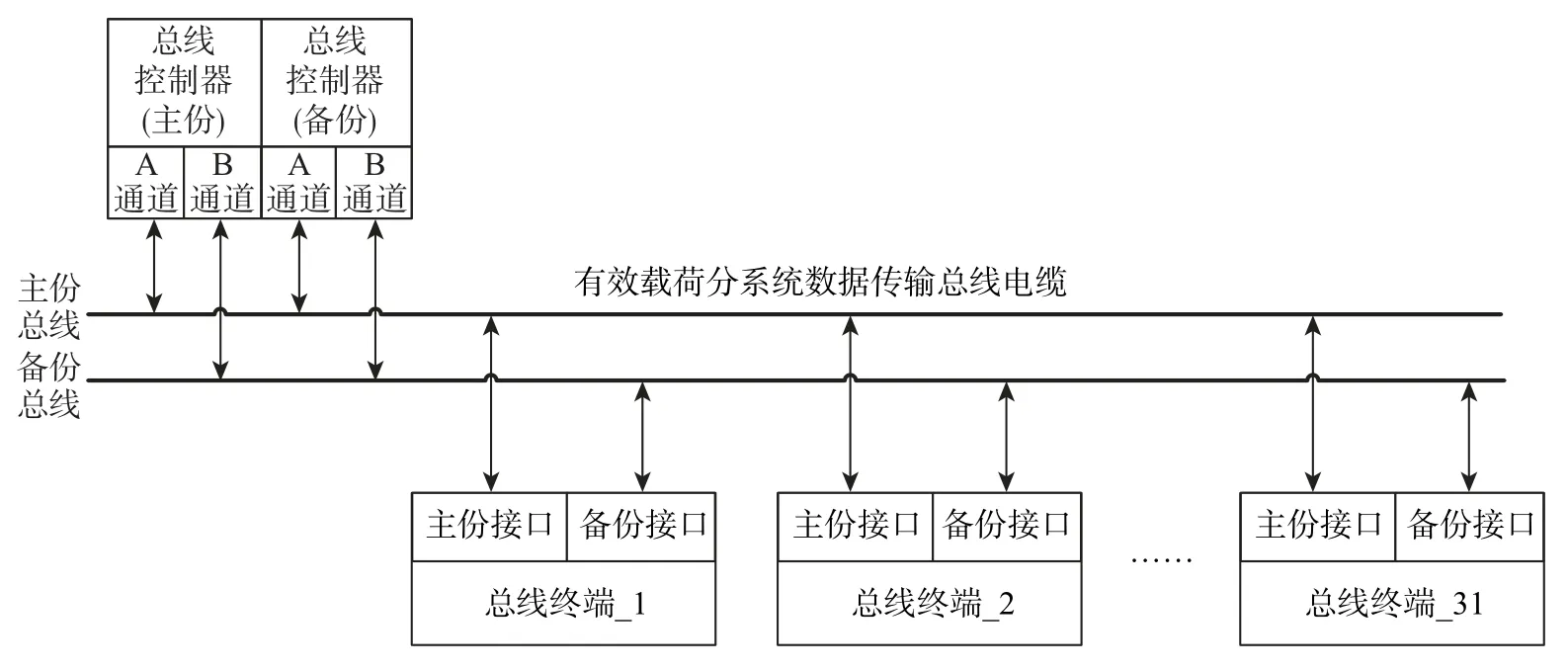

有效载荷数据传输总线主要包括总线控制器(BC)、总线终端(RT)总线电缆网等[3]。传输总线具有以下3个特性:1)该总线为低速同步五线制串行总线,1条总线可以提供31个终端设备的接入能力,总线采用TTL电平标准、单端传输,具备冗余设计;2)采用同步工作模式,时序关系简单,减小了总线通信协议的复杂度,降低了总线专用集成电路协议芯片研制的难度;3)总线控制电路与终端电路采用专用的接口电路,在改善信号上升沿/下降沿的同时,具备一定抗噪声干扰的能力,使总线信号传输更可靠。有效载荷数据传输总线的总线控制器、总线终端、传输总线电缆之间的关系如图1所示。

图1 有效载荷数据传输总线连接关系图Figure 1 Payload data bus structure chart

总线控制器是有效载荷数据传输总线上遥测接收任务、遥控指令发送任务的发起者。总线终端是有效载荷数据传输总线上指令接收的用户,总线终端只能被动接受命令,不具有自主向总线控制器发送数据的能力,仅当总线控制器请求发送数据时,总线终端才向控制端发送遥测数据。在空闲时间内,总线终端按照其自身采集时序采集终端设备的遥测参数。

总线传输的5条信号分别定义为:

1)时钟信号(CLK),总线时钟(收/发共用),由总线控制器输出;

2)指令使能信号(CMD),由总线控制器输出,当总线控制器输出串行命令数据时,该信号为高电平;

3)遥测使能信号(ACQ),由总线控制器输出,当总线控制器从终端读取遥测数据时,该信号为高电平;

4)指令数据(C_DATA),由总线控制器输出,控制器从此端口输出串行指令数据;

5)遥测数据(T_DATA),由终端输出,当前被访问终端从此端口输出串行遥测数据。

2 总线终端IP核设计与仿真

2.1 总线终端IP核框架

本文在对IP核进行设计时,详细研究了有效载荷数据传输总线协议[3],该总线为同步总线,欧洲ASTRIUM公司主流卫星Eurostar-3000平台用于有效载荷数据传输的LSSB总线[6]也是同步总线,相比法国SpaceBus4000平台所用的异步OBDH总线[7]具有协议简洁、实时性强、占用软硬件资源少、系统开销小等优势;同时,与Eurostar-3000平台的LSSB总线和SpaceBus4000平台的OBDH总线类似,该总线为串行总线,相比并行总线具有连线少、易维修、成本低、适合远程传输等特点。为了实现总线终端的小型化,总线终端最终的逻辑控制电路一般采用专门定制的ASIC芯片,其功能复杂且存在数模混合电路,因此工艺复杂度较高,芯片的系统验证工作也具有一定难度[2]。本设计IP核参考Eurostar-3000平台LSSB总线接口设计方案[8],将星载有效载荷数据传输总线终端IP化,不仅能够满足有效载荷数据传输总线协议中规定的终端采集传输规范,而且创新性地在IP核中增加了终端设备行为模拟功能,在使用该IP核实现总线功能和性能验证的基础上,完成总线控制端设备的遥测遥控功能验证。

具体来说,本文设计的总线终端IP核具备如下功能:

1)接收总线控制器的命令并向总线控制器发送遥测数据;

2)模拟TWTA组件的行为,具备阳压、螺流、工作电流以及各种工作模式、增益状态、功率调节状态、静噪状态、自动重启状态等特征行为的模拟;

3)动态终端地址检测,支持单核终端主备双份;

4)AD(anolog to digital)采样功能以及状态量采集功能;

根据有效载荷数据传输总线特性和上述功能要求,总线终端IP核框架设计如图2所示。

考虑产品的通用性,我们选择频率为20 MHz的外部晶振提供时钟输入。但IP核内部的全局工作时钟只需50 kHz~100 kHz,故需要将外部输入时钟进行分频,所以本文设计了时钟分频模块。为实现接收总线控制器指令和向总线控制器发送遥测数据的功能,需设置总线接口模块。同时,还需要IP核能够进行输入指令和数据的分析、判断、处理,奇偶校验、RT地址动态检测,将采集到的数据进行组帧,并可以模拟TWTA组件的行为,为此本文设置了协议处理模块。数据采集模块用以完成对终端设备模拟量和状态量的采集工作。这4个模块在顶层模块中实现互联和例化[9]。

综上所述,本设计总线终端IP核由5个程序模块组成,包括总线接口模块、时钟分频模块、协议处理模块、数据采集模块、顶层模块。

2.2 各模块设计和代码实现

2.2.1 顶层模块

总线接口模块、时钟分频模块、协议处理模块和数据采集模块这4个模块在顶层模块中实例化并实现互联,由于有效载荷分系统数据传输总线协议规定其具备冗余设计(包含主备份),故顶层模块包含了主备两份总线接口模块。各模块之间的连接关系如图2所示。

图2 总线终端IP核框架设计Figure 2 Design of the RT IP core

顶层模块中定义了有效载荷数据传输总线终端IP核所有的外部接口信号,包括时钟信号与复位信号、接口模块信号以及遥控、遥测接口信号。

2.2.2 时钟分频模块

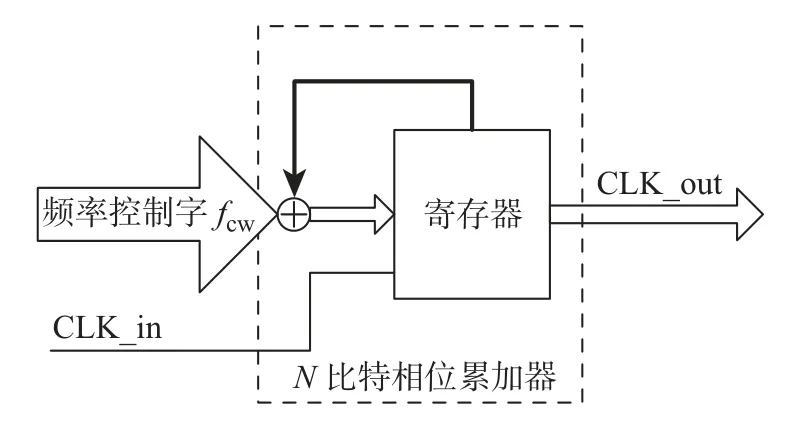

本设计中时钟分频模块采用NCO(numerically controlled oscillator)技术,即数控频率合成技术,该技术具有较高的运算速度[10]。如图3所示,在一个输入时钟周期CLK_in内,频率控制字fcw与N(本设计中为32)比特相位累加器累加一次,累加的最高位输出即为所需的分频时钟。最后得到的输出频率为

图3 NCO时钟产生模块Figure 3 Generator of the NCO clock

在外部输入晶振为20 MHz的情况下,为得到50 kHz的全局时钟,频率输入字fcw在程序中取值为0x00A3D70A。

2.2.3 总线接口模块

总线接口模块主要完成IP核输入信号的接收和输出信号的发送,根据总线协议的要求,本设计IP核包含总线接口模块主份和备份双份,当主份和备份的命令时序重叠时遥控命令以最后收到的命令数据为准。遥测数据的发送为被动发送,若主份和备份同时发送遥测数据,主份和备份总线上会同时出现数据且数据内容一致。主份和备份双份设计是为了提高总线使用的可靠度[11],通常情况下,主份和备份不会同时工作。

2.2.4 协议处理模块

协议处理模块是总线终端IP核的核心模块。它依据有效载荷数据传输总线通信协议的定义,完成对由接口模块和数据采集模块传输进来的遥控和遥测数据的分析和处理。包括奇偶检验、地址检查、命令分析、命令判断等功能,并输出对采集端设备的控制信号。同时可模拟TWTA组件的行为及将模拟结果作为遥测参数返回给接口模块,或直接将数据采集模块传过来的采集端设备遥测值组帧输出给总线接口模块。协议处理模块程序具体的处理流程如图4所示。

图4 协议处理模块设计Figure 4 Design of the protocol processing module

协议处理模块程序的处理流程包括奇偶校验、地址检测、命令模式字分析,根据接收到的模式字类型进行总线消息处理。

当接收到的命令模式字(command mode indication,CMI)为001、010、100时,总线终端存储该模式,并将功率调节、增益或电平的设置数据存放至保持寄存器。同时,为了遥控验证的遥测,此时把数据也传给遥测接口。仅当接收到命令执行指令后且没有接收到禁止执行指令时,则终端将上条命令传送至设备电路,执行命令。

当接收到执行指令(CMI=111),则保持寄存器将命令数据传送至设备电路,执行命令。

当收到加载并立即执行命令时(CMI=011,101),则所有过程合并,直接执行该命令。

如果接收到两条连续的执行命令(CMI=111),则两条连续命令中的第2条命令将被忽略,但第2条命令中静噪和自动重启功能的设置被认为有效;或者,两条连续执行命令中的第1条命令为加载并执行命令(CMI=011或101),第2条命令为执行命令(CMI=111)也被认为有效。

当接收到遥测请求命令时(CMI=000),则遥测使能条件应立即产生,串行遥测接口随着时钟信号,连续的将16 bits遥测字传送至总线,当遥测使能条件终止时,串行遥测结束,此时将总线释放给串行命令。

此外,TWTA组件的行为模拟功能也在该模块中实现,包括TWTA组件工作模式、增益状态、静噪功能等特征行为的模拟;具备对开关机、静噪开关、工作模式选择、增益档设置等指令的接收能力,并反馈相应遥测输出,包括开关机、阳压、螺流、工作电流、增益档、工作模式等遥测参数的模拟输出。

2.2.5 数据采集模块

数据采集模块完成TWTA组件的模拟量采集,包括检测器输出电压、输入衰减器电压、阳压、内部温度、主电流、螺流等参数;以及数字量实时采集,包括工作模式(1 bit)、静噪状态(1 bit)、自动重启状态(1 bit)、增益状态(8 bit)等参数。遥测采集模块能够定时采集6个模拟量和23个状态量。

其中6个模拟量采集控制信号由模块工作时钟产生,没有异步信号处理。6个模拟量为定时采集,只要片外AD使能被选中,程序内部模拟量定时采集便开始。为了定时循环采集这6个模拟量,程序内部设定一变量ana_cnt[2:0],定义了其数值与采集的模拟量之间的关系。

另外23个状态量经过内部时钟亚稳态处理后,由协议处理模块组帧输出。

2.3 IP核资源统计、功能仿真

2.3.1 IP核资源统计

为了达到较高的性能指标,本文IP核在综合的过程中采取了优化措施以提高速度并减少资源占用。在编译综合优化时设定了严格的约束条件并制定了编译策略。其中,时序约束用于规范设计的时序行为,完成本设计所期望的时序条件;区域位置约束用于芯片IO(input and out)引脚的确定;其他约束条件包括芯片型号和电气特性等。编译策略指定了编译优化策略以及优化算法,包括综合策略和布线策略[12]。

经过综合优化后,本文IP核资源占用情况如表1所示。以Virtex芯片为例,其基本单元为Slice,本文IP核寄存器Slice共占用375个,LUTs的Slice共占用316个,分别占整个FPGA基本单元的1%,IO引脚占用为21%。

表1 IP核资源统计Table 1 Statistics of the IP core

2.3.2 IP核功能仿真

总线IP核仿真使用Modelsim SE 6.5b,采用遍历的方式将各种输入组合加载到总线终端IP核来测试IP核对各种激励的响应情况,从而达到IP核仿真测试的正确性和完备性。

IP核的仿真测试主要从以下4个方面进行[13]:

1)模块接口,对被测的模块,信息能否正常无误地流入和流出;

2)模块数据结构,在模块工作过程中,其内部的数据能否保持其完整性,包括内部数据的内容、形式及相互关系不发生错误;

3)覆盖条件,模块的运行能否达到语句覆盖率100%的要求;

4)出错处理,模块工作中发生了错误,出错处理设施是否有效。

IP核的仿真内容包括:代码覆盖率、总线时序验证、总线命令、总线遥测、总线仲裁、总线工作异常情况。仿真结果表明:IP核代码覆盖率达到100%;在极限情况下,IP核也能完全满足时序约束要求;总线命令能够完成所有命令模式字要求的功能,总线遥测可按要求正常返回;总线仲裁满足“在主备总线同时发送总线命令时(即指令使能信号有交叠时)下降沿出现较晚的一方指令数据有效”的要求;在定义的多种异常工况下总线均能正常完成通信功能。

3 FPGA验证及流片测试结果

本设计IP核的FPGA硬件验证系统及实物图如图5所示。

图5 IP核FPGA硬件验证系统Figure 5 Verif ication FPGA system of the IP core

本验证系统具备主/备两套五线制同步串口电路,接口电路与总线要求的电气规范保持一致,每套包括3个输入、1个时钟、1个输出;设置了通用I/O接口以便连接,AD接口电路用以实现对采集端设备传输回来的模拟量遥测参数的模数转换;外部提供了20 MHz的晶振频率给FPGA;全局复位电路输出全局复位信号;具备5位RT地址电路及8位状态输入电路;设置了3套数据输出电路,分别实现TWTA的增益状态数据输出、功率调节数据输出以及数据控制输出;FPGA管脚电平为3.3 V,而总线接口电路、AD芯片均要求5 V传输电平,故系统加入了电平转换芯片RS245和相关电路,可实现输入信号5 V到3.3 V的电平转换以及输出信号3.3 V至5 V的电平转换。

FPGA采用Virtex5芯片,经过设计输入、功能仿真、综合、布局布线、管脚分配、时序仿真通过后,编译并写入FPGA,然后进行硬件调试[13]。FPGA验证试验包括RT功能正常通信测试、可靠性设计实验[14]。

正常通信测试包含以下测试项目:装载增益状态数据并等待执行指令测试、装载增益状态数据并立即执行指令测试、装载功率调节数据并等待执行指令测试、执行指令测试、禁止指令测试、模拟量遥测测试、终端地址测试、连续指令功能测试、连续遥测功能测试等。验证结果表明,终端IP核设计功能正常,能够满足总线协议的验证要求。

图6为某次终端通信过程中示波器所捕捉到的总线通道A的输出信号,在总线控制端发出遥测获取指令后,终端根据指令内容返回对应的遥测数据。图中从上到下4条波形分别为:指令数据、指令使能信号、时钟信号、遥测数据。

图6 FPGA验证结果Figure 6 Test results of the FPGA

可靠性设计测试包括误码率测试、错误注入和异常事件处理。在整个测试过程中,单次实验中测试的消息超过106,没有出现奇偶校验错误,总线指令接收与遥测输出均正常,测试结果与预期结果一致,说明总线终端IP核的设计符合预期要求,误码率小于10−6。

本设计IP核采用航天772所生产的0.5µm两层金属的硅栅CMOS工艺进行流片并封装,如图7所示。流片测试结果与FPGA测试结果一致,通过功能和性能考核。

图7 IP核IC封装图Figure 7 IC packaging of the IP core

4 结语

本文提出了一种用于有效载荷分系统传输总线的终端IP核设计和验证方案,设计具有自主知识产权[15],经过模块仿真、IP核系统仿真、FPGA试验验证及流片测试,结果表明本设计IP核功能全面正确、资源占用少、抗干扰能力强、可靠性高。

本文提出的总线终端IP核不仅能够实现总线传输协议要求的所有功能,同时还具备终端设备行为模拟功能。该IP核可以完成有效载荷传输总线的功能和性能验证以及总线控制端设备的遥测遥控功能验证。国产TWTA组件可直接使用本设计IP核,完成其总线终端逻辑控制功能。本设计IP核已成功应用于某国产通信卫星型号任务的总线地面验证系统中。