基于SHA-1身份认证的Flash程序烧写系统

张 铆 洪 泽 蒋炯炜

(中国电子科技集团公司第五十八研究所 江苏无锡 214072)

随着互联网、物联网等技术的飞速发展,嵌入式应用已日渐普及,无论是从高清电视到机器人,还是从汽车到飞机,都离不开Flash的使用[1].Flash由于其存储容量大、密度高等特性,已经在嵌入式系统中得到广泛的应用.

目前,Flash存储器主要用于存放用户自行开发的应用程序.但由于近几年封装技术的突破,给用户对Flash存储器的烧写带来极大不便,特别是Flash芯片已经焊接在电路上[2].针对上述问题,本文采用FTDI的USB2.0通信芯片FT2232H和SOC设计了一种高效的存储器烧写系统.为了进一步提升烧写系统的安全性,该系统利用SHA-1算法完成了上位机与下位机的身份认证.

1 系统结构

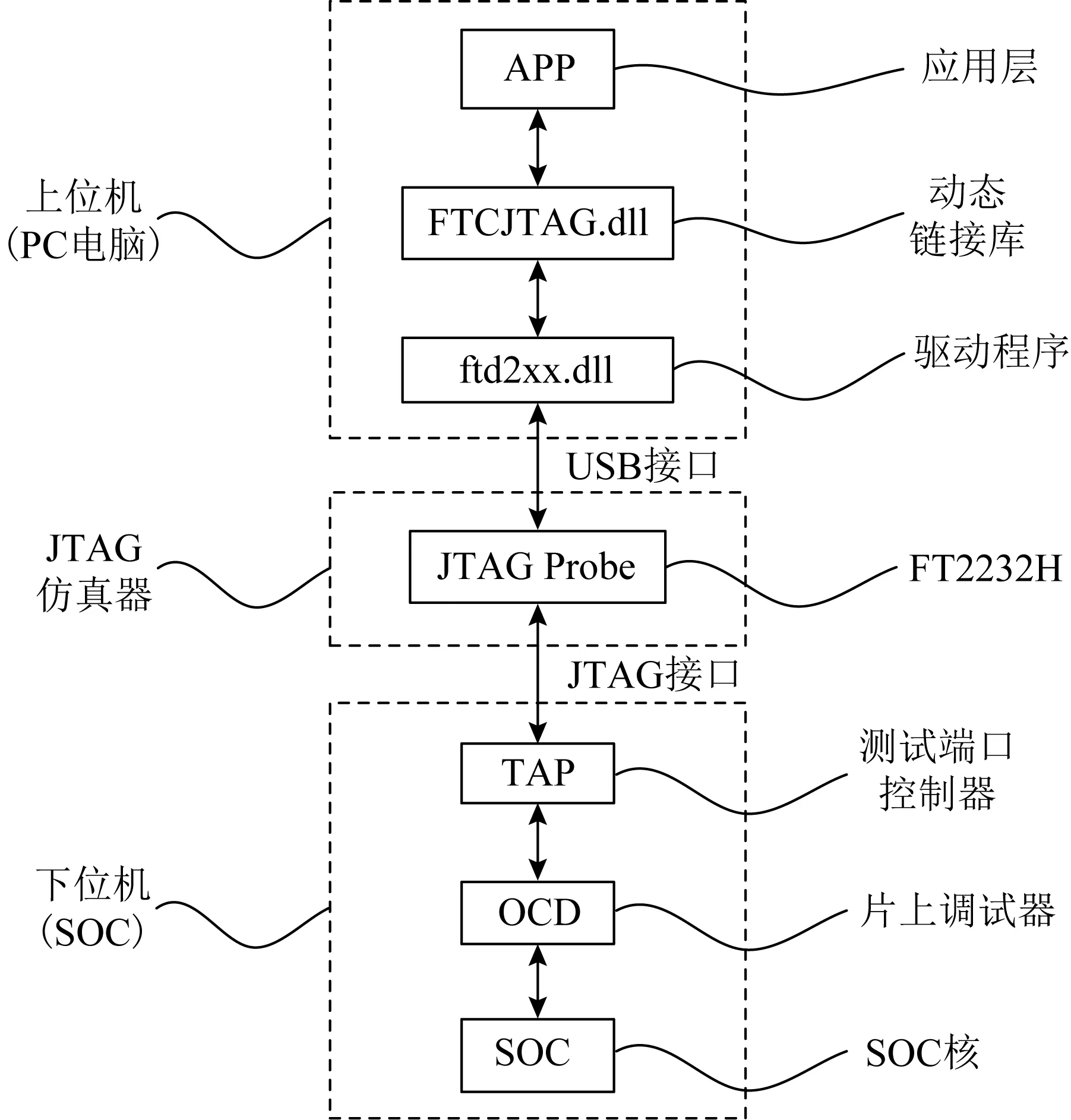

系统结构如图1所示,包含上位机、JTAG仿真器、下位机.其中上位机部分包含应用层APP以及FT2232H提供的动态链接库FTCJTAG.dll和驱动程序ftd2xx.dll;JTAG仿真器包含JTAG Porbe的物理接口,内部主要集成了FT2232H芯片,信号经过电平转换芯片后与下位机TAP通信;下位机部分包含测试端口控制器TAP、片上调试器OCD以及SOC核.上位机软件通过控制JTAG仿真器,给下位机TAP发指令,TAP收到指令后继续给OCD发指令,上位机软件和下位机软件就是通过OCD实现数据的交互.

图1 系统结构图

1.1 TAP控制器

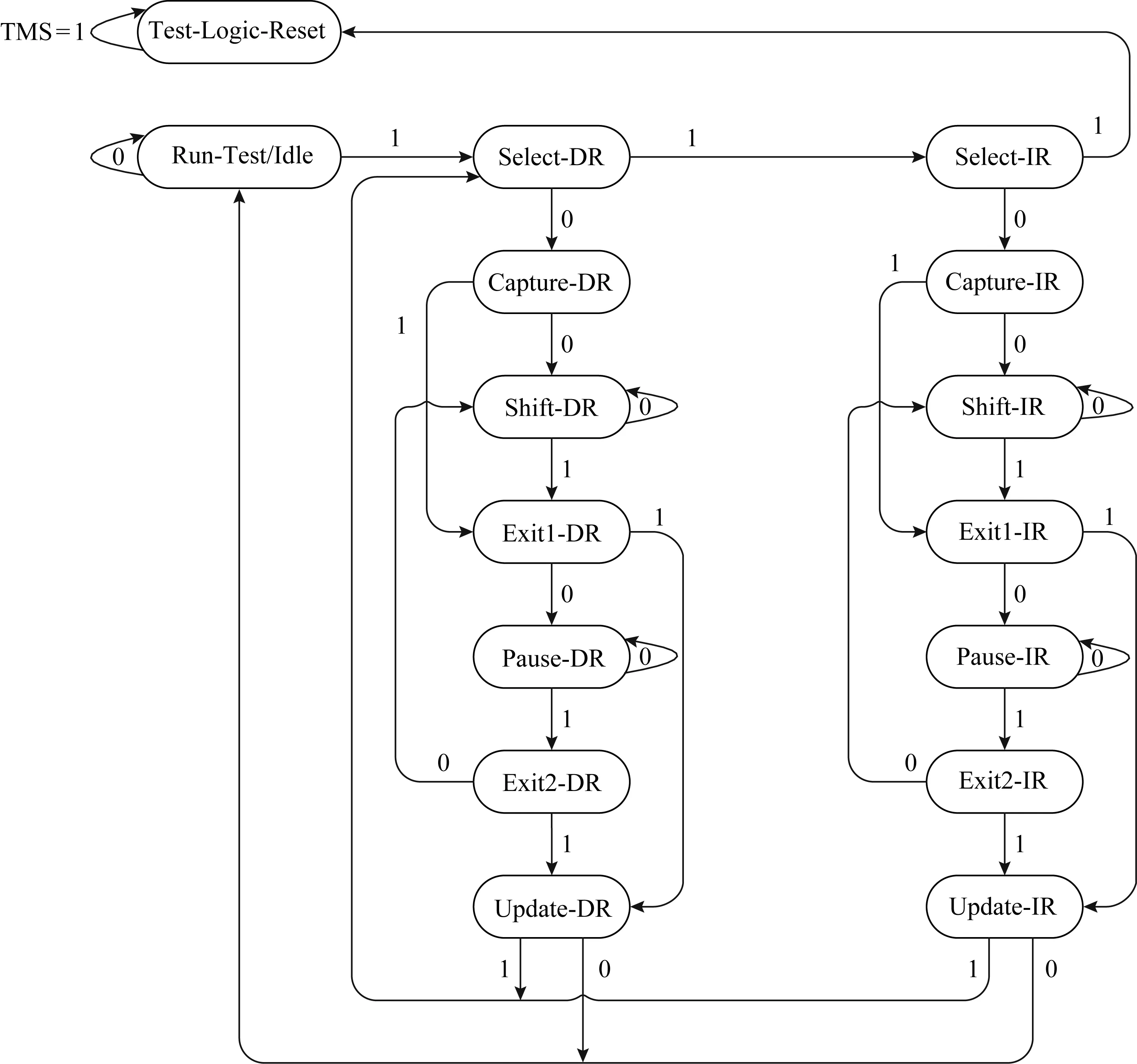

边界扫描测试核心控制器是TAP控制器.通过TMS和TCK,选取使用数据寄存器扫描、指令寄存器扫描及边界测试各个状态的控制器[3].在TCK的上升沿采样TDI和TMS,在TCK的下降沿采样TDO[4].TAP控制器的状态机如图2所示.TAP控制器分为4个部分,分别为复位、自检、指令寄存器扫描和数据寄存器扫描,一共有16个状态[5].

图2 TAP控制器状态机

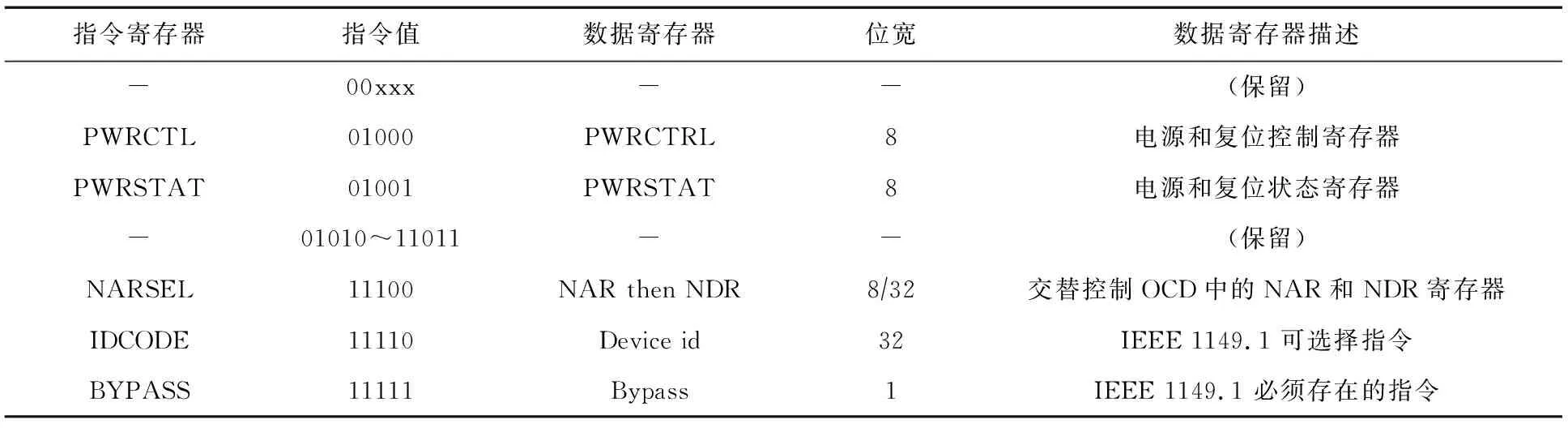

表1所示为TAP指令,TAP模块内部集成了这些寄存器,JTAG通过访问这些寄存器就可以控制TAP模块.

表1 TAP指令表

图3所示为JTAG接口时序图,TDI数据流格式从低向高发送,其状态机描述如下:

1)图3处在Run-Test-Idle模式.

图3 JTAG接口时序图

2)TMS经过1100后,进入Shift-IR模式,即TAP命令模式;TDI发送0x1C,即NARSEL命令.

3)TMS经过1,进入Exit1-IR模式.

4)TMS经过10,进入Run-Test-Idle模式.

5)TMS经过100,进入Shift-DR模式,即TAP数据模式;TDI发送0x8F,即NAR=0x8F.

6)TMS经过1,进入Exit1-DR模式.

7)TMS经过10,进入Run-Test-Idle模式.

8)TMS经过100,进入Shift-DR模式;TDI发送0x000072F0,即NDR=0x000072F0.

9)TMS经过1,进入Exit1-DR模式.

1.2 OCD调试器

OCD(on chip debugger)即片上调试器.在调试过程中,将实时跟踪功能和运行控制功能分开实现,用户通过专用的串行信号接口访问CPU核内的调试控制逻辑模块,获取片内各种资源,并实现CPU运行的停止和继续[6-7].

OCD模块初始化每条命令占用6个字节,第1个字节表示命令和数据标识,其中2表示命令,1表示数据;第2个字节表示位宽;第3~6个字节表示命令信息或者数据信息,低字节在前.如TAP指令“Bypass”:0x02,0x05,0x1F,0x00,0x00,0x00;TAP指令“读取设备ID”:0x02,0x05,0x1F,0x00,0x00,0x00;TAP指令读“取32字节设备ID号”:0x01,0x32,0x00,0x00,0x00,0x00;TAP指令“读电源和复位状态”:0x02,0x05,0x09,0x00,0x00,0x00;TAP指令“读取8位电源和复位状态”:0x01,0x08,0x00,0x00,0x00,0x00.OCD指令“置Debug控制寄存器”:0x01,0x08,0x87,0x00,0x00,0x00;OCD指令“使能OCD”:0x01,0x32,0x01,0x00,0x00,0x00;TAP指令“进入NARSEL模式”:0x02,0x05,0x1C,0x00,0x00,0x00.

当进入NARSEL状态后,无需再配置NAREL指令,直接NAR,NDR,NAR,NDR循环.其中NAR代表7位地址寄存器和1位读写状态,NDR代表32位数据寄存器.

2 SHA-1原理及加密认证设计

2.1 SHA-1算法原理

SHA-1算法能够将512位的输入数据压缩成160位的MAC输出.SHA-1算法运算过程大体可分为2个部分:

1)消息填充.

SHA-1算法将512位数据分为1组,对不满512位的数据进行填充,使填充后的数据长度为512的整数倍[8].数据填充的规则是在消息末尾填充“100…0”,使其长度为448,再填充上64位的消息长度.填充后的消息正好是512的倍数,按512位划分为n块数据,每一块数据按32位可以分为16组M0,M1,…,M15.

2)消息摘要计算.

SHA-1算法先将消息块的16组数据M0,M1,…,M15扩展得到80组数据W0,W1,…,W79,扩充方法如下[9]:

Wt=Mt, 0≤t≤15,

Wt=(Wt-3⊕Wt-8⊕Wt-14⊕Wt-16)<<<1,

16≤t≤79.

SHA-1设置了5个32位寄存器,分别标记为A,B,C,D,E,用于存储MAC计算值.这5个寄存器的初始值如下所示:

A=0x67452301;

B=0xEFCDAB89;

C=0x98BADCFE;

D=0x10325476;

E=0xC3D2E1F0.

SHA-1需要经过4轮运算,共80个步骤才能得到MAC值.0≤t≤79,A,B,C,D,E循环迭代操作步骤如下:

At=(At-1)<<<5+ft(Bt-1,Ct-1,Dt-1)+

Et-1+Wt+Kt;

Bt=At-1;

Ct=(Bt-1)<<<30;

Dt=Ct-1;

Et=Dt-1.

其中Kt和ft(x,y,z)分别是定义好的常数和逻辑函数,经过80轮循环迭代以后,由A,B,C,D,E构成160位MAC值.

2.2 加密认证设计

本文的烧写安全系统在保持烧写设备原有硬件结构不变的情况下,通过加入SHA-1加密算法模块提高嵌入式设备的安全性[10].

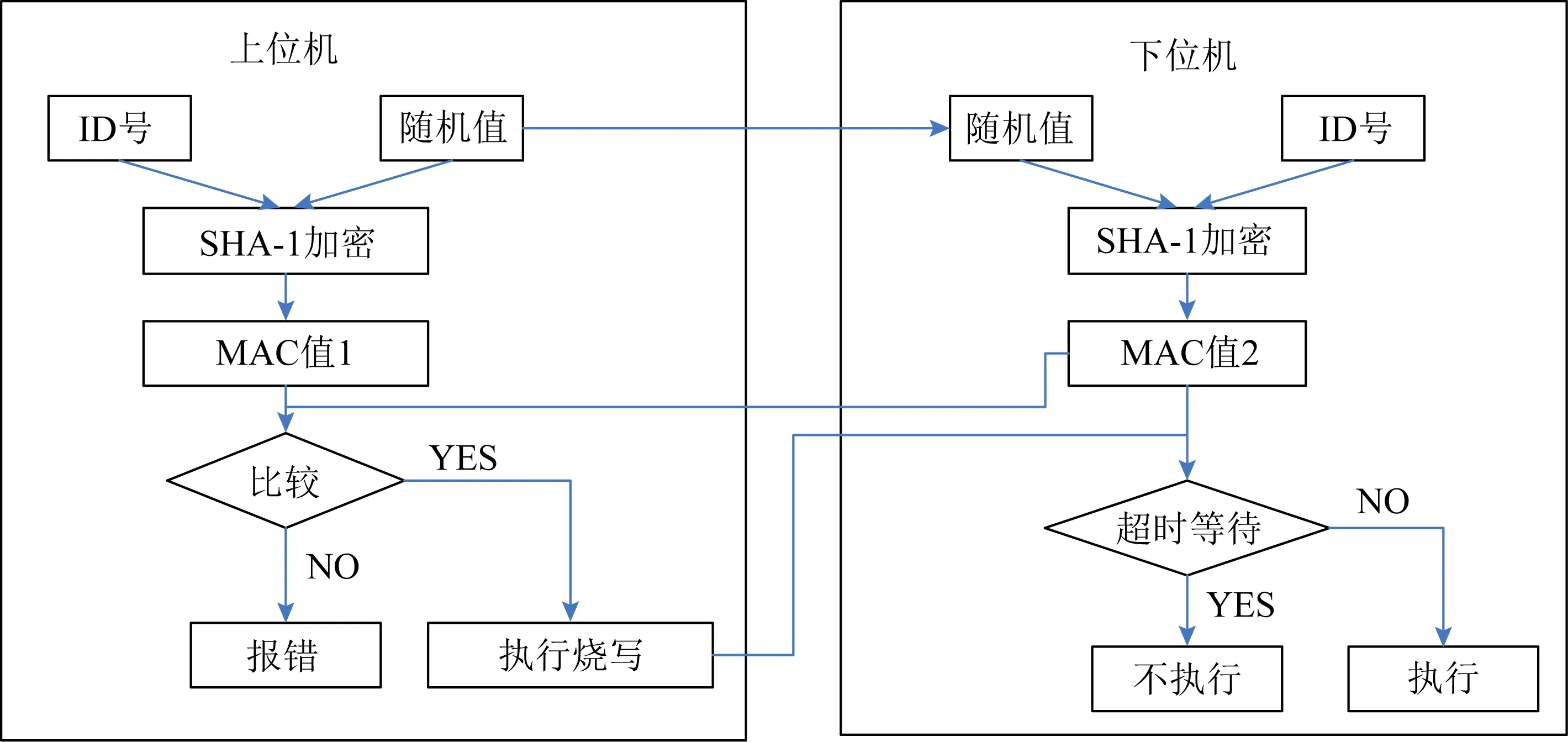

如图4所示,上位机和下位机有相同的ID号,大小64位,上位机随机生成448位大小的随机值,并把随机值发给下位机;上位机和下位机分别使用SHA-1加密算法生成160位的MAC值1、MAC值2,下位机把MAC值2发送给上位机,上位机对比2个MAC值是否相等,如果相等则执行烧写程序,不相等则进行报错.下位机设置超时等待时间,如果上位机在规定时间内发出烧写程序,则下位机执行烧写,否则不执行.

图4 加密认证构架图

3 系统软件设计

3.1 上位机软件设计

应用层使用C#编写基于FTCJTAG.dll的函数接口.图5所示为上位机主程序流程图,主要包含对FT2232H的初始化、TAP的初始化和OCD的初始化,初始化完毕后才能控制OCD模块操作SOC核进行身份验证及烧写程序.

图5 上位机主程序流程图

以擦除过程为例,需要先设置擦除的包数据,把包下载到下位机指定包处理区域,清除下位机给上位机的应答信号;然后运行下位机程序,下位机读到包的信息后,根据指令操作擦除命令,等擦完后给上位机发送应答信号;上位机接收到应答信号后停止下位机的运行,结束擦除线程.

3.2 下位机软件设计

下位机软件主要负责驱动程序的设计,包括下位机的正常初始化以及各种存储器的烧写驱动,下位机的初始化需要启动更快的CPU时钟,这样可以提高JTAG的访问速度和烧写Flash的速度.各种存储器的烧写驱动根据SOC生成本身的驱动代码定制而成.

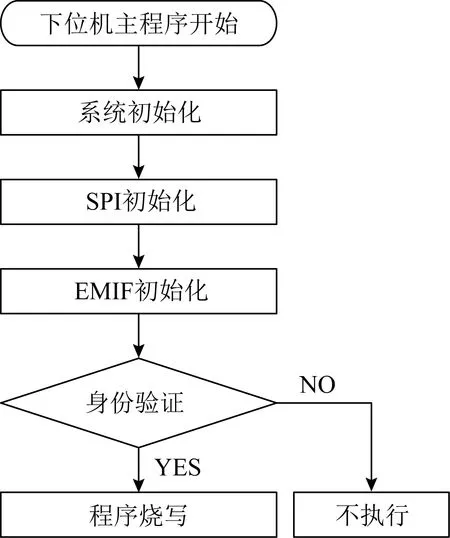

图6所示为下位机主程序流程图,主要处理SOC核的初始化、身份真实性识别和包命令判断.其中Flash的子程序又可以根据上位机的需要添加如ID读取、整片擦除、扇区擦除、空检测、读、编程等命令.

图6 下位机主程序流程图

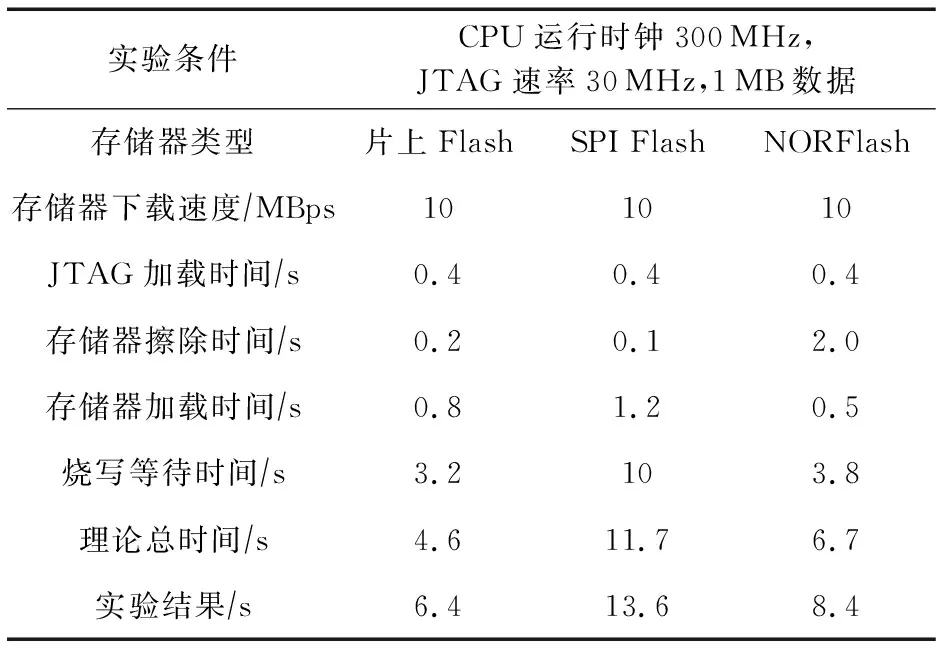

4 调 试

本文针对市面上比较常见的片上Flash,SPI Flash和NORFlash进行了实验[11].上位机和下位机在进行身份认证后,对JTAG加载时间、存储器擦除时间、存储器加载时间、烧写等待时间进行计算.本实验把SOC运行时钟设置为300 MHz,JTAG速率设置为30 MHz,通过上位机烧写1 MB数据到Flash上,具体时间如表2所示:

表2 不同存储器实验结果对照

5 结 论

本文介绍了一种基于SHA-1身份认证的Flash程序烧写系统.系统采用SHA-1算法进行身份认证,有效地提高了烧写的安全性;采用FTDI的USB2.0通信芯片FT2232H,快速地完成对SOC的Flash程序烧写.该系统方法在实验中得到有效的认证,且实验结果和理论较为接近,下载速度也已经达到极限,同时也适用于其他嵌入式芯片.