基于多相滤波的四路并行抽样算法及实现

徐 波

(中国西南电子技术研究所,四川 成都 610036)

0 引言

Joe Mitola 博士在1992 年美国通信系统会议上首次明确提出了可编程或可重构无线电系统的概念。理想的软件无线电架构如图1 所示,在信号接收侧:由天线接收的无线电信号经过低噪声放大后,利用数模转换器(ADC)对信号进行数字化处理,数字化处理的信号经过FPGA/DSP 等完成数字下变频、数字滤波、数字解调等信 号处理任务后送给控制与接口模块;在信号发射侧:从接口过来的基带信号会通过FPGA/DSP 完成数字调制、数字上变频和数字滤波等信号处理任务,再经模数转换器(DAC)变换为模拟信号,最后经功率放大器放大到足够功率,再由天线发射出去[1]。

图1 理想的软件无线电架构

在某型信号处理系统中,包含信号接收ADC 以及FPGA 处理等部分,数据采样相关的电路如图2 所示。该信号处理模块中共有三个模数转换模块ADC,一个时钟产生模块,一个主FPGA(FPGA1),一个控制FPGA(FPGA2)。其中模数转换模块ADC 的最高采样率为1 GS/s,采样位数14 bit,经过JESD204B 接口得到采样数据。时钟生成模块共有14 路输出时钟,分别给ADC 和主FPGA(FPGA1)输出采样时钟、JESD204B 参考时钟和工作时钟。控制FPGA(FPGA2)通过SPI 接口实现对ADC 和时钟产生模块的工作模式控制,以及通过两块FPGA 间的互连来实现对主FPGA 工作模式控制。主FPGA (FPGA1) 通过JESD204B IP 核接收ADC 的采样数据,并进行数据组合和简单处理,然后送至后续信号处理单元使用。

图2 信号处理模块模数转换相关电路

系统中的三个相同的ADC 模块,每个ADC 的采样率必须在320 MS/s、360 MS/s、575 MS/s 三个特殊频点下工作,且支持在线更新。要求在对任意一个ADC 的采样率更新时,不能影响其他ADC 的正常工作。但是时钟生成模块无法输出320 MHz 时钟,这就使得ADC 无法在320 MS/s 采样频点下进行工作。

为了满足系统对320 MS/s 采样率的需求,同时为了获取更加稳定的、抖动小的时钟输出,设计采用时钟模块生成了稳定可靠的960 MHz 时钟输出,并将该时钟信号与ADC 连接,然后在主FPGA 内做3 倍抽样,将采样率降到320 MS/s,最终输出320 MS/s 的采样数据。

1 四路并行滤波算法设计

假设输入信号为x[n],滤波器的单位冲击响应为h[n],由卷积定理可得到滤波器输出y[n]:

式(1)单位冲击响应h[n]中n 的取值范围为0,1,2,…,N-1,对h[n]做4 倍多相分解,则有h[n]、h[n+1]、h[n+2]、h[n+3],n 的取值范围为0,1,2,…,N/4-1,那么式(1)变为:

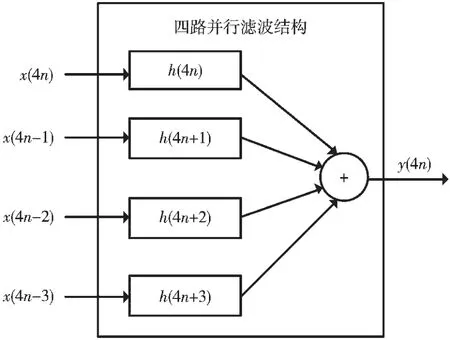

JESD204B 将输入信号做了1:4 的串并转换,即一个时钟周期输入四个数据x[4n]、x[4n-1]、x[4n-2]、x[4n-3],数据流如图3 所示。

图3 四路并行数据流

因此在做滤波处理时应该采用并行算法,滤波器每个周期输入四个数据,同时每个周期输出四个滤波后的数据。那么变为:

变换成卷积表示方式,则式(3)变为:

那么y[4n]的实现方式如图4 所示。

图4 四路并行滤波结构

同理可得到y[4n-1]、y[4n-2]、y[4n-3]的表达式为:

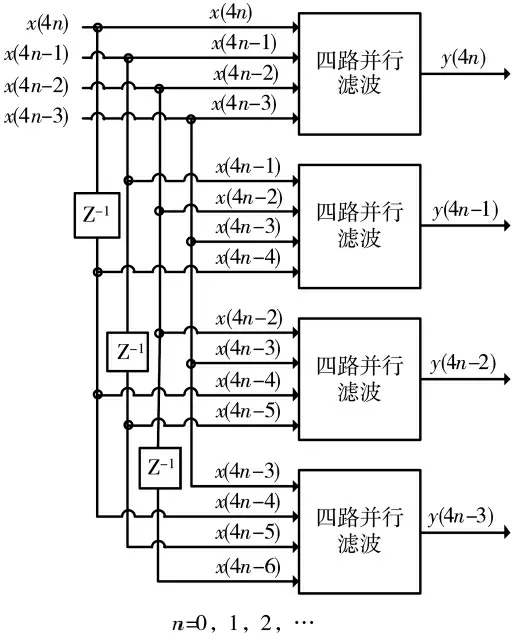

最终,四路并行滤波算法实现框图如图5 所示。

图5 四路并行滤波算法实现框图

滤波结束对输出信号进行抽样,即对数据y[4n]、y[4n-1]、y[4n-2]、y[4n-3]并行输出信号进行抽取处理。

2 算法仿真与滤波器参数提取

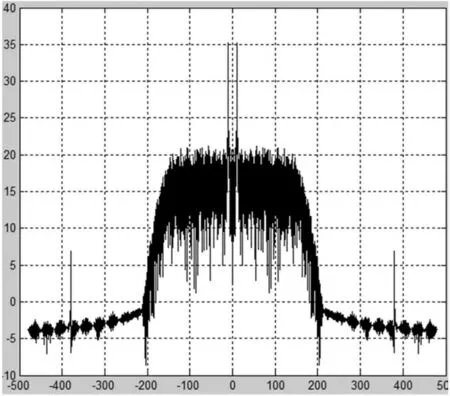

根据第一节对四路并行滤波算法的设计,对该算法进行仿真,验证算法能否按照系统要求正确滤波输出。设置采样频率fs=960 MHz,输入10 MHz、380 MHz 叠加的正弦波信号,对该信号添加SNR=5 dB 的噪声干扰,输入信号的幅频响应如图6 所示。

图6 输入信号幅频响应

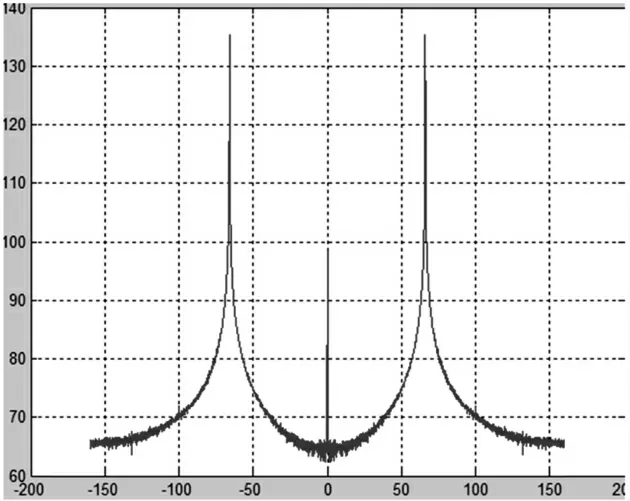

对输入信号进行1:4 的串并转换,将信号分解成四路信号并行输出。该四路信号经由各自的FIR 低通滤波器进行滤波,滤波器阶数取32,FIR 低通滤波器的系数设置为1/3。最后对四路并行信号进行并串转换,对转换后的信号进行分析,结果如图7 所示,证明经过四路并行滤波算法后能够正确得到10 MHz、380 MHz 两个频点。仿真完成后,在MATLAB 中提取四路低通滤波器的参数并对其进行量化,该参数值主要辅助后续的FPGA 实现。

图7 四路并行滤波输出幅频响应

3 算法的FPGA 实现及仿真

信号处理模块主要选取Xilinx 公司FPGA,四路并行滤波模块的实现如图8 所示,该模块主要用来实现图3中的四路并行滤波结构,是四路并行抽样算法的基本处理单元。该模块主要功能是输入的四路数据送入FIR低通滤波器进行滤波,并将滤波后的数据累加后输出,data0_i~data3_i 表示JESD204B 输出数据,data_o 表示滤波、累加后的输出信号,该信号会送给降样模块进行抽样。FIR低通滤波器采用Xilinx 公司的IP core,滤波器的参数在算法验证阶段产生,该参数值直接与IP core 结合使用。

图8 四路并行滤波通道模块框图

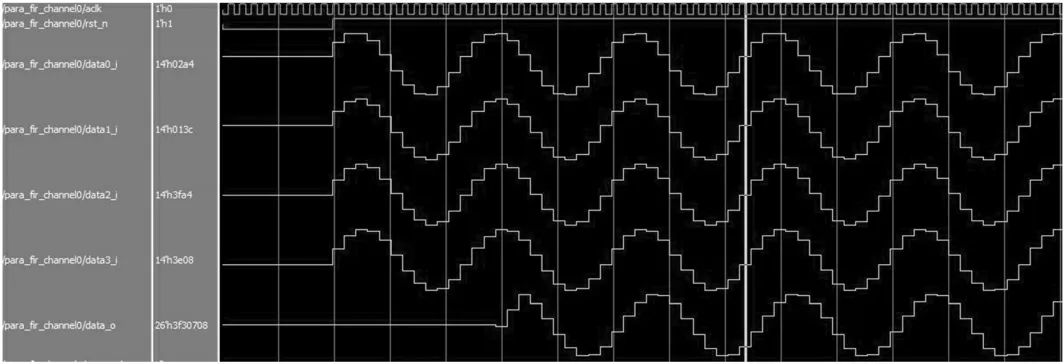

利用MATLAB 对算法仿真中产生输入信号进行1:4的串并转换,并将转换完的数据作为激励分别送给data0_i~data3_i,输入时钟clk 为240 MHz,data_o 表示输出,四路并行滤波通道的仿真结果如图9 所示,表明通过滤波后,信号正常输出。

图9 四路并行滤波通道模块的仿真结果

以四路并行滤波模块为基础,对四路并行抽样算法进行了FPGA 实现,如图10 所示,sample_clk 表示抽样时钟240 MHz;down_sample_clk 表示抽样时钟80 MHz;down_sample_data0~down_sample_data3 表示抽样数据;para_fir_channel0~para_fir_channel3 为四个并行滤波模块,四个模块分别用来对JESD204B 输出的四路信号进行滤波等处理;deci_filter 为降样模块,该模块主要用于在并行滤波模块分别对四路信号处理完成后,将输出信号送给降样模块进行抽取处理,抽取后的信号再送至后续信号处理单元使用。

图10 四路并行抽样算法实现框图

四路并行抽样算法的仿真结果如图11 所示,与上一节四路并行滤波的仿真方法类似,仍然利用MATLAB 对算法仿真中产生输入信号进行1:4 的串并转换,并将该四路信号作为激励分别送给data0_i~data3_i,图11 中选取了第1 路数据作展开,其中data_o_deci 表示para_fir_channel 模块送给deci_filter 的数据信号,data0_o 表示抽样信号。由data_o_deci 的信号波形分析四路信号在通过四路并行滤波模块后,信号被正确滤波输出;同时滤波信号经过降样模块,信号正确抽取。

图11 四路并行抽样算法的仿真结果

4 系统调试与结果分析

在完成四路并行抽样算法的FPGA 实现和仿真验证后,将代码综合后下载到信号处理模块进行测试。测试框图如图12 所示,时钟源向信号处理模块提供工作时钟,同时信号发生器向信号处理模块发送测试信号,信号处理模块将对测试信号先进行滤波,然后抽样输出,Vivado 对输出信号进行采集,MATLAB 对采集的输出信号进行分组分析,判断结果是否正确。

图12 信号处理模块测试框图

如果要查看更多的信号,图12 的测试系统的局限性就比较大,因为查看的信号越多,Vivado 中需要插入的探针(probe)就越多,这样导致的结果就是面积的增加和时序的劣化,而且可能会多次迭代综合,耗费的时间长,从而大大降低了工作效率。因而,搭建一个信号处理模块、MATLAB、Questasim 和Vivado 的软硬件联合调试环境就显得尤其必要。在该调试环境中,只需要Vivado 采集模块的接口和一些关键信号以外,利用Questasim 仿真工具查看模块内部的信号,这样除了减少了面积,对时序影响也比较小,同时还提高了调试效率。该软件硬件联合调试环境如图13 所示,信号发生器向信号处理模块送入信号后,Vivado 可以对模块接口和一些关键信号的信号进行采集,此时Questasim 利用这些采集的信号作为输入激励进行仿真,MATLAB 收集仿真结果并进行分组、串并转换等处理,或者将Questasim 输出的仿真结果与Vivado 采集的输出结果进行对比,用来判断结果是否正确。

图13 软硬件协同联合调试系统框图

软硬件联合调试环境搭建完成后,信号处理模块选择多个频率进行测试,实验结果证明均能输出正确的采样信号。以66 MHz 和74 MHz 为例,其中图14 是66 MHz的幅频响应,图15 是74 MHz 的幅频响应。

图14 66 MHz 幅频响应

图15 74 MHz 幅频响应

5 结论

四路并行抽样算法的设计主要为了解决ADC 在320 MS/s 采样率下,经由JESD204B 接收的信号在FPGA中无法处理的问题。在实际测试中将ADC 设置在960 MS/s的采样频点,信号经过JESD204B 转换为4 路并行信号,分别对该四路信号进行滤波、抽样,将采样率降样到320 MS/s,最终输出正确的抽样数据,经过试验证明该四路并行抽样算法模块能满足系统对320 MS/s 采样率的要求。