龙芯3A4000 主板VGA 接口电路设计及研究*

籍明慧,裴焕斗,宫健,张川川,庄杰

(1.中北大学 仪器与电子学院,山西 太原 030051;2.山西百信信息技术有限公司,山西 太原 030006)

0 引言

随着电子产业的快速发展,视频接口技术也从早期的BNC、S-端子、VGA 等接口发展到如今的DVI、HDMI以及DP 等数字视频接口[1],有了长足的进步。但是在视频数字化的潮流中,VGA 仍以成熟的技术优势、良好的兼容性和通用性以及相比之下较低的成本被广泛应用,是主板、嵌入式设备及高端显示器等设备上最主要的接口。同时VGA 接口对于那些需要模拟信号进行显示的机器是不可替代的,在技术产品革新替代中有着重要的作用。在针对国产化CPU 龙芯3A4000 进行主板开发时,面向国产机器替代,逐步实现国产化的要求,VGA接口的设计成为其中重要的一环。陈锴然[2]对不同视频传输标准的传输方式与优劣进行了分析对比,简要介绍了各种视频传输标准的应用场景;陈桂、朱丽婷、付宗宝及郑佃好[3-6]等人基于几种ARM 芯片控制ADV7120、ADV7125和THS8134B 等高性能视频D/A 转换芯片将LCD 扫描式接口转换为了VGA 接口,具体介绍了其电路设计。笔者在开发基于龙芯3A4000(MIPS 架构)的通用主板的过程中,提出一种利用高性能视频D/A 转换芯片ADV7125将DVO 总线数字信号转换为模拟信号通过VGA 接口实现视频输出的电路设计方法,该设计电路简单可靠,且有较好的防护性和信号质量。本文将详细介绍设计中的结构思路、电路设计及测试结果。

1 VGA 接口

1.1 简介及原理

VGA 是IBM 于1987 年提出的一个使用模拟信号的电脑显示标准[7],标准定义了VGA 信号外部接口互连的电气特性标称值、机械配接要求以及其信号传输原理(时序规范)。顾名思义,VGA 接口就是用来专门针对于VGA 标准输出数据的接口,具有多分辩率模式、模拟信号输出、数据传输速度快等优点,以其良好的兼容性、成熟性、可靠性被广泛应用于视频显示领域。

在进行视频显示时,第一步系统内部首先将视频信息解码为数字型图像信息缓冲至显存芯片中,然后高性能视频D/A 芯片调用数字视频信号经过模拟调制成为R、G、B 三原色模拟数据信号和行(HSYNC)、场(VSYNC)同步控制信号,最后信号遵循VGA 时序通过VGA 接口传输到显示设备中,其中行、场同步信号的作用是处理输入模拟信号以及联合起来控制VGA 的显示时序。由VGA 显示工业标准可知,VGA 的显示时序在不同显示模式和刷新频率下,各个模式行、场时序图轮廓基本一致,都由同步脉冲、显示后沿、显示时序段和显示前沿组成,只是每一段时序的状态持续时间不同。

1.2 VGA 接口引脚定义

VGA 接口的物理外形是一个15 针孔的插座,分为三排,每排五个针孔。其传输信号主要有以下几种类型:

(1)模拟数据信号:红、绿、蓝3 基色RGB 信号;

(2)同步控制信号:行/场同步信号(H/VSYNC);

(3)电源、地:1 个通用地,3 个对应彩色分量信号地,一个对应控制信号地,一个+5 V 电源。

其中行场同步信号(HSYNC、VSYNC)用来处理3 根RGB 彩色分量信号,同时配合起来控制VGA 的显示时序,当工作在不同模式时,行同步信号和场同步信号的波形也各不相同。VGA 接口引脚定义见表1。

表1 VGA 接口引脚定义

1.3 VGA 接口时序要求

前文提到,VGA 的显示时序是由行、场同步信号配合控制的。针对不同显示模式和刷新频率,VGA 接口的时序也有不同表现方式,但是其行场时序结构都是一致的,均由同步脉冲、显示后沿、显示时序段和显示前沿组成,只是其不同状态占用时间不同。图1 为VGA 的信号时序图。

如图1 所示,行、场同步信号在每行/帧开始的时候均产生一个的低脉冲信号,且对应的同步脉冲均为负脉冲,在难以分辨不同模式下同步脉冲的周期时,会将其反相处理到达区分效果[8]。

图1 VGA 信号时序

VGA 时序包括行、场扫描时序两个部分,其时序参数有四个部分:行(场)同步脉冲(tWH,tWV)、显示后沿(tHC,tHV)、有效显示区宽度(tHSYNC,tVSYNC)、显示前沿(tVH,tCH)。开始扫描时,第一步进行的是行同步操作,同步操作完成后开始真正的数据扫描工作[9]。TVSYNC 是完成一帧扫描所需要的时间,称为场扫描周期,其倒数被称为场频,又称刷新频率;行扫描时序与场扫描时序的结构是一致的,此处不再细说。其中各个状态所占用时间可通过刷新频率即场频得出,场扫描周期即为场频的倒数,行扫描周期则通过场扫描周期和所扫描行数计算得知。

2 接口功能实现整体结构

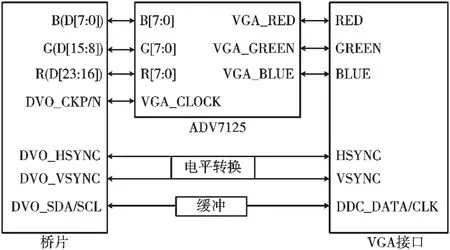

本文基于龙芯3A4000 CPU 的开发背景下进行VGA接口设计,整体采用龙芯3A4000+7A1000 的架构,通过龙芯7A1000 桥片(后文简称桥片)扩展显存以及VGA接口,利用高性能视频D/A 转换芯片ADV7125 将DVO 数字信号转换为模拟信号进行视频显示。整体结构如图2所示。

图2 整体结构框图

龙芯3A4000 是龙芯3 号系列处理器中首款基于GS464v 微架构的四核处理器,采用28 nm FD-SOI 工艺,主频稳定工作在1.5 GHz~2.0 GHz,其性能与龙芯3A3000相比提升达一倍左右[10]。桥片与龙芯3A4000 之间通过HT 高速总线相连,内部集成2D/3D GPU(100~500 MHz)、显示控制器以及显存接口,同时集成PCIE 以及USB、I2C、SPI 等多个高低速接口。

本次设计主要依托于桥片内部集成的显示控制器接口,桥片显示控制器支持双路DVO 显示,每路最大支持1 920×1 080@60Hz,支持RGB444、RGB555、RGB565、RGB888四种色深。桥片显示控制器提供了数据传输引脚和时序控制引脚,包括行场同步信号DVO_HSYNC/VSYNC 以及24 位数字数据信号DVO_D[23:0],其主要负责图像数据处理、VGA 接口时序实现以及配置芯片ADV7125 的工作模式,并把处理后的帧数据以点为单位送SDRAM 显示存储器。进行视频显示时,调用显存中图像数据经桥片处理后传输至D/A 芯片ADV7125 进行模数转换,最后模拟图像信号遵循VGA 时序通过VGA 接口传输到显示设备中。此次设计采用单片2 Gb×16 bit 的SUMSUNG公司的DDR3 SDRAM 芯片K4B2G1646Q-BCK0 作为显示存储器,可以满足高速数据收发存储的功能需求。

根据桥片设计手册规定,VGA 接口的同步信号需要由桥片显示控制器提供,故利用ADV7125 可以方便地将桥片的DVO 接口转换成VGA 接口。DVO 接口的数据位DVO_D[23:0]分别对应RGB888,即:DVO_D[23:16]对应RGB 信号的R[7:0],DVO_D[15:8]对应RGB 信号的G[7:0],DVO_D[7:0]对应RGB 信号的B[7:0]。在本系统中ADV7125 工作在RGB888 模式,故在设计中分别将DVO接口数据信号DVO_D[7:0]、DVO_D[15:8]、DVO_D[23:16]分别与ADV7125 芯片的VGA_B[7:0]信号、VGA_G[7:0]信号和VGA_R[7:0]信号相连接。ADV7125 芯片的时钟信号由桥片差分时钟提供,DVO 接口中的同步扫描信号HSYNC 和VSYNC 以及I2C 总线控制信号直接接到VGA接口。同时为了支持显示器热插拔功能,使用SPI_CSn2(复用为GPIO 功能)作为DVO 通道的显示器热插拔检测引脚。信号走向如图3 所示。

图3 整体信号流向图

3 电路设计

由于同步控制信号由桥片直接提供且VGA 时序已经确定,故利用ADV7125 将DVO 数据信号转换成VGA接口电路并不复杂,在设计时严格考虑到芯片的基本特性和信号输入要求即可。整体电路可分为桥片到ADV7125 芯片数据传输转换以及转换后信号处理并输出两个部分,下面就ADV7125 芯片特性、桥片到芯片ADV7125 电路连接、VGA 接口设计以及关键信号的处理做详细介绍。

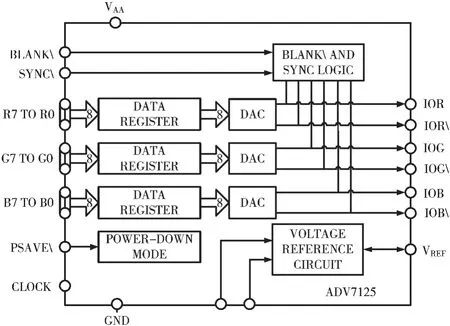

3.1 ADV7125

ADV7125 是一个单芯片高速数模转换器,吞吐量达330 MS/s,内置着三个独立的8 位高速分段式架构互补输出高速DAC,分别对应三个具有8 位寄存器的输入通道,用来接收数字信号并对视频数据做对应处理,24 位像素数据(颜色信息)在每个时钟周期的上升沿锁存至器件内,之后被提供给三个8 位DAC,然后转换为三个模拟(RGB)输出波形[11]。ADV7125 还有两个附加的控制信号BLANK 和SYNC,以与像素数据相似的方式锁存至模拟视频输出,分别在CLOCK 的上升沿锁存,以便与像素数据流保持同步,共同作为ADV7125 的输出信号。

ADV7125 采用单芯片设计,使用相同的电流源保证了单调性和低毛刺,片内运算放大器保证了满量程输出电流在面对温度和电源变动时的稳定性[12]。采用可以进行调节的+5 V/+3.3 V 电源供电,可配置省电模式,多应用于数字视频系统、高分辨率彩色图形、图像处理等方面。其功能框图如图4 所示。

图4 ADV7125 功能框图

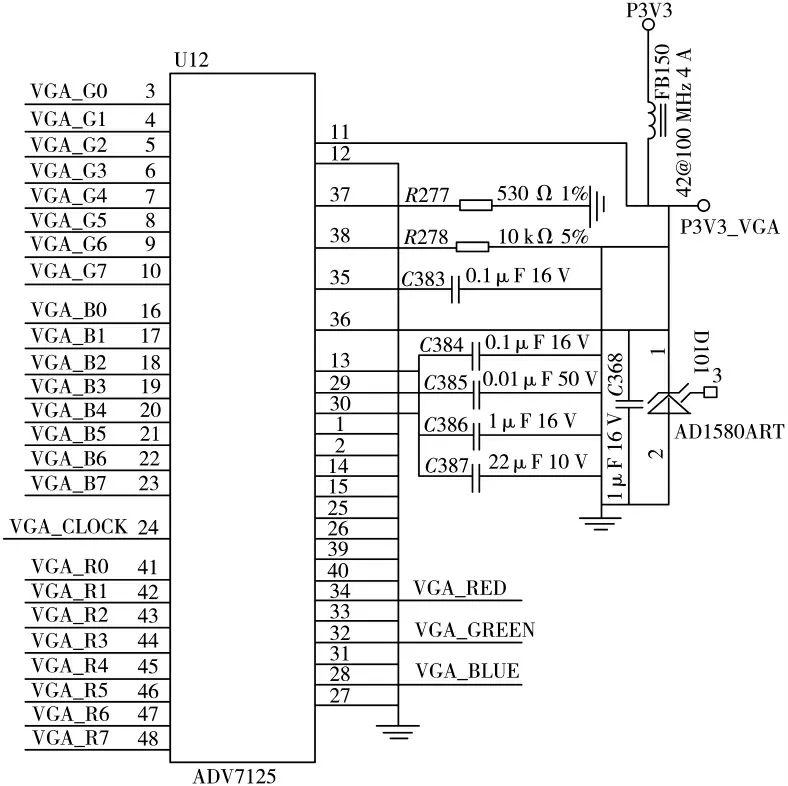

3.2 桥片与ADV7125 连接电路设计

由于VGA 接口的同步信号由显示控制器提供,故只要将DVO 接口数据的DVO_D[7:0],DVO_D[15:8]和DVO_D[23:16] 分别与ADV7125 芯片的VGA_B[7:0]、VGA_G[7:0]和VGA_R[7:0]直接连接进行数字信号传输,ADV7125 芯片的时钟信号由显示控制器内部时钟源产生的差分时钟提供。详细电路设计图如图5 所示。

图5 中VGA_B[7:0]、VGA_G[7:0]、VGA_R[7:0]、VGA_CLK 为桥片的输出端。COMP 端达到补偿内部参考运放的功能,通过在COMP 引脚与P3V3_VGA 之间连接一个0.1 μF 的电容来实现。ADV7125 是高精度DAC 芯片,对于参考电平的要求很高,如果以电阻分压的方式得到参考电压的话效果并不好,根据ADV7125 设计手册在电路设计时采用1.235 V 电压基准芯片AD1580 来产生参考电压,可以得到稳定的参考电平。ADV7125 的REST 引脚专门用来控制视频信号幅度,考虑到阻值要求,固定的530Ω用2个200Ω和1个130Ω的电阻来代替,便于后期调节。同时ADV7125 的SYNC 引脚用来控制单一复合同步输入,由于桥片的图形处理器可以生成水平同步(HSYNC)、垂直同步(VSYNC)和复合SYNC 信号,不需要ADV7125 产生同步信号,故将SYNC 拉到地,使其永久低电平。省电控制引脚PASVE 为低有效,此处同样将其接地,实现功耗降低。另外在布局设计时使用了尽可能短的电容引线,尽可能将电容靠近器件放置,将每个VAA 引脚单独去耦至地,最大程度地降低了引线电感。

图5 ADV7125 与桥片连接电路

3.3 VGA 接口设计以及关键信号的处理

考虑桥片VGA 接口设计要求、信号保护、信号缓冲等方面因素,设计VGA 接口电路如下,分以下三方面进行介绍,并在最后给出VGA 接口原理图。

输出模拟视频信号的处理:(1)在三个模拟输出的引脚上分别搭配一个75 Ω 的端接电阻到地,以达到最佳性能,并且在PCB 布局时尽可能地靠近了转换芯片去削弱信号反射。(2)在信号抵达接口之前,通过LC 滤波电路对模拟信号进行一级滤波优化处理;(3)使用快速开关二极管BAV99W 进行电路保护,BAV99W 相当于两个二极管,其开关速度快于一般二极管,其接法如图6 所示。

图6 BAV99W 连接方式

VGA_RED/GREEN/BLUE、LS7A_DVO_HSYNC/NSYNC 均经过此电路处理。公共端接所需要保护的信号,另两端一个接电源,一个接地,可以实现泄放超额电压从而稳定电压的作用。

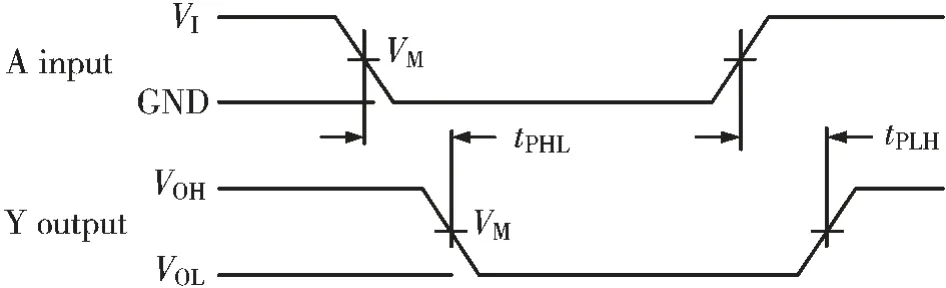

同步信号缓冲处理:视频同步信号由桥片显示控制器产生,由设计要求直接输出至VGA 接口,故需要对信号LS7A_DVO_HSYNC/N 做缓冲处理。本次设计使用74AHCT1G125GV 非逆变缓冲器实现信号缓冲,电路连接以及输入(A)到输出(Y)传播延迟如图7、图8 所示。

图7 74AHCT1G125GV 连接方式

图8 输入(A)到输出(Y)传播延迟

I2C 控制信号的电平转换:桥片的每个DVO 接口都自带了一组I2C 信号(使用GPIO 模拟),连接DVO 接口的转换PHY 芯片和显示器,专门用于显示器检测。根据桥片设计要求,必须使用该组I2C 信号连接显示器接口,而不使用PHY 芯片输出的I2C 引脚。桥片输出I2C 信号电平为TTL 电平,而VGA 接口需要电平为5 V,故需要对SDA/SCL 信号进行电平转换,此处设计使用常规的MOS 管实现电平转换,电平转换电路如图9所示。

图9 电平转换电路

视频信号、同步信号以及I2C 信号经过处理后连接至VGA 接口即可实现视频输出功能。除此之外,还使用了保险丝对VGA 接口进行了保护。VGA 接口及信号如图10 所示。

图10 VGA 接口及信号

4 测试结果

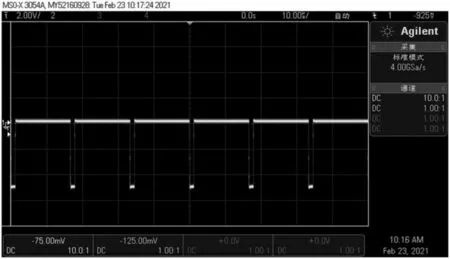

硬件调试后,针对VGA 接口标准进行测试,分辨率设定为1024*768@60Hz,利用MSO-X 3054A 示波器对行场同步信号HSYNC、VSYNC 进行测试,结果如图11、图12所示。

图11 HSYNC 波形图

图12 VSYNC 波形图

由图中分析可知:HSYNC 的周期为20.68 μs,VSYNC的周期为16.67 ms,与1 024×768@60Hz 模式下的VGA 接口时序要求一致,效果达到设计要求。同时,由模拟信号波形图可得知其输出电压在0~0.7 V 之间,均符合VESA标准及增强型数据显示通道标准。利用VGA 适配器将主板VGA 接口与显示器接口连接,显示器画面可正常显示,且无明显抖动,显示性能良好。

5 结论

本文在龙芯3A4000 的开发背景下进行了VGA 接口的设计,通过高性能D/A 视频转换芯片ADV7125 将桥片输出DVO 数字信号转换为模拟信号,并将模拟信号传输至VGA 接口,实现视频显示的功能。根据VGA 时序要求以及桥片设计要求进行电路设计,并考虑了信号质量以及接口防护方面的要求。经过测试,通过VGA 接口实现视频输出功能正常,性能良好,目前已成功应用于龙芯3A4000 主板,满足功能性、可靠性要求,同时达到了产品级别的要求。