图片WiFi传输与FPGA平台显示

东南大学微电子学院 陶 柱

为扩展FPGA在无线通信和图像处理方面的应用,设计了一个基于上位机、Marvell8801 WiFi模块、FPGA开发板和HDMI显示器的图片WiFi传输与显示系统。本文首先介绍了系统的功能结构,然后介绍系统的主要模块。最后通过功能测试,表明本系统的可行性。

随着智能时代的到来,各种图像传感器在日常生活中的应用几乎无处不在。相较于有线线缆,无线传输无疑极大便利了人们的生活,在智能时代图像的无线传输,也成为一大技术研究重点。近年来智能设备越来越普及,图像处理和显示技术的要求也愈来愈高。传统的CPU已难以满足图像处理的需要,对于图像处理的需求也是爆发性的增长。使用FPGA来进行图像的处理和显示,也是近年来的技术热点。

1 系统功能结构

本系统分为两大部分,第一部分为上位机,主要负责图片像素数据的读取,以及TCP的server端的搭建;第二部分为FPGA开发板及其外设,主要负责图帧数据的接收,缓存和显示器。本系统的功能结构框图,如图1所示。

图1 系统的功能结构框图

若想把图片从计算机无线传输到FPGA开发板上,而TCP/IP通信协议一般不支持图片格式的无线传输,因此需要把图片转化成TCP/IP支持的字节数据,可以是16位,24位或者32位的像素数据。

进行无线传输必须要进行无线网络的连接,这里是计算机和Marvell8801 WiFi模块的连接。对接收过来的图片像素数据进行图帧缓存,FPGA片内资源非常有限,需要使用片外资源,FPGA平台常用的片外资源是DDR。显示接口选择主流接口HDMI。

2 系统关键技术

2.1 图片像素读取

本系统传输的图片格式目前针对BMP格式的图片,从图片提取16位像素数据的txt格式的C/C++代码也是针对此格式的图片,其他格式图片该功能的实现也类似。

BMP格式图片的第18-21字节代表宽度,第22-25字节代表高度,第28-29字节代表每个像素的位数,第10-13字节代表像素数据的起始位置。根据所读像素数据的起始位置,可以读取整个图片的像素数据。读到的原始像素数据是32位,包括RGB888的值和8位透明度值(该值这里不做处理,默认不透明),经过量化压缩变换,可以得到对应像素16位的RGB565的值。

2.2 WiFi通信系统的搭建

WiFi通信系统包括两部分,一是上位机内socket编程实现的TCP server端,负责连接IP地址和端口,同时计算机连接WiFi信号;二是作为FPGA开发板外设的WiFi模块,通过SDIO接口与FPGA开发板连接。

套接字(sockets)是通讯的基石,是支持TCP/IP协议的网络通信的基本操作单元。可以将套接字看作不同主机间的进程进行双向通信的端点,它构成了在单个主机内及整个网络间的编程界面。套接字的服务进程和客户进程在通信前必须创建各自的套接字并建立连接,然后才能对相应的套接字进行“读”、“写”操作,实现数据的传输。

2.3 DDR3图帧缓存和HDMI显示

在FPGA中调用DDR3控制器IP来完成对该存储器的读写。本模块的设计是以DDR3控制器MIG(Memory Interface Generator)IP的使用为核心,该IP的输出信号与外部DDR3存储器的接口连接,输入信号是供用户侧使用的AXI接口。AXI接口总线共有5个通道,5个通道分为写和读两个事务。基于MIG IP的输入输出接口,图帧缓存和HDMI显示的整体设计框图如图2所示。

图2 图帧缓存和显示设计框图

3 功能测试

本系统主要测试两大功能,一是WiFi通信的实际测试,验证是否可以正常通信以及实际的传输速度;二是测试FPGA平台DDR3图帧缓存,进行HDMI显示。

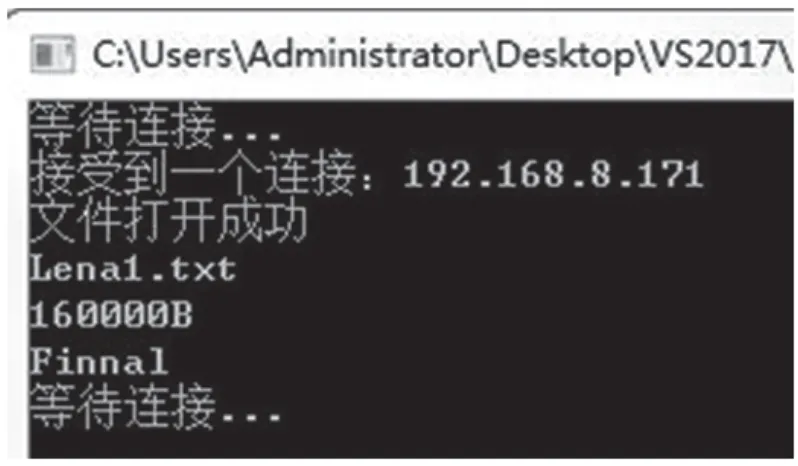

SDIO接口进行通信传输数据,选择一个160KB的Lena1.txt文件,测试WiFi系统是否可以通信,测试结果如图3所示。

图3 SDIO接口通信测试

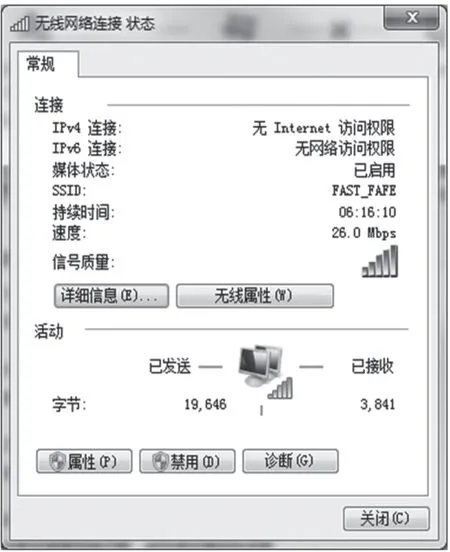

虽然可以通信,但还需要测试WiFi实际传输速度,测试结果如图4所示。

从图4可以看到,此时的WiFi信号FAST_FAFE并未接入宽带,而是与FPGA平台和上位机进行通信,且速度为26Mbps(约3.25MB/s),可以满足图片无线传输的需要。

图4 WiFi速度测试结果

FPGA平台DDR3图帧缓存和HDMI显示,实际效果如图5所示。

图5 FPGA平台图帧缓存和显示测试

综上,WiFi通信的功能基本实现,可以进行图片的传输,DDR3的图帧缓存和HDMI显示功能也正常。