基于TMS320DM8127的双路视频压缩传输终端系统设计与实现

张力锋,王涛

(1.陆装驻西安地区第七军代室,陕西西安710065;2.西安电子科技大学,陕西西安710071)

视频信息具有的直观、准确、高效等优点人们有目共睹。但是视频信息数据量过大,视频图像带来的高数据量问题已然成为视频实时播放和存储的一个瓶颈。而随着人们对高清视频的需求日益增长,高清视频带来的数据量更为庞大,高清视频的发展受限于信道带宽和存储器容量,仅仅依靠扩宽信道或增大存储器容量来解决该问题并不现实。因此,要使视频应用更加广泛,无论是实时播放还是存储都需要对采集到的原始视频图像进行压缩[1-2]。

文献[3]基于S3C2440/Windows CE5.0 平台设计了一款具有网络传输查看功能的嵌入式网络视频监控系统。该系统通过OV9650 CMOS 摄像头采集视频,采用H.263 算法对采集到的视频压缩后通过TCP协议进行网络传输。文献[4-5]基于TMS320DM365设计了音视频压缩传输系统,以MPEG-4 格式对视频压缩后通过EMIF 接口将压缩后的视频数据发送至FPGA 进行传输。文献[6-7]基于TMS320DM8168平台设计了高清视频采集系统,该系统支持双路高清视频的采集,实现了基于H.264 的视频编解码和基于RTSP 协议的视频网络传输[8-9]。

文中是基于某恶劣环境下多路视频监控项目开展的,以TI 公司的高性价比视频处理器TMS320DM8127 为核心,设计并实现了兼容高清和标清视频压缩传输的网络视频服务终端系统。该系统可以满足目前对不同分辨率需求下视频传输、播放及存储的需求。同时,为了克服复杂网络环境对系统的影响,设计实现了双网冗余架构,保证网络传输的可靠性。经实际测试验证,该系统在压缩码率、传输时延等方面满足项目要求,为相关场景的视频传输提供了设计参考。

1 视频压缩传输终端系统总体设计

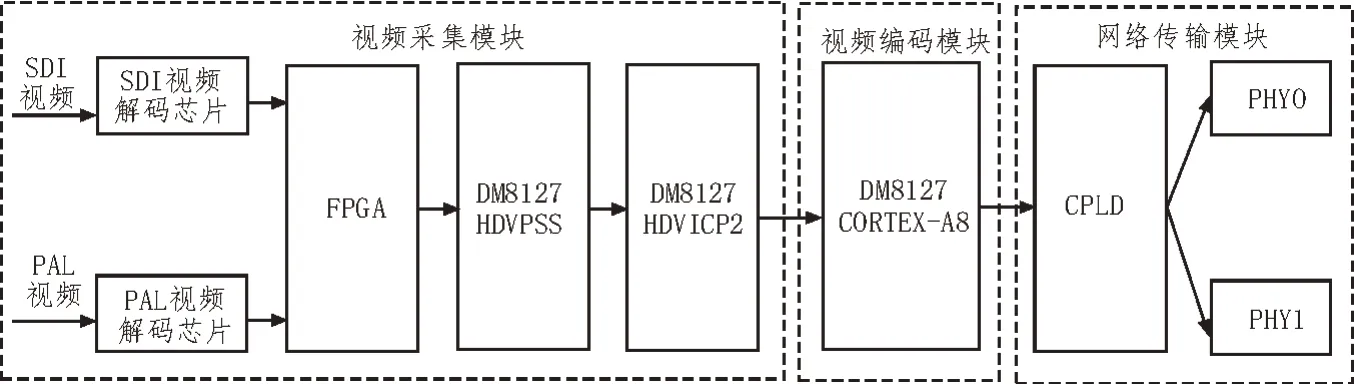

该文的目的是设计一个网络视频服务终端,对输入的不同格式视频进行数字压缩编码,并通过网络传输视频,支持实时播放,并配合后端存储阵列完成压缩后的视频存储[10-11]。网络视频压缩传输终端系统采取模块化设计,主要分为图1所示的几个模块。

图1 视频压缩传输终端系统框架图

1)视频采集模块:该模块包含高清1080P 视频源和标清720P 视频源、不同格式对应的解码芯片、FPGA 以及DM8127 的HDVPSS 核[12]。摄像机采集原始视频后通过解码芯片将采集到的模拟视频信号转换为数字信号,两路视频信号输入FPGA 完成信号切换和数据格式转换后进入DM8127处理器的HDVPSS模块。以上4个部分构成整个系统的采集模块。

2)视频编码模块:该模块是整个系统的核心,由DM8127 的高清视频图像协处理器完成,采用H.264算法进行压缩[13-14]。输入视频分辨率为1 920×1 080时,通过DM8127 的HDVPSS 模块缩放出一路720P的视频码流,然后将1080P 和720P 的视频进行双路压缩编码。输入视频分辨率为720×576 时,只需要一路压缩编码。

3)网络传输模块:该模块由DM8127 的Cortex-A8 核、CPLD 和两个网卡芯片构成。将压缩编码后的数据经过TCP 协议传输至电子存储阵列,同时利用RTP 协议分发至网络。考虑到实际应用场景网络环境的恶劣,网络模块采用双网冗余设计,CPLD 起到单刀双掷开关的作用。

2 视频压缩传输终端硬件设计

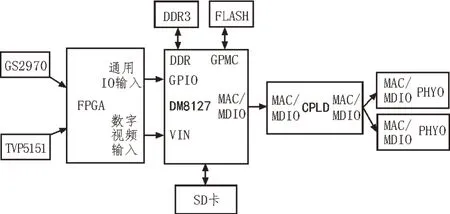

视频压缩传输终端系统设计需要将视频采集、视频编码、视频传输等功能集为一体。硬件设计整体架构采用FPGA 加DM8127 处理器[15]。硬件平台原理框图如图2所示。

图2 硬件平台原理框图

2.1 视频采集模块设计

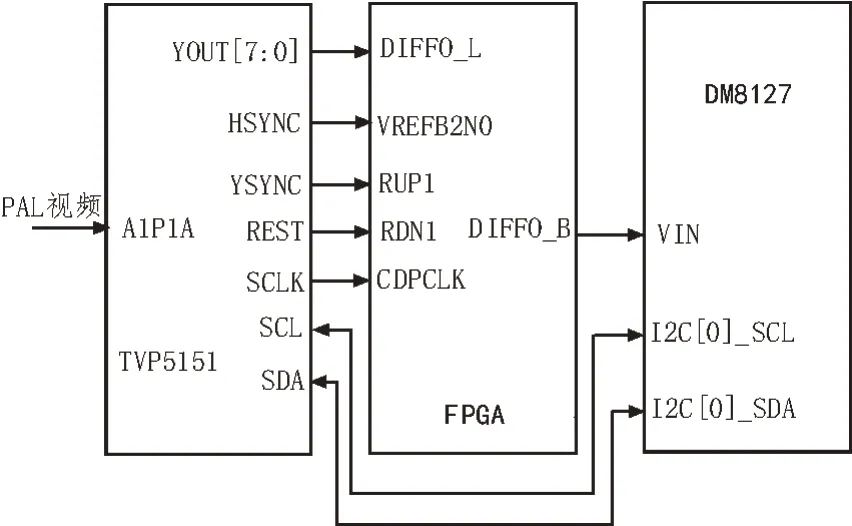

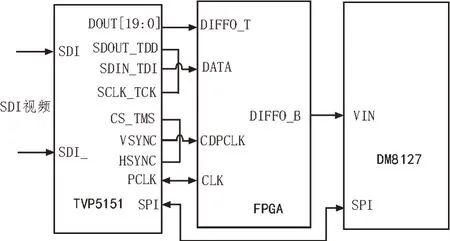

系统的视频采集模块可采集PAL 标清视频和SDI 高清视频。通过拨码开关选择其中一种作为视频源。PAL 标清视频译码芯片选用TI 公司的TVP5151 解码器,SDI 高清视频译码芯片选用GENNUM 公司的GS2970 解码器。硬件连接框图分别如图3、图4所示。

图3 标清解码芯片连接框图

图4 高清解码芯片连接框图

其中应该注意的是:

①TVP5151 视频输入的电压范围是0~0.75 V,所以在输入前端需要设计一个衰减器来降低输入振幅。

②时钟设计方面,TVP5151 由内部的锁相环产生系统和像素时钟,需要一个27 MHz 的时钟来驱动锁相环。 27 MHz 的晶振通过XTAL1 和XTAL2 引脚连接到解码器。连接晶振的电容之间需满足以下关系:CL1=CL2=2CL-Cstray,其中Cstray是相对于地面的终端电容,CL是27 MHz 指定的晶体负载电容。

③由于TVP5151 内部有多种电压,因此为了保障系统的正常工作,应先上1.8 V 电压后上3.3 V 电压,相隔100 ms 后给系统复位。

④GS2970 需要一个外部27 MHz 的参考时钟才能正常工作。这个参考时钟通过将27 MHz 的晶振连接到解码器的XTAL1 和XTAL2 引脚来生成。

⑤由于GS2970 被设计成在多电压环境下工作,所以允许任何加电顺序。为了将所有内部操作条件初始化为默认状态,RESET TRST 信号需要保持在较低的值。所有电源稳定后1 ms 复位。复位时,所有设备输出都被驱动到高阻抗状态[16]。

2.2 网络传输模块设计

考虑到该视频压缩阵列实际应用场景网络环境的恶劣,网络模块需要采用双网冗余设计。当系统启动时会将两个网卡芯片都进行初始化,初始化以后,一个网络芯片处于工作状态,另一个网络芯片处于等待工作状态即备用状态。网络冗余模块的任务是监测网络芯片的工作状态。若检测到工作网络芯片出现异常,则将当前网络芯片切换到备用网络芯片上。考虑到该项目的实际应用场景,选用了TI 公司的一款针对恶劣工业环境定制的千兆以太网物理层收发器DP83867IRPAPT,该收发器具有稳健性和高抗干扰度。

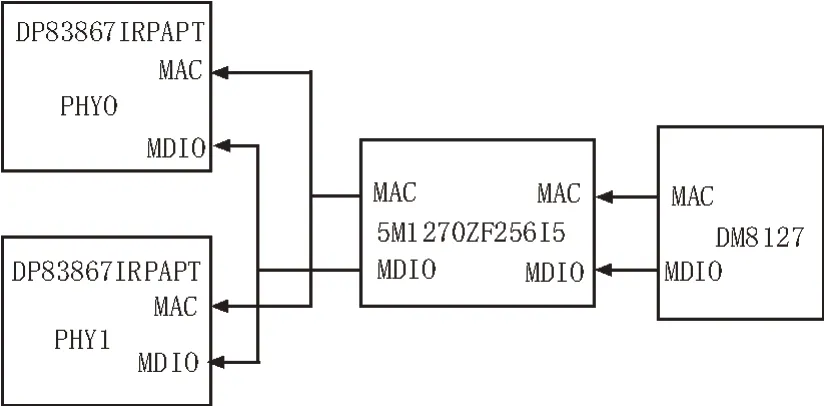

该设计采用CPLD 实现双网切换,CPLD 主要起到单刀双掷开关的作用。DM8127 的MAC 和MDIO连到CPLD,两片PHY 的MAC 和MDIO 连接CPLD。MIDO 的读写切换是判断MIDO 协议的读写状态bit,获取读写模式做MIDO 的方向切换,CPU 写模式同时写入两片PHY,读模式根据连接状态读取其中一片PHY。双网切换根据PHY 的Link 引脚高低电平来判断当前连接状态,Lan0 优先级最高,若Lan0 连接,则不管Lan1 状态是否正常都选择Lan0;若Lan0 未连接,Lan1 连接,则选择Lan1;若都未连接,则也选择Lan0。设计原理图如图5所示。

图5 双网冗余模块设计原理图

2.3 电源模块设计

电源设计是整个嵌入式系统设计的关键环节之一,良好有效的电源供应是系统正常运行的基础。该系统中各模块需要电压供应的主要芯片有PAL 解码芯片、SDI 解码芯片、核心处理器DM8127、网卡芯片、DDR3 芯片、FLASH 芯片以及SD 卡。

DM8127 芯片需要多种电源且需严格遵守一定的上电时序,上电时序如图6所示。上电时序必须是先上内核电压1.8 V,接着给DM8127 内的DDR 模块供电1.5 V,随后供给内核电压3.3 V,最后依次再给CVDD、ARM 核、DSP 核、HDVICP 核供1.2 V 电压。同理断电时也要先保证1.2 V 电压先断掉,之后3.3 V、1.5 V、1.8 V 依次断电。

图6 上电时序如图

2.4 存储模块设计

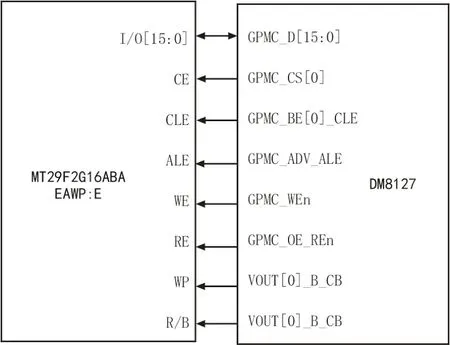

存储模块包括数据存储模块DDR 和引导程序存储模块FLASH。数据存储模块具有以下功能:①在视频采集阶段,缓存原始视频进行后续的视频处理。②在视频编解码阶段,缓存编解码视频数据供HDVICP 模块使用。③在视频组播阶段,缓存视频供Cortex -A8 模块使用。综上所述,系统运行时需要一块较大的存储空间来缓存视频,而处理器内部存储空间有限,不足以支持所需视频数据的缓存,所以需要外扩存储器DDR。引导程序存储模块负责存储Linux 系统的U-Boot、内核以及文件系统。由于DDR 掉电后不保存数据,所以还需要外部扩展FLASH 芯片。DDR 和Flash 模块连接框图如图7所示。

图7 存储模块设计图

3 基于IPNC-RDK的软件设计

TI 为开发者提供了MCFW 框架,所以文中只需要利用MCFW 框架下的LINK 设计合适的视频数据链路,就可以控制视频数据流向。

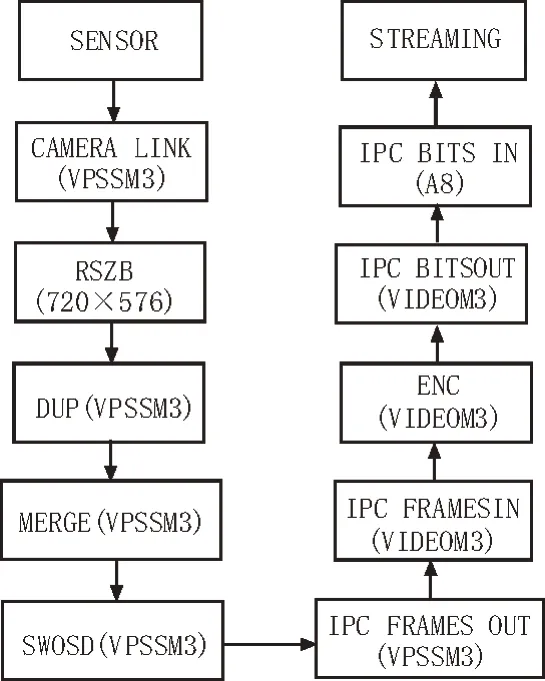

根据项目的实际需求,当输入视频为PAL 制式视频时,数据链路设计如图8所示,从CMOS SENSOR 采集到720P 的原始图像数据在VPSS M3 建立Camera Link,处理图像数据,首先ISS 调用Resizer对YUV 格式进行进一步处理,Resizer-A 把720P 的数据转换成YUV420SP(Y 分量独立保存,UV 交叉独立保存),统一保存到Dup,Dup 为一块独立的内存空间。Dup 数据通过Merge 对队列内的通道视频进行重新定义,定义之后的数据通过Swosd 完成字符的叠加后,通过Link 机制由M3 VPSS 核输出数据给VIDEO M3 核,VIDEO M3 核通过共享内存的方式得到Dup 的数据,再进行H.264 编码。Dup 的数据经过H.264 编码后,以bit 流的方式通过Link 机制,传给Cortex-A8,此时A8 运行的应用程序就可以得到bit流进行传输。

图8 标清输入数据链路流程图

当输入视频为SDI 制式视频时,数据链路如图9所示。从CMOS SENSOR 采集到1080P 的原始图像数据,在VPSS M3 建立Camera Link,处理图像数据,首先ISS 调用两个Resizer,即Resizer A 和Resizer B。对YUV 格式进行进一步处理,Resizer A 把1080P的数据转换成YUV420SP(Y 分量独立保存,UV 交叉独立保存),统一保存到Dup[0];Resizer B 也对初始的YUV 格式进行Resizer 缩小为720×576 标清图像,对于YUV420SP 格式(同上),统一保存到另外一个独立的缓存队列Dup[1],Dup[1]和Dup[0]是分开的。简而言之,Dup[0]的1080P 数据和Dup[1]的720P 数据分别传输至M3 VIDEO 核进行H.264 编码,经过H.264 编码后,以bit 流的方式通过Link 机制,传给Cortex-A8,此时A8 运行的应用程序就可以得到这两个不同分辨率的bit流进行传输。

图9 高清视频输入数据链路流程图

4 系统测试

4.1 测试环境

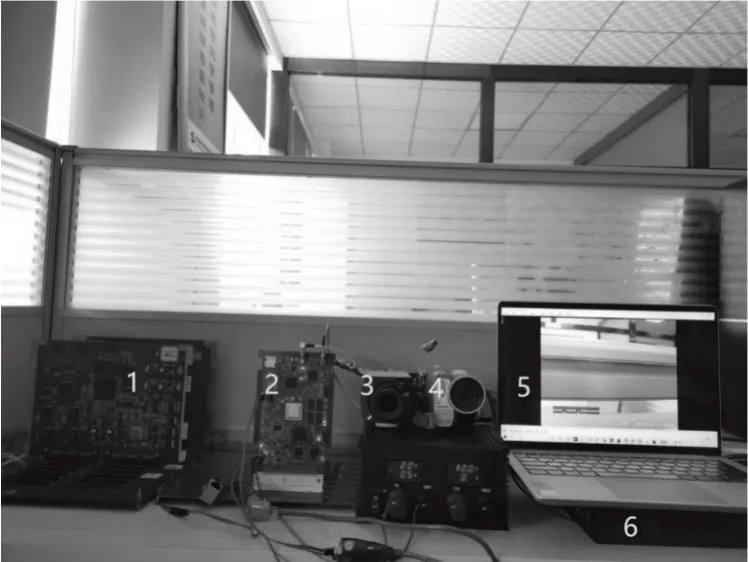

系统硬件平台搭建如图10 所示。标记1 为电子存储阵列,主要负责接收网络视频服务终端(标记2)传输的视频流并存储,通过以太网口连接至交换机。标记2 为网络视频服务终端,即所设计的基于DM8127 的双路视频压缩传输系统,通过以太网口连接至交换机。标记3 为SDI 高清摄像机,直接与网络视频服务终端连接。标记4 为PAL 标清摄像机,直接与网络视频服务终端连接。标记5 为PC 机,这里PC 机既当作客户端播放RTP 实时视频,也作为上位机发送指令。标记6 为交换机,负责将网络视频服务终端、电子存储阵列以及PC 机连入同一网段。

图10 测试环境搭建

4.2 延时测试

文中借助手机秒表测试系统的延时,以高清SDI延时测试为例,如图11 所示,将手机置于电脑左侧,摄像头同时对准手机屏幕和电脑屏幕,开启秒表计时,VLC 播放器可以清晰地观察到手机的秒表计时。通过计算图中手机秒表实际计时和VLC 播放器中手机秒表计时即可得到系统的延时。

图11 实测延时图

图11 中画面为随机选取,图中左侧为摄像头采集到的实际秒表时间,右侧为视频解码后的秒表时间。由ΔT=T-T′可得,图中延时为280 ms。为避免延时测试过程中的偶然性,文中采用大约每隔5 min记录一次,记录一小时,总计十二组数据的方法增加实验结果的可靠性。在随机测试的一小时内,延时最高为257 ms,最低为195 ms,经计算平均延时为231 ms。系统设计需求的延时最高不超过300 ms,经过大量测试,文中设计的系统完全满足延时要求。

4.3 稳定性测试

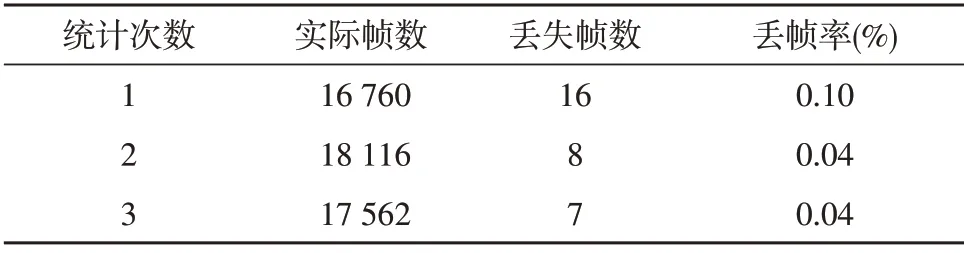

稳定性主要通过数据传输过程中的丢帧率来体现。文中大约每隔十分钟统计一次实际帧数和丢失帧数,连续测试一小时为一组,共测试十组。表1为3 次统计数据的丢帧率统计表。

表1 丢帧率统计表

经长时间测试,系统平均丢帧率最高为0.062%,表明系统稳定性良好。

5 结束语

文中设计并实现了基于DaVinci™系列TMS320 DM 8127 核心处理器的双路视频压缩传输终端系统。该系统可同时满足PAL 标清视频和SDI 高清视频输入,当输入SDI 高清视频时,为满足存储需求,将1080P 视频流缩放出一路720P 进行双路同时压缩,1080P 压缩后的数据经由RTP 协议发送至网络供组播播放,而720P 压缩后的数据经由TCP 协议发送至电子存储阵列。当输入视频为PAL 标清视频时,不需要做缩放处理,直接压缩再分别通过RTP 或TCP 发送。经过大量测试表明,系统的功能性、延时以及稳定性均满足项目需求。