基于DSP的基带噪声模拟模块设计

李莉,沈旭,马久青

(1.92126 部队,福建福州350007;2.常州国光数据通信有限公司,江苏常州213000)

在传统无线电通信基带信号处理模块的研发、生产、维修过程中,需要对模块的抗干扰能力进行测试,如抗白噪声干扰能力、抗电磁干扰能力、多普勒频偏追踪能力等。常见的检测设备有白噪声发生器、函数信号发生器、音频分析仪、毫伏表、信号叠加装置等多种设备,存在检测设备数量多、种类多,检测方法繁琐,效率低等问题[1-4]。为解决这些问题,提高检测效率,文中以C6748 数字信号处理器为基本硬件平台,设计了一种基于DSP 的多功能基带噪声模拟模块。

1 硬件设计

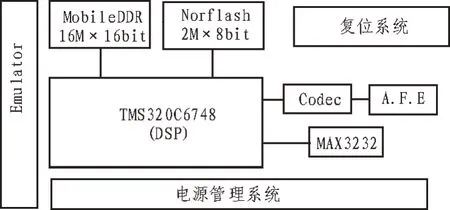

该设计由核心板和信号调理板组成,核心板主要为DSP 最小系统,其由DSP、MobileDDR、Norflash等组成。信号调理板由Emulator、电源管理电路(PM)、音频编解码器及其信号调理电路(A.F.E)等组成[5],如图1所示。

图1 总体设计框图

1.1 DSP最小系统

核心板DSP 采用TMS320C6748 浮点运算处理器作为控制和算法处理器,工作时钟采用25 MHz晶振,工作主频为300 MHz,挂载16 M×16 bit mDDR 闪存和2 M×8 bit FLASH 存储器,对外提供McBSP 同步串口和UART 异步串口[6],mDDR 闪存芯片采用MT 46H16M16LF,连接DSP 的DDR 控制接口,FLASH 存储器采用S29GL016 芯片,连接DSP 的EMIF 接口。

1.2 电源管理电路

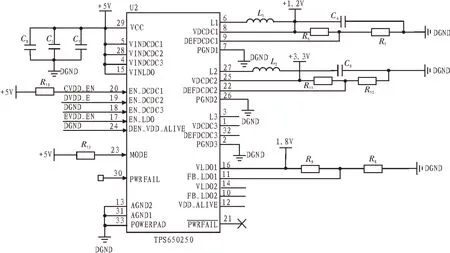

文中采用TPS650250 电源芯片实现电源管理电路,如图2所示。

图2 电源电路

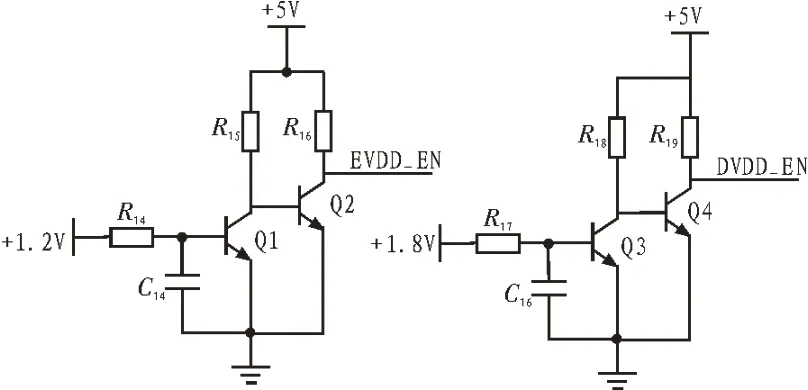

电源管理系统可输出的DSP 最小系统工作电压为+1.2 V、+1.8 V和+3.3 V,并通过三极管Q1~Q4进行上电顺序控制,其上电电压依次为+1.2 V、+1.8 V、+3.3 V,如图3所示。

图3 上电顺序控制

1.3 音频编解码电路

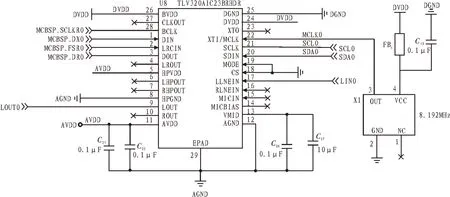

文中采用TLV320AIC23 数字音频编解码芯片实现音频编解码电路,其工作时钟采用8.192 MHz晶振,其SCL0 和SCA0 为芯片I2C 的控制接口,DSP通过I2C 接口进行工作参数的配置。DIN、DOUT和BCLK 为音频数字接口,DSP 利用MCBSP 接口与音频数字接口实现互通[7],如图4所示。

图4 音频编解码器电路

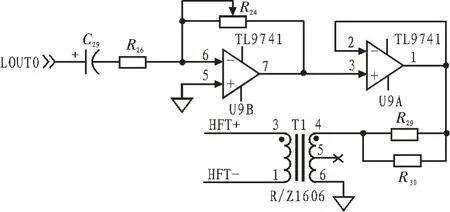

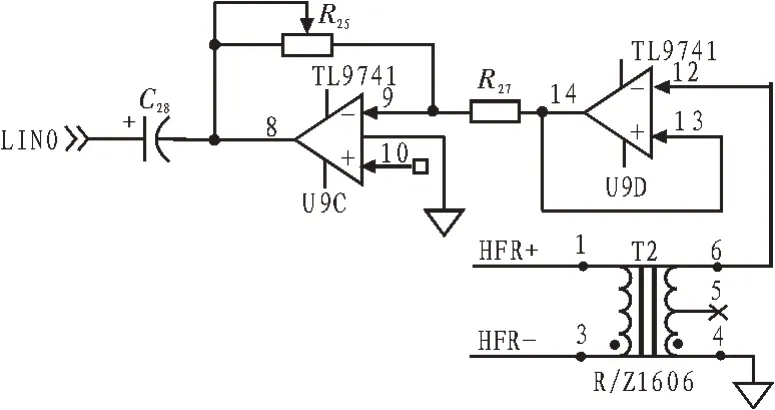

1.4 信号调理电路

信号调理电路部分采用变压器和运算放大器实现4 线平衡音频信号的输入、输出(模拟差分信号),如图5和图6所示。

图5 输出调理电路

图6 输入调理电路

2 算法设计

该设计主要涉及信号有效值计算、高斯白噪声生成、固定频率噪声生成3 种信号处理算法。

2.1 信号有效值

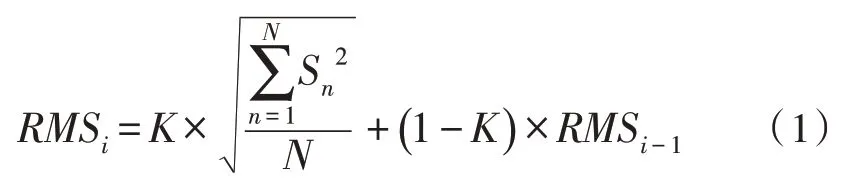

该设计的信号有效值计算采用实时功率加权计算方法[8],如式(1)所示。

其中,RMS为信号有效值,S为信号采样值,K为有效值实时性权值,N为有效值计算所取采样点数。K反映了有效值的灵敏度,N反映了有效值的实时性。综合考虑硬件平台的采样率和运算速度等性能,该设计中N取4 096,即每隔0.256 s 计算信号的有效值,K取0.8,即保证了有效值的实时性,又避免了有效值变化抖动过大。

2.2 高斯白噪声

极坐标法是生成数字高斯白噪声序列常见的方法[9-11],步骤如下:

1)产生平均分布的随机数U1、U2;

2)计算V1=2U1-1,V2=2U2-1,并计算S=V12+V22;

3)若S≥1,则返回步骤1);若S<1,则计算

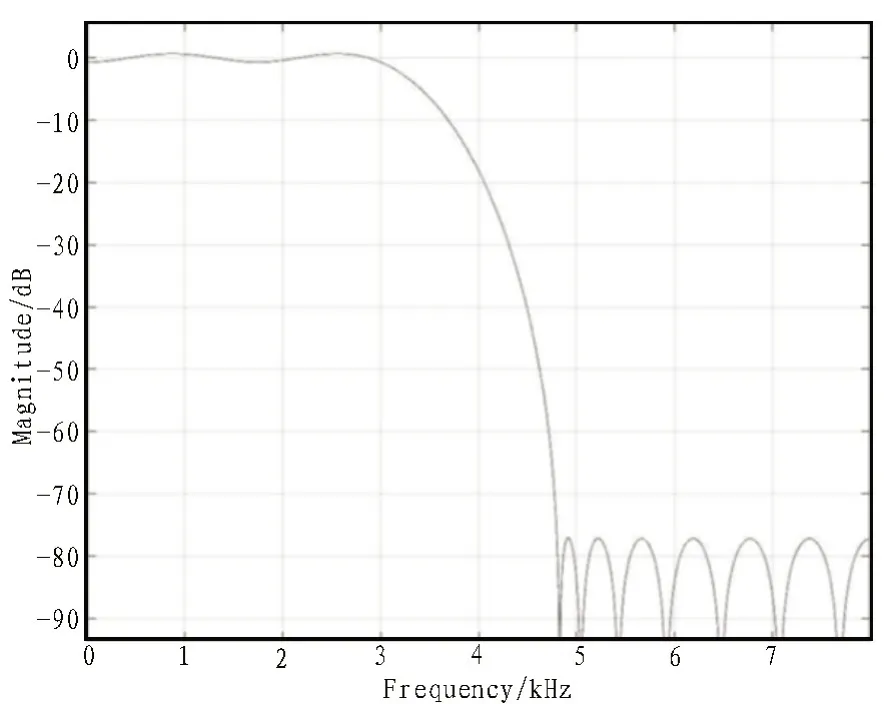

由上述算法可以得到一组正态分布的随机数列,即标准高斯白噪声序列,其功率谱符合白噪声功率谱特征。然而在检测短波基带信号调制解调模块抗白噪声干扰能力时,采用的是带宽为3 kHz 的窄带高斯白噪声,该模块采用带宽为3 kHz 的FIR 低通滤波器对标准高斯白噪声序列进行处理,从而得到所需的窄带高斯白噪声序列[12-15]。

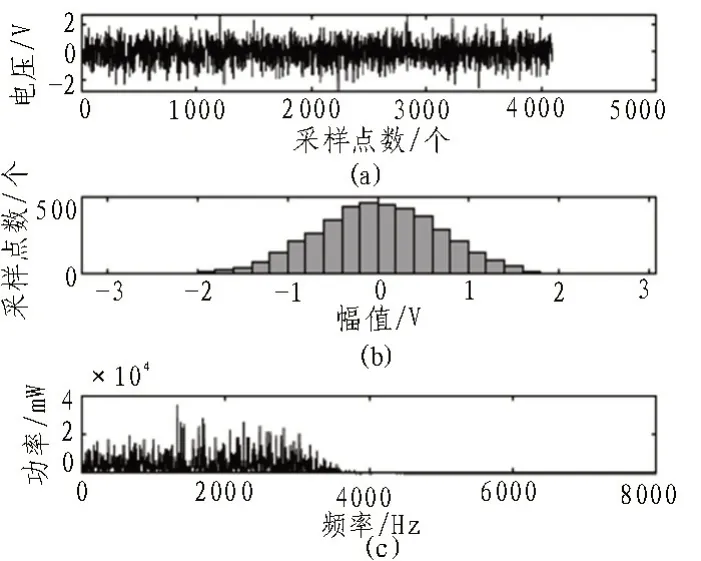

图7为该模块采用的Equiripple FIR 数字低通滤波器响应曲线,其通过频率为3 kHz,截止频率为4.8 kHz。图8(a)为带宽为3 kHz 的高斯白噪声序列,图8(b)为高斯白噪声功率谱,图8(c)为序列分布特性。

图7 Equiripple FIR数字低通滤波器响应曲线

图8 窄带高斯白噪声

2.3 固定频率噪声

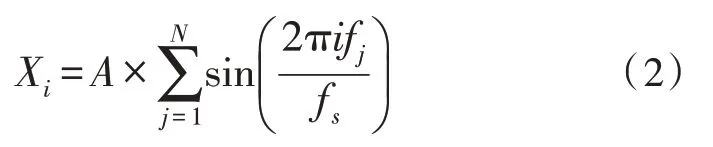

对于某些抗强单频率噪声干扰能力强的通信设备,在需要测试其抗干扰能力时,传统的测试方法是采用函数信号发生器或音频分析仪生成固定频率的音频信号,并利用信号叠加设备进行噪声叠加,若需加入多个频率噪声,则需多台设备[16]。这种测试方法存在设备过多、操作繁琐、信噪比不准确等问题,因此该设计中采用数字化方法生成所需噪声,如式(2)所示。

其中,Xi为信号采样序列,N为不同噪声频率的个数,fs为采样率,fj为噪声频率,A为噪声幅度系数,噪声频率fj应同时满足fj≤fs/2。

3 软件设计

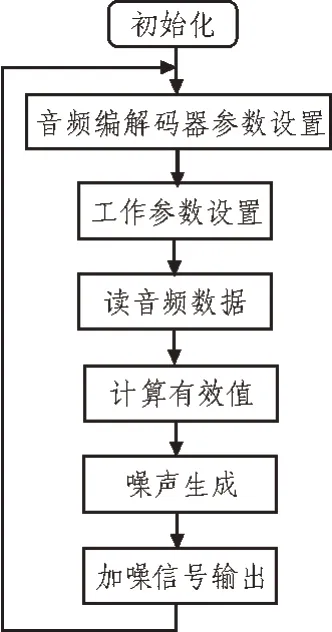

根据上述算法论证分析,该设计中首先进行系统初始化,包括通信端口(UART/I2C/MCBSP)、中断以及任务等参数,然后进行音频编解码器的参数设置。用户通过串口进行信噪比和噪声类型设置,DSP 计算生成用户要求的噪声类型,对采样的模拟信号进行有效值计算,根据用户需要的信噪比和输出加噪信号的幅度大小调整信号幅度和噪声幅度,将幅度调整后的信号和噪声进行叠加,得到用户所需的加噪信号,如图9所示。

图9 模块工作流程

3.1 系统初始化

系统初始化程序首先进行时钟初始化,主要是设置DSP 的工作时钟,DSP 的时钟源为25 MHz,通过设置PLL锁相环工作参数将DSP主频设置为300 MHz。其次是初始化UART、MCBSP 和I2C 3 个数字接口的工作参数并使能中断。再次是通过I2C 接口初始化音频编解码器的工作参数。

3.2 串口中断服务函数

系统软件通过串口中断服务函数接收用户传输的串口数据,保存信噪比、噪声类型和噪声频率等工作参数,同时在接收到查询命令时,输出缓存的有效值数据。

3.3 MCBSP接口中断服务函数

MCBSP 接口中断服务函数用于接收和发送数字音频数据,当音频编解码器完成一次采样后,产生接口中断,中断服务函数将16 bit 的采样值存入输入缓存,并将输出缓存的数据通过MCBSP 接口输出。

3.4 信号处理函数

该设计中当音频输入数据缓存存满时,进行数据处理,将缓存数据取出,按该文2.1 的方法进行有效值计算,并保存得到的有效值,供用户查询,然后按该文2.2 节的方法生成相同缓存长度的高斯白噪声序列,或按该文2.3 节的方法生成相应长度的固定频率噪声序列,然后按信噪比计算信号幅度,将输入的信号数据序列和噪声序列叠加后存入输出缓存,由MCBSP 接口中断服务函数进行输出。

4 仿真结果

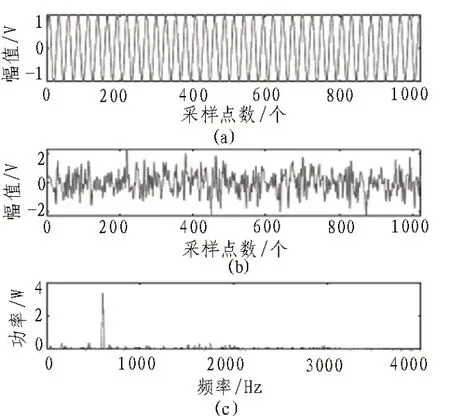

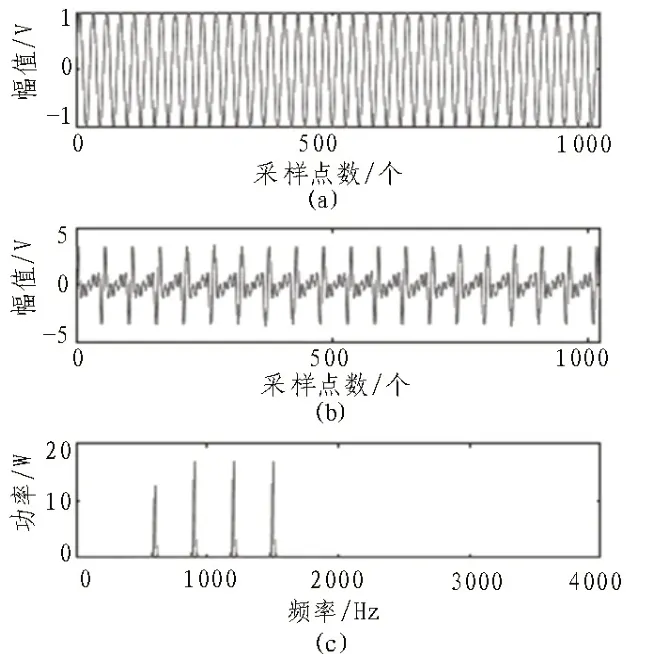

利用MATLAB 工具对该设计所采用的计算过程和软件工作过程进行模拟[17],见图10和图11。图10为叠加高斯白噪声效果图,原始输入信号是600 Hz 的正弦信号,输出加噪信号的信噪比为-3 dB。图10(a)为输入信号,图10(b)为叠加高斯白噪声后的加噪信号,图10(c)为加噪信号频谱。图11 为叠加900 Hz、1 200 Hz、1 500 Hz 3 种频率正弦噪声的效果图,图11(a)为原始输入信号是600 Hz 的正弦信号,图11(b)为加入固定频率噪声后的加噪信号,信噪比是-3 dB,图11(c)为噪声信号频谱。

图10 高斯白噪声效果

图11 多个单频率噪声效果

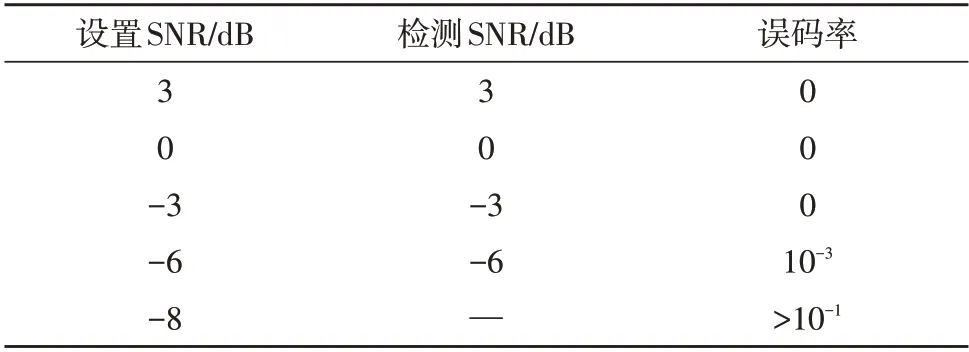

利用该设计模块对某短波通信调制解调器进行报文通信性能测试,其结果如表1所示。该调制解调器具备信噪比检测功能,在SNR≥-6 dB 的噪声环境下具有良好的通信准确率,设置SNR 为该设计模块输出的加噪信号的信噪比,检测SNR 为该调制解调器检测到的实际信噪比。当设置的SNR 大于-6 dB时,调制解调器正常通信,其检测得到的实际信噪比结果与设置基本一致,当SNR小于-8 dB时,已超出调制解调器工作范围,通信误码率较大,无法正常通信。

表1 信噪比模拟结果对比

5 结束语

该设计采用基于DSP 的信号处理硬件平台,实现了信号有效值计算、高斯白噪声生成、固定频率噪声生成等数字信号处理算法[18]。该设计具备操作简单、集成度高、自动化程度高等特点,在短波通信设备的实际研发、生成、维修过程中具有很好的实用价值。作为进一步的发展方向,该设计可以在多普勒频移模拟、多径衰弱等短波信道模拟功能方面持续完善,并实现自动控制、数据统计等智能检测功能。