SRAM 型FPGA 单粒子效应测试方法及试验验证

余永涛,陈煜海,余俊杰,龙伊雯,罗 军,王小强,罗宏伟

(工业和信息化部电子第五研究所,广州 510610)

0 引言

SRAM 型FPGA 具有逻辑密度高、可重复配置、可在线编程等优点,在硬件系统完成开发以至实际使用后,还可重新编程配置更改系统设计,因而在航天航空电子系统中得到广泛使用。然而,SRAM 型FPGA 器件对空间、临近空间至航空高度环境的辐射效应非常敏感,在空间粒子辐射下会发生单粒子效应(SEE),包括单粒子翻转(SEU)、单粒子功能中断(SEFI)和单粒子锁定(SEL)等,严重影响系统安全可靠运行。因此,应用于航天电子系统的SRAM 型FPGA 需要进行抗辐射加固并通过地面重离子辐照模拟试验及评估。

随着FPGA 技术的发展,国内近年来针对先进工艺SRAM 型FPGA 开展了较多的单粒子效应试验研究,但相关研究大多主要针对FPGA 内部配置存储单元和块存储单元的静态单粒子翻转效应、逻辑控制电路功能模块的单粒子功能中断效应及器件单粒子锁定效应的某一方面,而SRAM 型FPGA 器件阵列规模大、内部资源丰富、结构复杂,不同电路模块的SEE 敏感特性不同,因此对其开展全面准确的单粒子效应特性测试评估才能保证器件在空间辐射环境中应用的可靠性。

本文针对国产抗辐射加固SRAM 型FPGA 器件,在分析FPGA 内部电路结构SEE 敏感性的基础上,系统研究器件的SEU、SEFI、SEL 等单粒子效应测试方法,利用重离子加速器开展辐照试验验证,全面获得了配置存储器、块存储器和用户触发器等敏感模块的单粒子效应特性,并对试验结果进行讨论和分析,旨在为空间用SRAM 型FPGA 的单粒子特性全面测试评估和设计防护提供借鉴。

1 SRAM 型FPGA 单粒子效应测试类别及对象

主流的基于查找表结构(LUT)的SRAM 型FPGA 器件内部电路结构主要包括可编程逻辑模块(CLB)、输入输出模块(IOB)、互连资源(IR)以及块存储器(BRAM)、锁相环(PLL)、数字时钟管理器(DCM)等。

CLB 是FPGA 器件实现系统功能的主要资源,CLB、IOB、IR 等模块的大量可编程配置存储器(CRAM)都采用SRAM 单元或类似结构来实现。而SRAM 单元是单粒子翻转效应敏感结构,配置存储器数据出错将改变电路结构,导致FPGA 的系统逻辑功能错误。FPGA 器件的配置存储器控制着CLB 等可编程逻辑资源,其资源规模巨大,本工作所用FPGA 器件的配置存储位数接近600 Mbit,占总位数的95%以上,发生SEU 的概率最高。

BRAM 是FPGA 内部独立于逻辑单元的专用存储器,采用SRAM 单元结构存储用户程序和数据。BRAM 是单粒子效应敏感模块,如果其数据用于FPGA 控制,SEU 将会对器件功能产生影响。随着FPGA 阵列规模不断增大,BRAM 的存储容量也成倍增加,本工作所用FPGA 器件的BRAM 存储位数达到128 kbit。

此外,SRAM 型FPGA 的CLB 中每个逻辑单元(LC)通常包括1 个触发器(Flip-Flop),因而FPGA 器件中存在着大量的触发器单元。触发器的翻转会影响后续电路的输出,引发器件功能错误,故也需要进行单粒子翻转效应评估。

同时,FPGA 器件内部上电复位控制电路(POR)、通信接口控制逻辑(Select-MAP、JTAG)等全局控制电路的寄存器在粒子辐照下可能发生逻辑位翻转,导致器件功能中断。虽然此类寄存器数量较少,但其一旦发生功能中断,须通过全局重新复位或重新上电才能恢复,对器件的危害较大。单粒子锁定效应则会导致FPGA 器件电流快速增大,温度升高,从而发生功能异常甚至器件损坏,严重影响FPGA 的在轨安全,因而空间用器件一般应具有良好的抗SEL 特性,相关LET 阈值至少大于75 MeV·cm/mg。

根据以上SRAM 型FPGA 器件内部不同资源的SEE 敏感特性,SRAM 型FPGA 单粒子效应测试应包括单粒子翻转测试、单粒子功能中断测试和单粒子锁定效应测试,测试覆盖配置存储器、块存储器、触发器和寄存器等敏感结构资源。

2 SRAM 型FPGA 单粒子效应测试方法及测试系统

2.1 单粒子翻转测试方法

FPGA 单粒子翻转敏感单元主要是存储器,按资源类型分类,存储器分为内部配置存储单元和BRAM 存储单元。SEU 测试应覆盖上述2 类单元,包含2 部分的SEU 翻转数据。配置存储数据应覆盖所有的用户可编程资源,包括CLB、PLL、IOB 等。

SEU 测试采用回读码流数据方式进行,判断存储单元发生翻转的数量——利用Select-MAP 端口下载配置码流文件,回读配置存储器中的数据,与原数据进行比较。具体流程参见图1 所示:首先给测试电路板和测试器件上电,然后加载CRAM 配置存储器和BRAM 存储器码流进行配置,并将CRAM 码流和BRAM 码流作为Golden 码流存入SRAM;配置完成后,对CRAM 存储器和BRAM 存储器数据进行回读验证,确认FPGA 配置成功后方可开始辐照试验;辐照试验过程中对FPGA 的功能状态进行监测,判断器件功能是否发生SEFI,如果发生SEFI 则需要重新配置芯片。在无SEFI 的情况下,对CRAM 和BRAM 的数据进行回读验证,并与未接受辐照的SRAM 中存储的Golden 码流进行数据比对,统计出SEU 数据并上传给上位机。

图1 FPGA 存储器的单粒子效应检测方法流程Fig. 1 Flow diagram of SEE testing for RAMs of FPGA

CRAM 和BRAM 的SEU 测试包括动态测试和静态测试。静态测试是在辐照试验过程中FPGA 所有引脚接固定电平且无时钟信号,当辐照到规定注量后,回读CRAM 和BRAM 的数据,进行对比记录SEU 翻转数据,以评估存储单元本征的SEU 敏感性;动态测试是在辐照试验过程中持续配置并回读CRAM 和BRAM 的数据,相邻两次的回读时间间隔不超过1 s,进行对比并记录SEU翻转数据,直到试验结束,以评估在程序运行情况下存储单元的SEU 敏感性。

用户触发器是FPGA 中的基本时序单元,为了测试其SEU 特性,将CLB 触发器配置成移位寄存器链,覆盖所有的CLB 用户触发器,如图2 所示。试验前将测试样品上电复位,然后下载位流,再进行寄存器链移入数据,并静态辐照到规定注量;关闭束流并刷新器件,寄存器链移出数据进行对比统计翻转数。在统计寄存器链翻转数时,激励长度与寄存器链保持一致,激励的前一半是连续的1,后一半是连续的0。在静态辐照过程中,寄存器链的时钟处于关闭状态。

图2 移位寄存器链结构Fig. 2 Chain structure of shift register

2.2 单粒子功能中断检测方法

FPGA 中的单粒子功能中断检测主要针对内部功能电路,在本工作中SEFI 检测内容包括POR 和SMAP 两部分:POR-SEFI 检测FPGA 配置的用户功能是否存在,样品是否处在正常工作状态;SMAPSEFI 检测FPGA 的Select-MAP 端口是否正常工作。

POR-SEFI 检测通过监测FPGA 的DONE 信号实现——FPGA 完成配置后,其DONE 信号为高电平;在辐照试验过程中,如果DONE 信号变为低电平,则表示POR 电路发生SEFI,导致配置寄存器部分或全局复位,需要重新进行配置以进行新的测试,参见图1。

SMAP-SEFI 检测通过读写FAR 寄存器实现——如读出数据与写入数据一致,则表明Select-MAP端口工作正常;反之,则判断发生SAMP-SEFI,需要重新进行配置以进行新的测试,参见图1。

2.3 单粒子锁定测试方法

单粒子锁定效应的主要特征是导致器件电流的陡增,因此SEL 测试通过辐照试验过程中实时监测FPGA 器件的内核电源和I/O 端口电源的电流来判定是否发生SEL。辐照试验在常温、配置状态下进行,芯片偏置电压设置为最恶劣状态。

在辐照试验过程中,随着FPGA 器件SEU 的积累以及温度的升高,器件工作电流也会缓慢增大。为了更准确地甄别SEL,当电源电流突然增大到正常状态的2 倍以上,且program 管脚拉低进行软复位仍无法恢复时才能判定为SEL。发生SEL 后,应关断电源以保护器件。

2.4 SRAM 型FPGA 单粒子效应测试系统

SRAM 型FPGA 单粒子效应测试系统由单粒子辐照试验板、可编程电源、PC 机、示波器及远程控制计算机构成,如图3 所示。其中:单粒子辐照试验板主要由控制器、被测FPGA 芯片、串行通信接口、并行配置接口、电源接口以及其他外围电路构成;可编程电源为辐照试验板和被测FPGA 芯片的内核及I/O 端口稳定供电,并采集电压/电流数据实现SEL 的检测;PC 机是测试系统软件控制及显示系统的载体,通过USB 实现与可编程电源的通信,通过RS232 串口实现与单粒子辐照试验板的通信,通过并口对被测FPGA 芯片进行配置、回读、刷新等操作,实现SEU 和SEFI 的检测;示波器通过网线与PC 机相连,监测FPGA 芯片的POR 信号;远程控制计算机通过网线实现对PC 机的远程控制,实时监测试验情况。

图3 FPGA 单粒子效应测试系统Fig. 3 Schematic diagram of FPGA SEE test system

3 SRAM 型FPGA 单粒子效应测试试验方案

SRAM 型FPGA 单粒子效应测试试验分别采用中国原子能科学研究院的HI-13 串列静电加速器和中国科学院兰州近代物理研究所的HIRFL 回旋加速器产生不同LET 值的重离子进行模拟辐照,重离子的LET 值从低到高,数量不少于5 个以满足数据拟合的需要,如表1 所示。

表1 试验用重离子特性Table 1 Ion species, energy, LET value and range in silicon for FPGA test

试验样品为某国产SRAM 型FPGA,采用CMOS加固工艺,SPGA560 封装,内核电压1.5 V,I/O 电压3.3 V,逻辑单元数27 648,系统门数112 4022,总存储位数6 122 688 bit。辐照试验使用3 只器件,以3 只器件测试数据的平均值作为该型器件的单粒子效应特性数值。

4 试验结果及分析

4.1 单粒子翻转试验结果

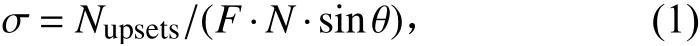

根据不同LET 值重离子的离子注量和相应的器件翻转数,可计算出该器件的单粒子翻转截面

N

为发生翻转数;N

为器件容量(当计算整个器件的翻转截面时,N

=1);F

∙sinθ

为有效离子注量,入射倾角θ

为入射离子束与器件平面的夹角,本试验的离子垂直入射,θ

=90°。为了保证测试结果的统计有效性,须离子注量达到10/cm或翻转数(事件数)达到100 以上。配置存储单元静态和动态单粒子翻转截面与重离子LET 的关系曲线如图4 所示。可以看出,配置存储单元的静态和动态单粒子翻转截面均随入射离子LET 值增大而增大,不同器件的试验结果偏差不大,LET 值达到30~40 MeV·cm/mg 时,单粒子翻转截面逐渐饱和。总体而言,在静态测试模式下,配置存储单元对重离子辐射更为敏感,单粒子翻转截面更大。

图4 配置存储单元静态和动态单粒子翻转截面与重离子LET 值的关系曲线Fig. 4 σ-LET curves for static and dynamic SEU testing of CRAM

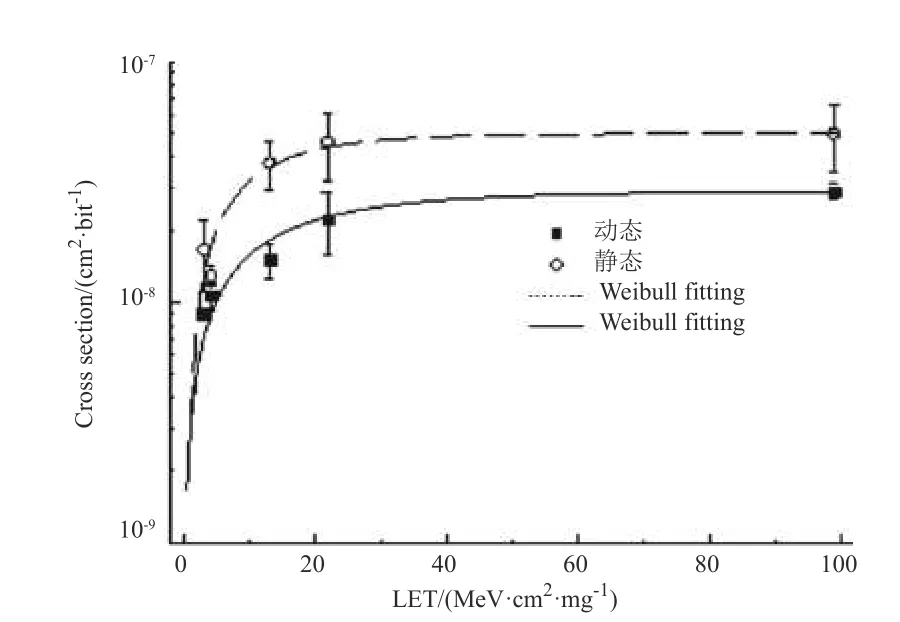

BRAM 存储单元静态和动态单粒子翻转截面与重离子LET 的关系曲线如图5 所示,与配置存储单元类似,BRAM 存储单元在静态测试模式下对重离子辐射更为敏感。

图5 BRAM 存储单元静态和动态单粒子翻转截面与重离子LET 值的关系曲线Fig. 5 σ-LET curves for static and dynamic SEU testing of BRAM

触发器Flip-Flop 的单粒子翻转截面与重离子LET 的关系曲线如图6 所示,在辐射离子LET 值较低时,不同器件的翻转截面差异较大。

图6 Flip-Flop 单粒子翻转截面与重离子LET 的关系曲线Fig. 6 σ-LET curve for SEU testing of Flip-Flop

利用OMERE 的拟合工具进行Weibull 函数数据拟合,得到配置存储单元的SEU 饱和截面(σ

),取10% SEU 饱和截面处对应的LET 值为SEU 阈值(LET);同时,Weibull 拟合得到BRAM存储单元和Flip-Flop 单元的SEU 饱和截面以及SEU 阈值,汇于表2。

表2 SRAM 型FPGA 的SEU 试验结果Table 2 SEU test results of SRAM FPGA

通过表2 可以看出,在取10% SEU 饱和截面处对应的LET 值为SEU 阈值的情况下,LET值最 低 达 到1.0 MeV·cm/mg,换 算 到 整 个 器 件 的SEU 最大饱和截面为0.376 cm/device,显示SRAM型FPGA 对SEU 非常敏感,需要采取系统级层面的加固措施,如码流刷新、三模冗余等。相对于动态测试模式,配置存储器和BRAM 存储器在静态测试模式下对SEU 更为敏感,表现在饱和截面更大,LET值更低。以静态测试结果表征器件本身的抗SEU 能力,用于器件在轨失效率预估的结果更为保守;器件实际的在轨翻转频次还与器件资源利用情况相关,因此将动态测试结果用于器件在轨失效率的预估更接近实际使用情况。虽然FPGA 器件的触发器数量远少于配置存储器和BRAM 的存储位数,但其SEU 饱和截面和SEU 阈值与CRAM 和BRAM 的相当,需要进行地面单粒子效应辐照试验评估。

4.2 单粒子功能中断试验结果

FPGA 的单粒子功能中断试验结果如图7 所示。可以看出,SRAM 型FPGA 在辐照试验中多次出现Select-MAP 端口功能中断的情况;出现Select-MAP 端口数据异常时,在不断电条件下重新进行FPGA 配置可恢复正常。

图7 FPGA 单粒子功能中断的截面与重离子LET 值的关系曲线Fig. 7 σ-LET curve for SEFI testing of SRAM FPGA

Weibull 数据拟合得到SEFI 饱和截面为1.24×10cm/device。取10% SEFI 饱和截面处对应的LET 值为SEFI 阈值,其值为1.2 MeV·cm/mg。一般将单粒子效应阈值低于15 MeV·cm/mg 的器件定义为单粒子效应敏感器件,因此该SRAM 型FPGA 器件属于SEFI 敏感器件,空间应用前需要进行系统加固。

4.3 单粒子锁定试验结果

FPGA 的内核电流约250 mA,I/O 电流为20 mA,在单粒子锁定测试过程中,随着辐射离子注量的增加,FPGA 的内核电流缓慢增大,但未达到SEL 的设定电流阈值;离子注量达到1×10/cm后试验结束,进行重新配置软复位后芯片电流恢复正常,表明未发生SEL。随着工艺的进步,通过工艺加固的SRAM型FPGA 的SEL 阈值已大于99.8 MeV·cm/mg,具有良好的抗SEL 特性。

5 结束语

本文基于SRAM 型FPGA 内部不同电路结构的SEE 敏感性分析,系统研究了SRAM 型FPGA的单粒子效应测试方法,包括配置存储器、块存储器的静态和动态SEU 测试、用户触发器的SEU 测试、全局和局部逻辑控制电路的SEFI 测试、整个器件的SEL 测试等。利用重离子加速器对辐射加固SRAM 型FPGA 进行单粒子效应辐照试验,分别获得了其静态SEU、动态SEU、SEFI 和SEL 等单粒子效应特性。结果表明:通过我们提出的方法可以全面有效地测试和表征SRAM 型FPGA 的单粒子效应特性,所测试抗辐射加固SRAM 型FPGA 具有良好的抗SEL 特性,但对SEU 和SEFI 十分敏感:SEU 的LET 阈值最低为1.0 MeV·cm/mg,最大饱和截面达到0.376 cm/device,SEFI 饱和截面为1.24×10cm/device。

随着SRAM 型FPGA 内部资源规模不断增大,功能模块增多,其单粒子效应特征及测试方法也会更为复杂,特别是单粒子功能中断效应,有待进一步研究提高SRAM 型FPGA 的单粒子效应测试覆盖率,以全面测试表征器件的SEE 特性。