基于eMMC阵列的高速大容量数据的存储设计

叶聪相,章增优

(浙江工贸职业技术学院 人工智能学院,浙江 温州 325000)

0 引言

随着信息时代的蓬勃发展,各行业对信息数据的需求更加迫切。产品研制阶段需要大量的数据支撑,通过分析数据能够实现对产品性能的不断优化,因此大容量数据的存储技术持续受到各行各业的关注。首先,传统的存储芯片Flash随着芯片制造工艺的不断改进,不同厂商生产的芯片也存在差异[1],因此虽然Flash存储空间越来越大,但其可移植性降低,进一步影响软件的开发周期[2]。其次,在对FLASH芯片进行读写控制时过程较复杂,产品异常断电时Flash芯片内部指针可能会随意跳转,导致数据读写错误[3],且数据通过FLASH芯片接口传输时速率低[4]。针对以上问题,提出采用eMMC存储芯片来对数据进行存储。eMMC芯片与其他存储芯片最大的不同是其内部包含了FLASH芯片以及FLASH芯片控制模块[5],解决了不同型号存储芯片兼容性的问题,极大地提高了软件的可移植性,节省了产品开发周期。该存储芯片存储容量大,接口传输速率高,可实现数据的高速传输[6]。因此,这种嵌入式芯片获得了越来越多的青睐。

由于FPGA具有强大的并行处理数据的能力,且内部集成了很多硬核,对其进行编程时可直接调用,缩短了软件开发时间[7],系统选用FPGA作为控制芯片,利用其内部集成的IP核实现对外部数据的高速收发,然后对数据进行暂存及数据组帧处理,使用MMC接口实现对对8片eMMC芯片的读写操作,完成高速大容量数据的存储。本设计对于产品进行后续测试提供了保障。

1 系统总体设计

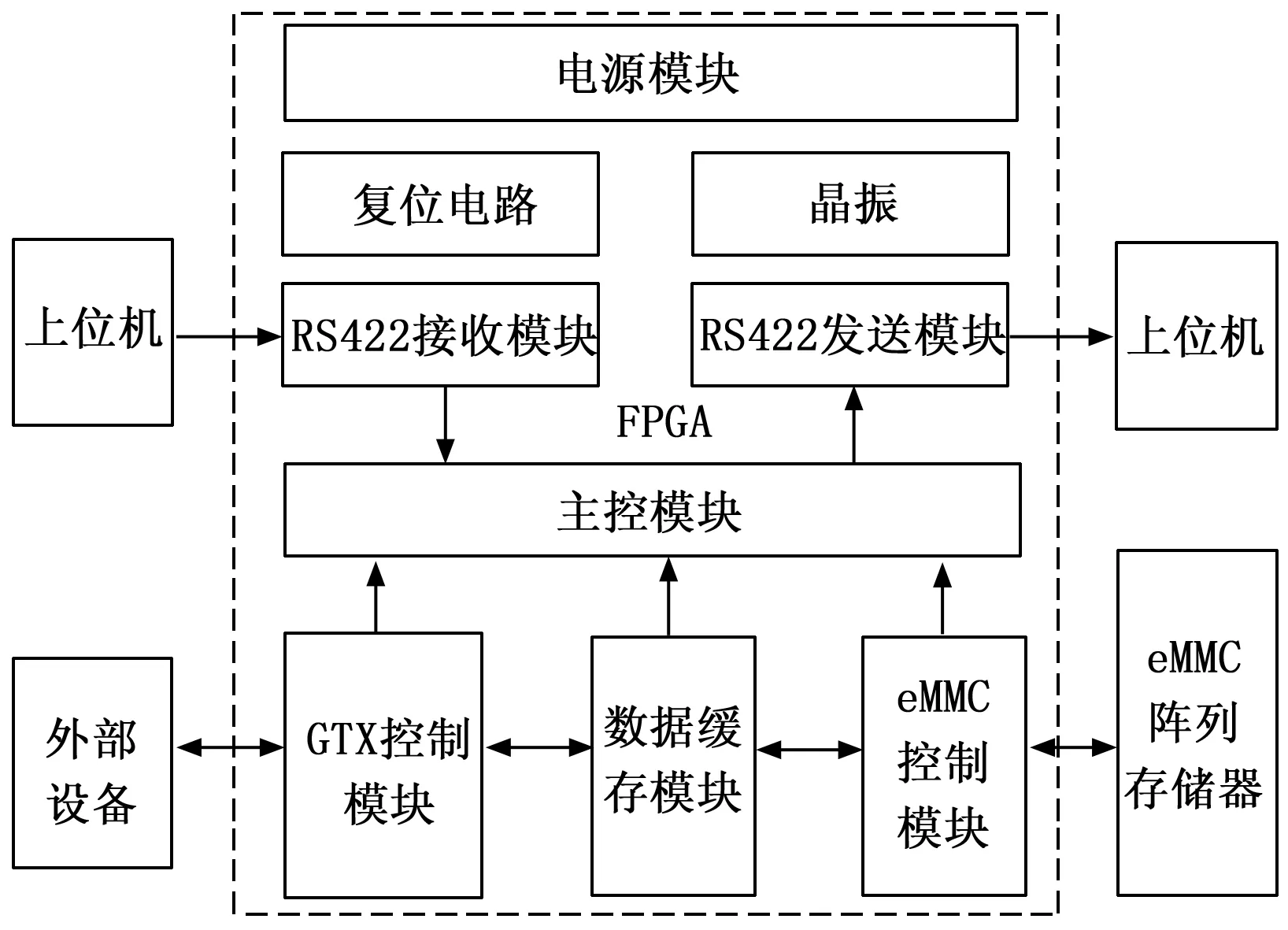

设计主要由RS422收发模块、主控模块、eMMC存储控制模块、数据缓存模块、GTX控制模块及电源模块等模块组成。系统总体设计如图1所示。

图1 系统总体设计框图

系统上电复位完成后,eMMC控制模块以及GTX控制器模块自动进入初始化流程。FPGA通过RS422接口接收到上位机发送的启动采数命令时,首先对eMMC控制模块以及GTX控制模块的状态进行判断,若其初始化未完成,则将回应帧中的Busy标志位置‘1’;若初始化流程结束,则Busy标志位清‘0’,并准备数据的采集。GTX控制模块启动对外部串行数据的高速采集,为匹配数据传输速率,使用数据缓存模块对高速收发控制器模块输出的数据进行暂存,FPGA主控模块根据缓存模块输出的空满标志,一方面控制eMMC存储控制模块对eMMC芯片进行读、写、擦除等工作;另一方面对GTX控制模块的收发也进行控制。eMMC控制模块对数据按照传输协议组帧后,通过MMC接口将数据存储至外部eMMC芯片中。回读是数据写入的逆过程。经系统实测,eMMC接口传输速率为2.4 Gbps,实现了设计需求。

2 系统硬件设计

2.1 GTX收发模块设计

设计选用Virtex-6系列的FPGA作为逻辑控制器,采用其内部集成的IP硬核GTX实现对大容量数据的高速传输[8]。GTX内部由两部分构成,分别为接收模块和发送模块[9]。其中,接收模块主要实现的功能依次对输入信号进行整形滤波,从输入串行数据流中将时钟与数据恢复出来,串并转换,数据字符对齐,解码,时钟纠正,位宽转换输出[10]。发送模块实现数据发送的步骤大致与接收相反,依次为位宽转换输入,编码,并串转换,信号预加重,信号转差分输出[11]。发送模块与接收模块传输时互不影响,GTX模块通过SMA接口与用户设备进行连接,信号输入为差分方式,使得数据传输更稳定[12]。GTX控制模块在进行数据传输时,其接口的传输速率理论值为6.6 Gbps[13],完全符合设计对数据传输速率的要求。GTX控制模块接口原理如图2所示。

图2 GTX接口原理图

2.2 eMMC阵列模块设计

设计采用美国美光公司的eMMC芯片(MTFC64GJVDN-4MIT)进行大容量数据的存储[14]。通过该芯片进行数据的传输时,其接口的传输速率为3.2 Gbps,能够实现数据的高速收发[15]。由于eMMC芯片集成了Flash芯片及Flash控制器,FPGA只需通过简单的接口就可对其进行操作[16]。FPGA与eMMC芯片通讯的接口原理如图3所示,设计采用6片eMMC芯片进行数据存储,每片可以存储的空间大小为64 GB[17]。FPGA与eMMC阵列之间主要通过时钟线、数据线、命令线、电源线以及地线进行通讯。其中,时钟线、电源线以及地线是共用线,数据线和命令线则各自独立[18]。硬件在设计时,为降低干扰,在电源接口处引入滤波网络,从而保证电源的可靠性[19]。同时硬件上将数据线及命令线均进行上拉,提高了芯片管脚的驱动力[20]。

图3 eMMC阵列接口原理图

3 系统软件设计

系统采用Verilog语言在ISE14.6开发环境下实现软件代码的编写,软件整体架构如图4所示。系统上电后,上位机通过RS422接口发送命令给FPGA,待FPGA各模块初始化完成后,启动对外部数据的接收存储。首先外部设备的数据经过GTX模块快速接收后,设计为匹配数据传输速率,保证数据传输无误,将数据进行缓存后再发送至eMMC控制模块。eMMC控制模块根据上位机命令对eMMC芯片进行相应的操作,通过命令接口、数据接口实现对eMMC芯片的初始化、写入、读出等功能。

图4 系统软件总体架构图

3.1 eMMC协议帧格式

3.1.1 数据帧格式

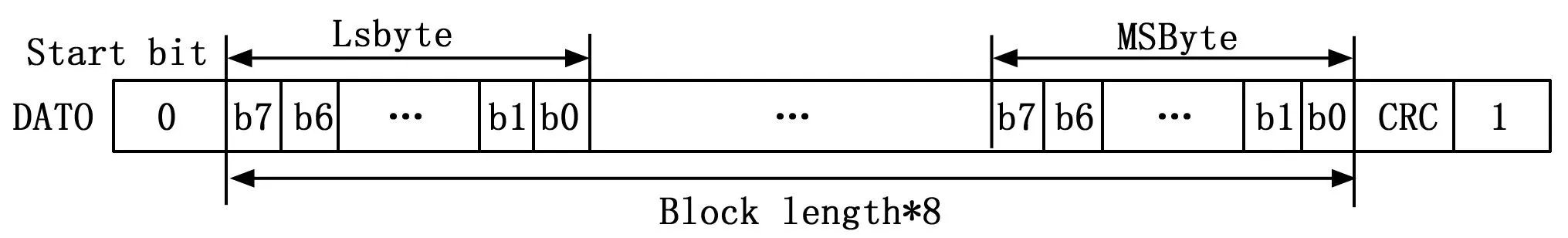

FPGA作为主机,控制数据总线与eMMC芯片进行数据交互。在对eMMC芯片写入数据时,需要按照正确的传输格式对数据进行重新组帧才可以实现数据的正常发送[21]。其协议帧格式如图5所示,主要由4部分构成。其中,起始位为固定值‘0’,结束位为固定值‘1’,CRC为2选择字节,数据包长度不定。数据在SDR模式下传输时,可以选择1 bit、4 bit或者8 bit的传输位宽,且数据均在时钟上升沿进行采样。

图5 eMMC协议数据帧格式

3.1.2 命令帧格式

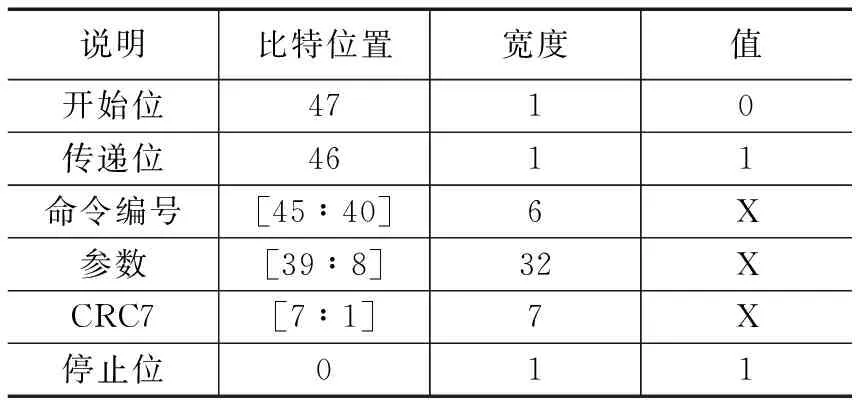

FPGA作为主机,控制命令总线与eMMC芯片进行命令交互。为确保命令发送有效,当eMMC芯片接收到命令时,会发送命令响应至FPGA。FPGA通过发送不同的命令实现对芯片的操作,但这些命令都具有相同的帧格式,如表1所示。命令帧长度固定,均为6个字节。

表1 eMMC命令帧格式

主机发送不同的命令,接收到的响应长度各不相同。且命令发出后,将在各自要求的时间后收到响应信息。如图6所示,当主机发送命令给单片eMMC芯片设置初始地址时,等待NCR个周期后,得到eMMC芯片发送的响应信息。

图6 eMMC协议命令和响应时序图

3.2 eMMC初始化模块设计

系统上电后,通过发送命令实现对eMMC芯片内的寄存器进行配置,从而完成eMMC芯片的初始化工作。首先,根据eMMC芯片特性,芯片上电复位完成后,配置200 Hz的时钟作为eMMC芯片的初始化主频。然后,发送CMD1命令完成对工作条件寄存器的配置,实现eMMC工作电压的检验与匹配。发送CMD2命令可获取产品出场信息等。由于设计选用6片eMMC芯片用于大容量数据的存储,因此当FPGA对其进行访问时,需要唯一的芯片地址与之对应,因此在配置芯片时,可以通过写入CMD3命令对其内部相对地址寄存器进行每片芯片地址的配置,使得数据在传输时具有一对一的效果。根据eMMC传输帧格式,一帧数据中除去开始位、结束位以及校验位以外,数据字节长度不定。通过发送命令CMD9,可以查询到eMMC芯片在数据传输过程中支持的数据字节长度等信息。然后发送CMD7命令选定eMMC芯片参与初始化流程结束后的数据读写工作。最后发送CMD6命令将输入时钟切换至5 MHz,并重复发送该命令确认数据传输位宽及采样时刻,初始化流程结束。eMMC控制模块初始化流程如图7所示。

图7 eMMC控制模块初始化流程图

3.3 eMMC写模块设计

将大容量数据写入eMMC存储芯片时,首先由FPGA通过命令线串行输出48 bit的CMD7至eMMC存储器,用于指定6片eMMC存储器之一作为从机。然后发送命令CMD16配置有效的数据包长度。完成以上命令的发送后,FPFA发送写指令CMD24至eMMC芯片,并且在FPGA收到正确的命令响应之后开启数据的传输。eMMC芯片开始接收时,首先将数据接收到内部缓存器中,同时对接收到的每1 bit数据进行校验,当接收完一帧数据时,会将CRC正确与否的标志通过数据线0发送至FPGA,该标志包括3位,若该标志为2时表示数据写入正确,此时缓存器中的数据才会编程至内部Flash;若该标志位5时,表示数据写入过程中出错,该数据将丢弃。数据在写入Flash的过程中,不允许其他写入操作,因此通过拉低数据线0表示数据正在写入。eMMC写时序如图8所示。

图8 eMMC写时序图

3.4 eMMC读模块设计

对eMMC模块的读操作与写操作大致相同。发送读命令之前均先发送CMD7、CMD16,分别完成芯片的选择及数据包长度的配置工作。通过输入读命令CMD17,根据该命令中的参数选择指定地址的芯片进行数据的读取。等待命令线收到来自eMMC存储器的响应后,开启数据的回读操作。eMMC模块读流程如图9所示。

图9 eMMC模块读流程图

4 系统测试与验证

4.1 数据及命令的CRC仿真

FPGA与eMMC进行数据或命令的交互时,需要对数据及命令分别按照不同的传输格式进行组帧,并计算CRC。对数据进行组帧的功能由eMMC控制模块中的子模块数据处理模块完成。为检验数据处理模块逻辑设计的严密性,编写仿真文件对模块内相关信号进行观察。由于数据及命令在组帧过程中遵循不同的帧格式,其CRC计算方法也不一致。命令帧的7位CRC按照CRC7校验方法计算,仿真图如图10所示。输入复位命令0x400000000095的高40位进行校验计算,得到校验结果为16’ h4 a,即十进制数95。与输入数据组帧后即为复位指令,因此可验证该模块对于命令帧CRC的计算仿真正确。

图10 命令帧CRC计算仿真图

数据帧的16位CRC按照CRC16校验方法计算,仿真图如图11所示。由于系统采用的是8 bit位宽进行数据的传输,过程中每一条数据线都会针对本条数据线上的串行数据进行CRC计算。为方便观察验证,发送数据从0开始递增。从图中可以看出,计算得到的首个CRC为0x1021,设计正确。

图11 命令帧CRC计算仿真图

4.2 GTX控制模块数据收发验证

采用在线逻辑分析仪Chipscope对GTX控制模块进行仿真。为使得验证结果更加直观,对GTX模块进行闭环验证,即收发模块进行连接,输入16 bit的递增数据,对数据收发同时进行测量并绘制折线图,如图12所示。从图中可以看出,数据收发一致。该模块可以实现数据的高速传输功能。

图12 GTX模块收发数据曲线图

4.3 eMMC模块初始化验证

eMMC模块的初始化是对eMMC模块进行其他操作的前提。为验证eMMC控制模块是否能正确实现对eMMC芯片的初始化操作,采用Chipscope对该模块的相关信号进行在线监测。首先按照初始化流程,输入相应的指令,完成对eMMC芯片内部相关寄存器的配置。然后通过命令线观察回应,判断初始化完成状态。如图13所示,从图中可以看出,当主机发送完时钟切换指令0x4603b901002f后,命令线上的回应为0x0600000800cb,表明eMMC芯片初始化已完成。

图13 eMMC模块初始化验证图

4.4 eMMC模块数据写验证

为加快数据的写速率,简化写入步骤。在FPGA对eMMC芯片进行写操作时,采用多块写的方式进行。数据传输前,设置好写入数据的块数据写入后,将自行完成块数的递增,并完成数据的写入。发送完预设的数据字节长度后,不断查询数据线0上的校验标志,来确认数据写入的正确性。如图14所示,经系统验证,数据线0返回的3bit CRC标志为0x010,表示多块写成功。

图14 eMMC模块多块写验证图

4.5 eMMC模块数据读验证

eMMC模块数据读操作同样采取预先设置指定读块数,然后发送读命令后,自动读取相应eMMC地址的数据。通过对比块数预设值和读取值,来判定读流程是否结束。经系统验证,预设读取6块数据帧,同时对读取的数据帧进行计数,结果数值一致,验证正确。完成的方式。eMMC模块的数据读过程如图15所示。

图15 eMMC模块多块读验证图

4.6 系统验证验证

对系统各模块功能进行验证后,需针对全局时序进行仿真验证。FPGA主控模块识别上位机输入的写命令,控制GTX模块启动对外部数据的接收,然后经过eMMC控制模块对数据重新组帧处理后,将其串行输入至eMMC阵列中。对该过程采用Chipscope进行在线监测,如图16所示。根据数据的采样点,计算其传输速度为2.4 Gbps,从而验证了本设计可以实现数据的高速存储。

图16 系统写验证图

上位机输入读命令后,启动对eMMC阵列的数据读取。然后将读取的数据进行相应的处理后,发送给GTX控制模块发送至外部设备。对该过程采用Chipscope进行在线监测,如图17所示。根据数据采样点,计算其传输速度为3.0 Gbps,实现了数据的高速读取。

图17 系统读验证图

测试设备采用对比工具,将回读的数据与发送的数据进行比较后,确认数据的一致性。验证了数据传输存储的正确性和可靠性。

5 结束语

系统为实现对某飞行仿真数据的快速存储,设计了基于eMMC阵列的高速大容量数据的存储设计。采用GTX控制模块与eMMC控制模块相协作,实现了对大容量数据的高速存储,数据存储速率为2.4 Gbps。通过对数据回读验证,系统传输存储设计稳定可靠,数据未出现错帧丢帧的现象。系统采用eMMC阵列进行数据的存储,简化了FPGA对存储器的读写控制,缩短了研发周期,节约了成本,为大容量数据的测试提供了良好的保障。