一种基于UVM的高层次化1394链路层验证方法

魏美荣,田 泽,王宣明,郭 蒙

(1.航空工业西安航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点实验室,陕西 西安 710068;3.西安翔腾微电子科技有限公司,陕西 西安 710068)

0 引 言

1394总线是一种高性能串行总线,链路层在串行总线节点系统中位于事务层、应用层和物理层之间。链路层为事务层提供异步数据的接收、发送和确认服务,为应用层提供固定时间间隔的等时数据广播传输服务。同时链路层提供寻址、数据检查、发送数据组包和接收数据解包服务。

随着集成电路技术的不断发展,芯片的规模和集成度在快速提升,这对验证提出了更高的要求。据统计表明,发现bug的时间与修复成本成指数关系,越早发现弥补的成本也会越低,因此,验证已经成为芯片设计的发展瓶颈。针对传统RTL代码验证平台重用性差、覆盖率低和自动化程度低等问题,在吸取了OVM,VMM和ERM等验证方法优点的基础上,三大EDA公司(Mentor、Candence和Synopsys)联合业内其他公司推出UVM(universal verification methodology)验证方法学。UVM是基于系统级硬件描述语言SystemVerilog,具备面向对象编程的思想和功能[1-3],实现了验证的重用性和清晰的层次结构。由于其开源的特质,使得它相比于其他的验证方法学,具备更好的兼容性。UVM平台的架构主要是由通用的验证组件(universal verification component,UVC)构成的,而且每个UVC都是已经封装好、功能完善且可配置的验证环境,可重用的验证组件,约束随机激励产生、自动化的验证平台等特点,大大缩短了验证时间[4-6]。

另外,相比于传统的验证平台,断言机制提供了简洁的行为级代码描述,能对设计的属性进行实时性的检测,仿真过程一旦报错可迅速定位[7]。功能覆盖率是用来衡量哪些设计特征已被测试程序测试过的一个指标,评估验证的结果[8]。覆盖率有三类:代码覆盖率、功能覆盖率和断言覆盖率。使用UVM提供的随机测试激励以及带约束的随机测试(constrained random test,CRT)方法可以覆盖各种情况[9-10],不用编写定向的测试集,就可以达到尽可能高的覆盖率。若还有未能覆盖的边界情况,可采用定向的测试激励来进行测试[11]。

文中以1394链路层作为主要分析对象,重点从基于覆盖率驱动的自动化验证环境搭建、验证流程、验证平台、随机验证激励用例开发、覆盖率统计结果分析等方面重点阐述。并经过功能仿真测试和覆盖率分析表明,采用基于UVM的验证分层结构,实现的事务层请求模型、数据包模型、链路层监控模型,物理层模型等激励序列具有继承性和灵活的随机约束性,可使验证人员花费较少的精力实现重用原有的激励场景而构成新的激励场景。基于断言和覆盖率驱动的验证理念,以可约束的随机向量为主,对仿真结果进行覆盖率统计和分析,并对随机向量的约束进行修改或补充定向向量,保证验证的完备性。

1 虚拟验证策划

在前端设计中,文中先对1394总线链路层系统功能进行分析,根据设计功能提取链路层验证功能点,然后制定了相应的验证策略与方法,并详细描述了该方法中的验证环境、验证流程、虚拟验证平台各组件功能以及工作原理。

1.1 系统功能分析

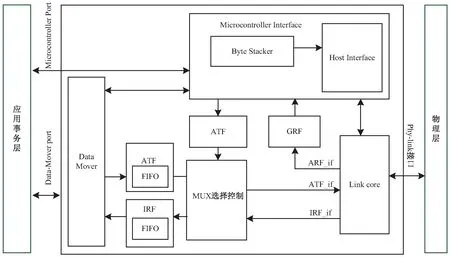

1394总线链路层是1394高性能串行总线的重要部分,实现了IEEE Std 1394-2008协议规定的1394b高性能串行总线的节点链路层功能,其逻辑结构框图如图1所示。主要包含数据搬运(data mover)模块、选择控制模块、异步发送FIFO模块(asynchronous transmit FIFO,ATF)、通用接收FIFO(general receive FIFO,GRF)、微处理器接口(microcontroller interface)模块、链路层核(link core)等功能模块,实现的主要功能包括:

图1 1394总线链路层结构框图

(a)负责在事务层和物理层之间传递异步、异步流和等时数据;

(b)提供标准的Alpha类型物理层-链路层接口,用于连接物理层;

(c)提供数据搬运接口(data mover),支持异步流数据的收发,可通过寄存器访问接口进行异步发送物理配置包和异步包,通过访问GRF接收异步包和自标识包;

(d)当进行异步消息收发时,链路层将数据从事物层传递给物理层,或将物理层接收到的数据传递给事物层,并负责添加数据CRC校验;

(e)在等时通讯过程中,负责周期发送、接收cycle start包,用于同步总线各节点的等时周期,并保证等时消息通讯能够正常进行。

1.2 验证方法

文中采用UVM验证系统架构、基于功能覆盖率驱动的验证方法,从链路层系统级功能分析角度出发,制定出一套通用性强的1394总线链路层验证实施方案。

1.2.1 验证流程

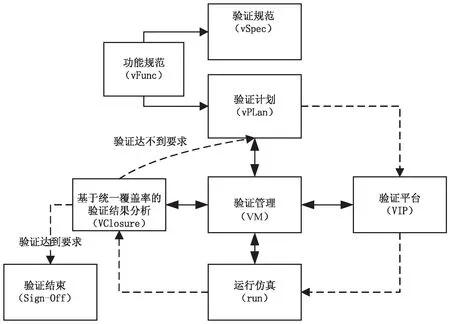

文中将结合最新UVM验证技术、统一覆盖率的验证管理技术,采用新型闭环的验证流程[12],如图2所示。

图2 验证流程

实现对1394总线链路层功能验证,具体过程如下:

(a)首先,根据1394总线链路层功能规范编写验证规范和验证计划,即列出需要验证的关键功能特性、边界情况和可能出现的故障模式。建立覆盖率模型时,先根据上述的验证规范,明确待验证的功能点以及如何对这些数据采样,然后构建能够自动统计功能覆盖率的验证平台,定义覆盖组(Covergroup)来统计和分析功能覆盖率,确保每个设计需求都被实现、验证且功能正确。下面以1394总线链路层寄存器访问为例,设计的一个寄存器对象的功能覆盖组代码示例如下:

class host_coverage_monitor extends uvm_subscriber #(host_trans_item);

`uvm_component_utils(host_coverage_monitor)

host_trans_item analysis_txn;

covergroup host_cov;

option.per_instance =1;

ADDR: coverpoint analysis_txn.addr[5:1]{

bins VERSION_U ={6'h00};

bins VERSION_L ={6'h01};

………

}

OPCODE: coverpoint analysis_txn.wr {

bins write = {0};

bins read = {1};

}

RW_CROSS: cross ADDR,OPCODE;

endgroup

// Standard UVM Methods:

function new(string name = "host_coverage_monitor", uvm_component parent = null);

super.new(name, parent);

host_cov = new();

endfunction

extern function void write(T t);

extern function void report_phase(uvm_phase phase);

endclass: host_coverage_monitor

(b)其次,基于UVM方法学搭建验证环境、开发验证代码、验证管理功能,通过输入测试计划,即“产生的激励”输入到DUT(design under test)设计中,并且通过UVM内部自带的函数run_test()开启UVM运行仿真,并将产生结果输出,引入功能覆盖率模型,对覆盖率的结果进行分析,即将测试覆盖率与测试对象联系起来,从而为管理人员与工程师提供强大支持,使得持续不断地跟踪验证进度和更为合理高效地配置资源成为可能。

(c)最后,经过回归测试、验证结果和覆盖率分析,如果验证达不到要求,则需要反复迭代优化验证方案,完善或更改验证计划,通过UVM机制管理验证平台、再运行、再进行结果分析等,直到完成验证激励的开发调试,最终极大程度地实现1394总线链路层芯片验证工作的收敛。

1.2.2 验证平台构建

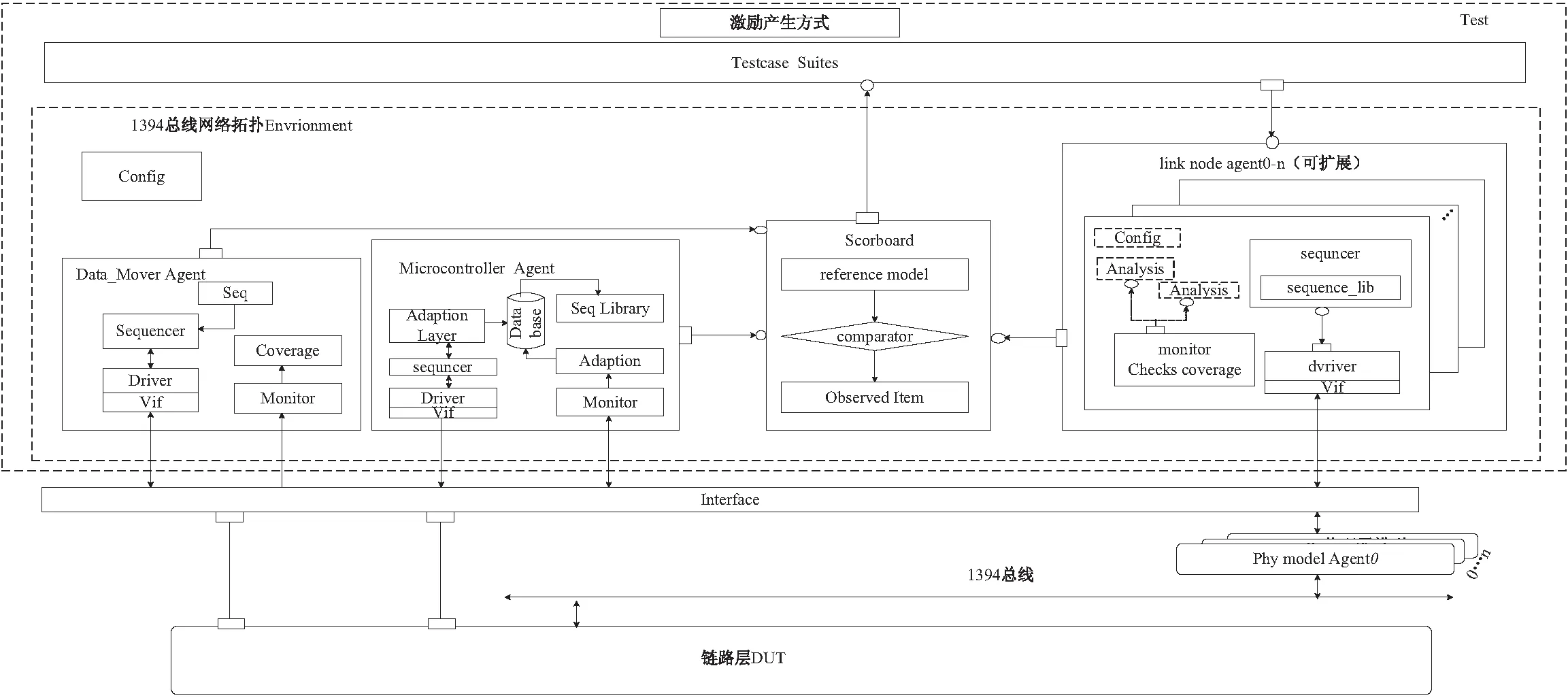

文中对不同的功能组件进行单独设计,同时以UVM方法学为基础,设计了如图3所示的高层次化验证平台结构。采用基于Systemverilog面向对象编程的方法编码实现,每一个组件用一个类(class)单独实现,类中定义属性(数据)和属性操作方法(包括任务和函数)[13-15]。此验证平台的结构可以分为三个部分:首先实例化链路层DUT,是用于平台中与其他组件进行通信的接口;然后创建DUT外围的验证组件UVC,是一种可以重用的对应于链路层外围接口协议的IP模型,与顶层DUT之间具备通信接口,分别是微控制器寄存器访问(Microcontroller Agent)、事务层数据搬运接口(Data_Mover Agent)、1394总线物理层模型(Phy model agent)、1394总线多节点的链路层模型(link node agent);最后是基于UVM开发的测试激励Test Suites、测试脚本等。

图3 基于UVM的1394总线链路层虚拟平台验证架构

文中搭建的验证平台是一个1394总线多节点拓扑结构,链路层DUT也是作为其中一个被测试节点,其中,Test Suites是由UVM的Sequence机制实现的一系列随机测试激励。各模块Agent内部Sequencer是激励产生器,产生协议规定的寄存器访问类型、不同类型包数据格式,Sequence通过Sequencer将Seq_item送到驱动器Driver,Driver通过虚接口virtual interface(vif)将事务级的数据按照信号层接口的时序要求转换为DUT端的电信号,并驱动DUT来发送接收数据包。平台中的Configuration模块用于系统的配置,根据不同的配置,使驱动芯片外部管脚不同时序下激励输出和错误注入。各Agent内部的Monitor进行数据采集监控,最后将放到Coverage和记分板Scoreboard中,通过记分板Scoreboard与行为级模型进行数据结果比较,通过UVM_report功能完成结果输出。

在上述验证平台中各功能模型Agent的主要功能如下:

(a)Microcontroller Agent,模拟1394链路层主机访问寄存器读写,和通过填写内部包头、包中和包尾寄存器来实现TAF中异步包、异步流包、物理配置包的发送以及通过GRF接收异步包、自标识包等数据包的接收;

(b)Data_Mover Agent,模拟事务层进行异步或等时通信模式下,数据包的发送与接收;

(c)Phy model Agent,和link node agent连接,模拟1394总线上的拓扑结构,并且提供1394总线物理层的协议规定的数据处理行为;

(d)link node agent,模拟1394总线协议规定的链路层协议处理行为;

(e)Test Suites,用于验证的测试用例,是由UVM的sequence机制实现的一系列随机测试激励。测试用例均由uvm_test类派生而来,每个测试激励都设置了默认启动的测试激励,只需在命令行启用这些测试用例。文中设计有3种类测试用例,分别是基本测试、随机测试、注错测试。其中,随机激励测试可以找出预料不到的错误,通过SystemVerilog语言对激励进行随机化和约束。基本测试用例是根据需要产生特定要求的激励,关注设计功能点本身。注错测试用例通过带约束的随机激励产生各种错误激励,用于测试某些极限情况下可能出现的故障问题,检测设计本身的处理错误能力;

(f)达到覆盖各种情况,达到尽可能高的覆盖率,从而完成验证目标。

上述各Agent模块均具有独立结构,根据实际项目中1394总线节点通信个数,只需要通过实例化多个Phy model Agent、link node agent来实现可重用,达到快速构建验证平台,便可以加快验证流程。

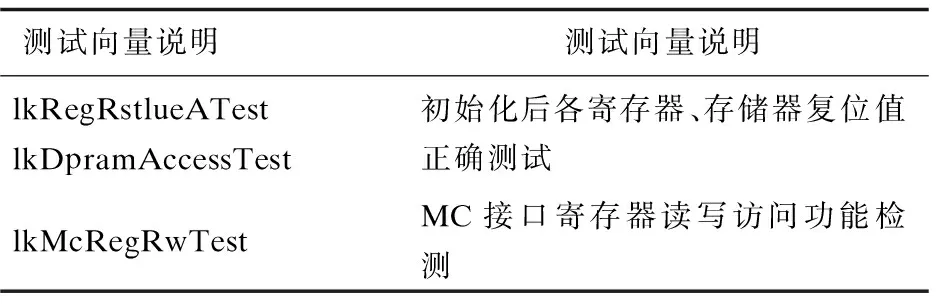

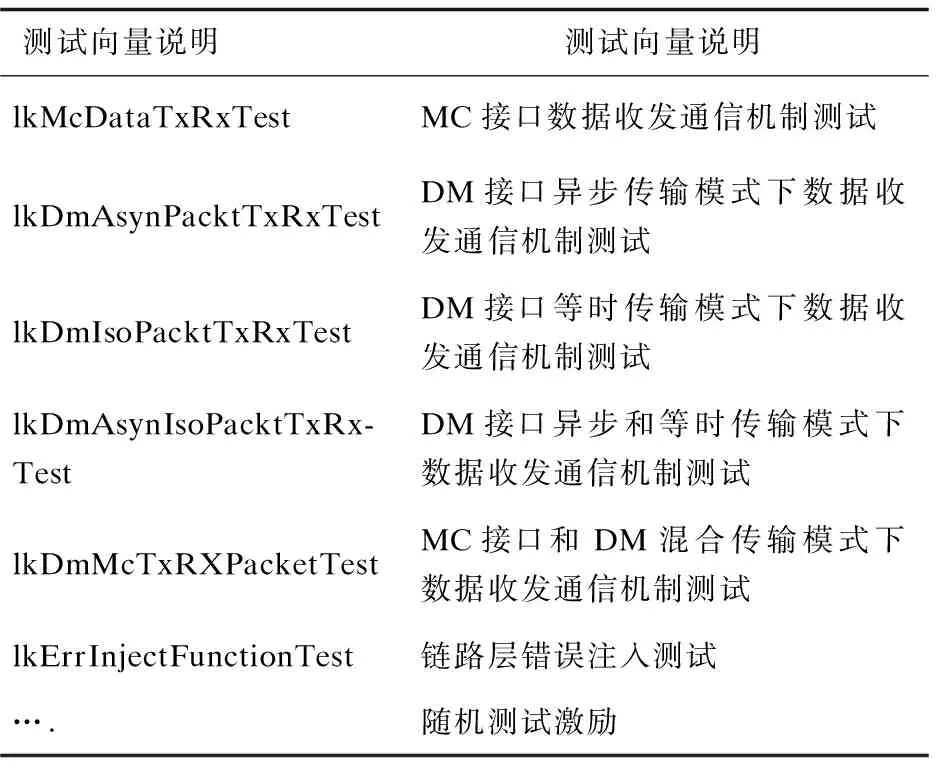

文中根据制定1394总线链路层主要功能建立的测试用例如表1所示。

表1 测试向量

续表1

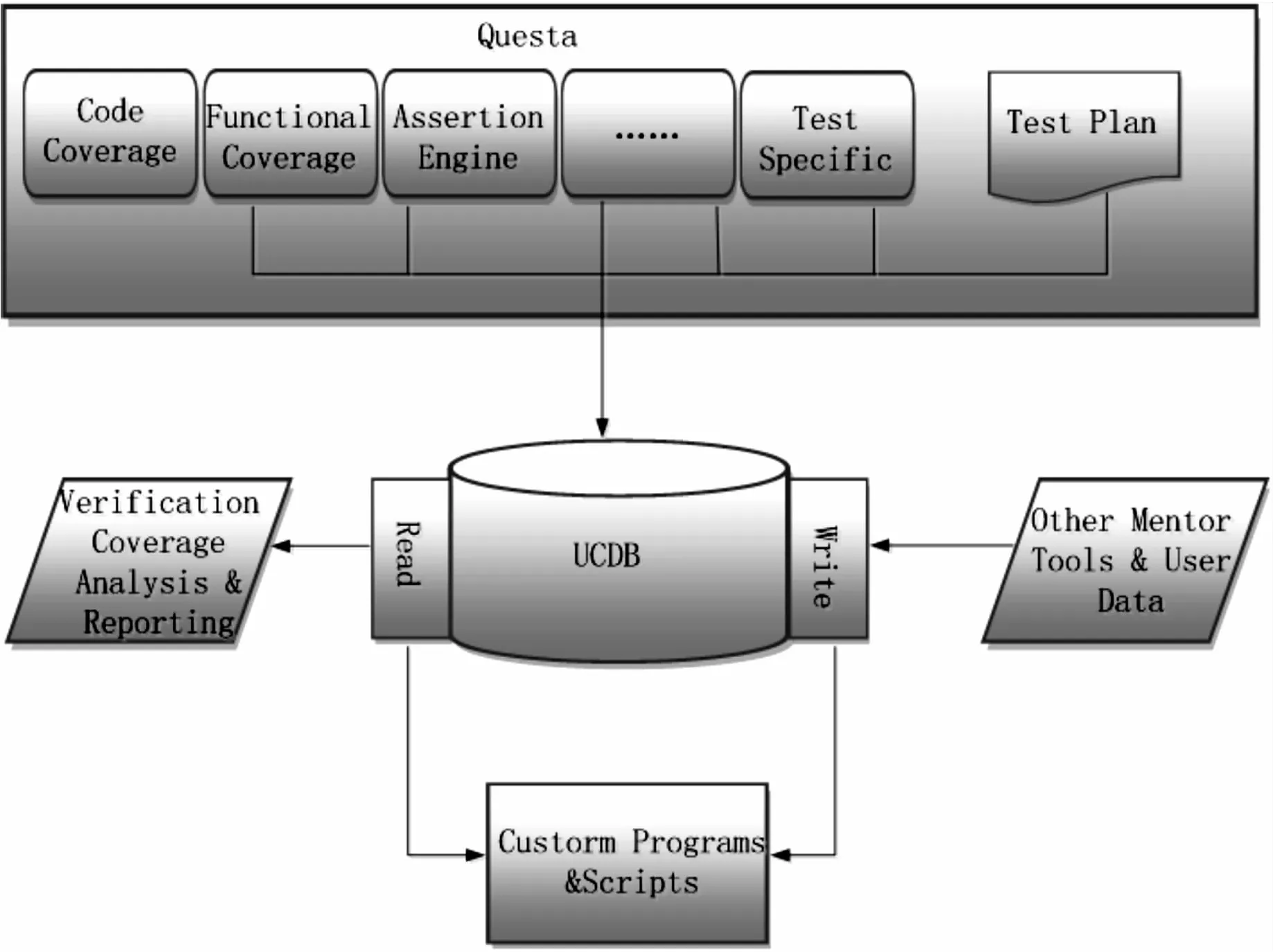

1.2.3 验证环境

文中采用Metor Graphics公司提供的Questa作为功能仿真平台,如图4所示。利用其内嵌断言引擎、高性能约束求解,以及统一覆盖率数据库(UCDB)。断言是对设计属性的描述,采用断言技术快速检测到设计中潜藏的缺陷,如被检测对象与预期检测行为不一致,则上报断言错误,并直接追溯源代码中最原始的信号。通过UCDB管理并收集所有的覆盖率数据:代码覆盖率、功能覆盖率和断言覆盖率,并存储在统一个数据库中。验证管理功能通过输入测试计划、并将测试覆盖率与测试对象联系起来,利用Questa提供的强大分析能力,将原始覆盖率数据转变为可操作易识别的信息。

图4 功能仿真平台

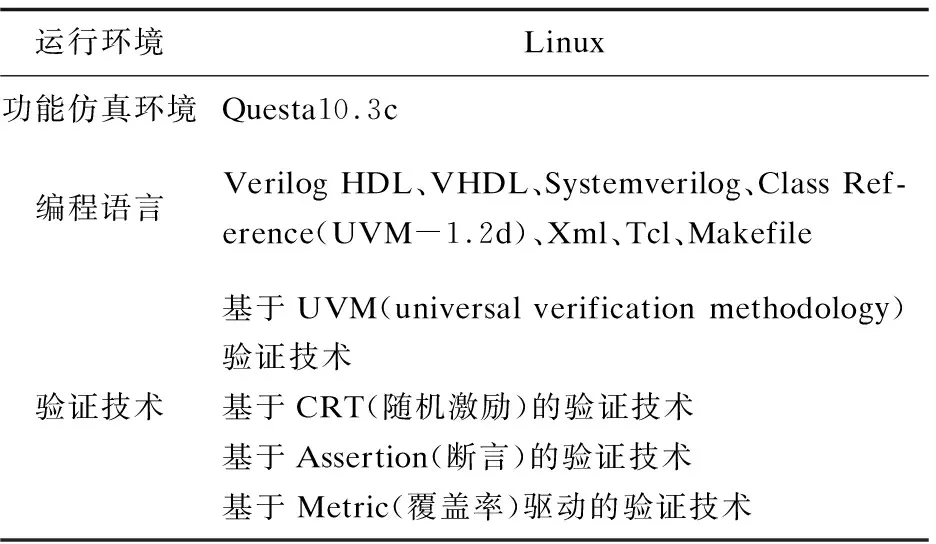

在Linux运行环境QuestaSim功能仿真平台,如表2所示,采用SystemVerilog、Makefile编程语言及脚本语言,将编译、仿真、测试选择、覆盖率收集等功能设计为自动化流程。不同的测试模式下,切换外部测试模型的应用场景,把外部的测试激励输入给1394总线链路层被测设计。

表2 1394链路层验证环境

1.2.4 运行流程

基于UVM验证方法学,验证组件之间按照UVM的phase机制运行,即仿真器首先从平台顶层TOP执行,遇到特定函数run_test()后验证平台开始启动,脚本运行时利用UVM_TESTCASE从命令行中寻找testcase名字并创建该测试case实例,以树形结构方式依次执行case及其成员变量的build_phase,顺序执行UVM树各个节点build_phase、connect_phase以及run_phase各阶段,直到所有的phase执行结束。

2 验证与分析

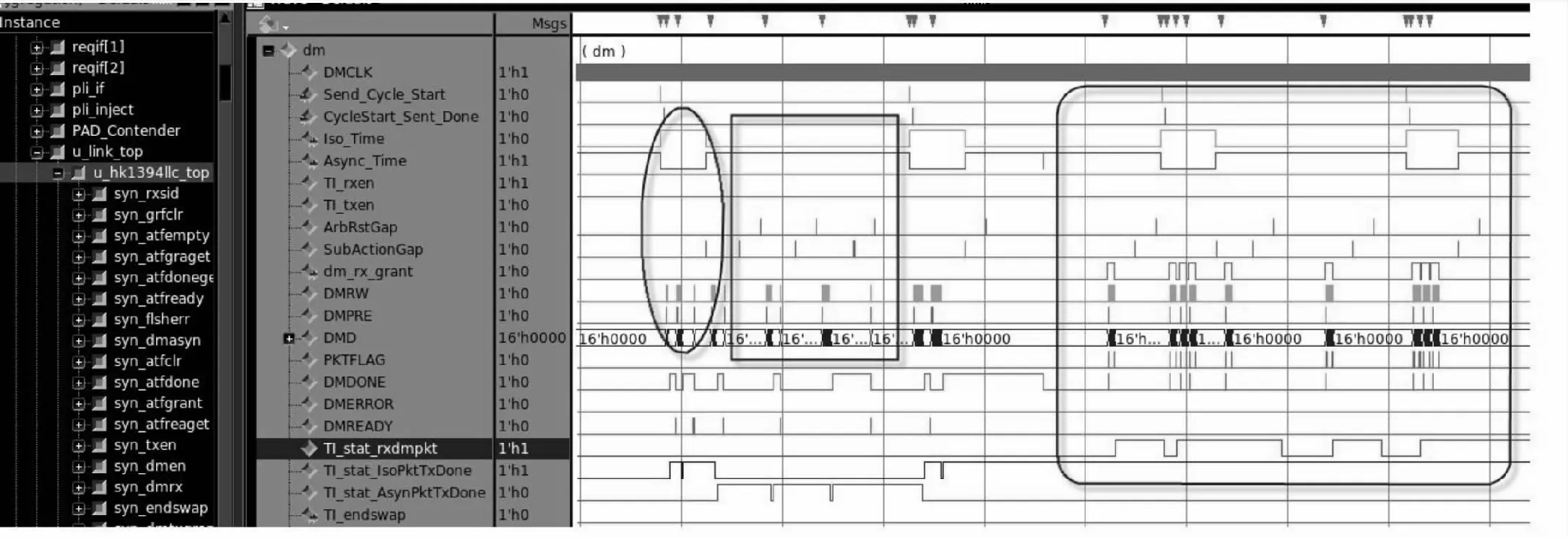

使用上述描述的验证平台对链路层DUT进行功能验证,以事务层数据搬运Data Mover接口的等时和异步模式通信仿真为例,采用上述规划的测试激励,运行UVM仿真平台得到仿真结果波形,如图5所示。图中椭圆框出的部分为等时数据包的发送,长方形框出的部分为异步流数据包发送,圆角矩形框部分是等时数据包和异步流数据包的接收,可见该测试平台能够很好地模拟1394总线实际通信场景。仿真进行到Check_phase阶段通过检查Scoreboard的对比结果以及其他组件的结果是否出现违例,确认没有遗留的数据要处理,到Report_phase阶段产生报告仿真结果,或者生成的log文件中的报告及断言来检测DUT的正确性[16-17]。同时,通过分析覆盖率报告,不断完善测试激励,添加新的测试激励,实现全面的功能验证,将所有测试向量测试完毕后,进行回归测试并进行覆盖率统计,将输出结果进行打印。如图6所示,覆盖率已达到100%,满足链路层系统功能验证的要求,证明了该验证平台测试激励的完整性,达到了预期验证目标。

图5 DM接口等时和异步流数据包收发通信仿真波形

3 结束语

文中针对1394总线链路层系统功能需求分析,制定了一套适用于链路层验证的方法,构建了能够自动统计功能覆盖率的验证平台,基于高级验证方法学UVM的UVC实现了1394总线协议。采用monitor监视收集数据,利用功能覆盖率统计各验证功能点,并能够在Scoreboard上比较输出结果。采用基于UVM的高层次的以覆盖率驱动的验证方法,实现了链路层功能验证的100%的功能覆盖率。能有效模拟链路层行为,极大地提高验证效率,缩短验证周期。