一种低温漂高电源电压抑制比带隙基准电压源设计

谢海情 王振宇 曾健平 陆俊霖 曹武 陈振华 崔凯月

摘 要:通过将具有高阶温度项的MOS管亚阈值区漏电流转换为电压,并与一阶温度补偿电压进行加权叠加,实现二阶温度补偿. 采用高增益的运放和负反馈回路提高电源抑制能力,设计一种低温漂高电源电压抑制比带隙基准电压源. 基于0.18 μm CMOS工艺,完成电路设计与仿真、版图设计与后仿真. 结果表明,在1.8 V的电源电压下,电路输出电压为1.22 V;在温度变化为-40~110 ℃时,温度系数为3.3 ppm/℃;低频电源电压抑制比为-96 dB@100 Hz;静态电流仅为33 μA.

关键词:带隙基准;温度系数;电源电压抑制比;温度补偿

中图分类号:TN402 文献标志码:A

Design of Bandgap Voltage Reference

with Low Temperature Drift and High PSRR

XIE Haiqing1,2,WANG Zhenyu1,2,ZENG Jianping3,LU Junlin1,2,CAO Wu1,2,

CHEN Zhenhua1,2,CUI Kaiyue1,2

(1. School of Physics and Electronics Science,Changsha University of Science and Technology,Changsha 410114,China;

2. Hunan Provincial Key Laboratory of Flexible Electronic Materials Genome Engineering,

Changsha University of Science and Technology,Changsha 410114,China;

3. School of Physics and Electronics,Hunan University,Changsha 410082,China)

Abstract:The second-order temperature compensation was realized by weighted superposition of the first-order temperature compensation voltage and the voltage with high-order temperature term which was conversed from the subthreshold leakage current of MOS transistor. In addition,a high-gain operational amplifier and negative feedback loop were adopted to improve the power supply rejection ratio(PSRR). Subsequently,a bandgap voltage reference with low temperature drift and high power supply voltage rejection ratio was proposed. Based on 0.18 μm CMOS technology,circuit design and simulation,layout design,and post-simulation were carried out. The results indicated that the output voltage was 1.22 V under the power supply voltage of 1.8 V;the temperature coefficient(TC) was 3.3 ppm/℃ in the temperature range from -40 ℃ to 110 ℃;the PSRR at low frequency was -96 dB@100 Hz;the static current was only 33 μA.

Key words:band gap;temperature coefficient;PSRR(power supply rejection ratio);temperature compensation

帶隙基准电压源作为集成电路的重要模块之一,能够有效抑制电压扰动与温度变化对输出的影响,产生精准的基准电压,从而被广泛应用于诸多领域[1]. 传统的带隙基准电压源是通过对三极管的发射结电压VBE进行一阶温度补偿,降低温度系数,从而减小温度变化对基准电压的影响[2-3]. 然而,由于高阶温度项的存在,一阶温度补偿的极限约为13 ppm/℃[4],无法满足高精度集成电路系统的要求. 为提高带隙基准电压源的性能,人们尝试了多种技术以降低基准源的温度系数. Andreou等[5]提出了一种新型的宽温度范围的基准电压源,利用多晶硅电阻和运放产生与绝对温度呈负相关性的电流进行曲率补偿,从而拓宽了温度范围,但容易受到工艺变化引起的不匹配的影响. Duan等[6]通过设计两个基准源模块和共源共栅电流镜结构,分别获得了曲率上升和曲率下降的基准电流,实现了精确的匹配,降低了温度系数,但其采用了多个运放,不仅使电路更为复杂,而且消耗更多的功耗. Ming等[7]利用多个低阻抗路径,将电源纹波在未抵达输出前旁路至地,并通过多个电流基准形成高阶曲率补偿,从而获得了高稳定性的基准电压,但其工作温度范围较为狭窄. 此外,Wang等[8]利用硅带隙变窄效应,将三极管的发射结电压随温度变化的曲率由3.6 mV降到1.4 mV,在不增加功耗的基础上,提高了带隙基准电压源的精度. 肖璟博等[9]利用双带隙结构,以电流比例相减的方式实现曲率补偿. 文献[4]提出了一种指数型曲率补偿技术,通过亚阈值区MOS管获得与绝对温度呈指数关系的补偿电流,取得了良好的效果. Chen等[10]提出了分段式电流补偿技术,将加法电路,减法电路和电流镜结合在一起,分别补偿不同温度范围内的曲率,在整个温度范围内实现良好的温度系数. 但这些技术在降低温度系数的同时,输出电压易受电源电压扰动影响,难以获得较高的电源电压抑制比(Power Supply Rejection Ratio,PSRR).

针对以上问题,本文通过电阻将亚阈值区MOS管漏电流转换为电压,并与一阶温度补偿电压进行加权叠加,实现二阶温度补偿. 同时采用高增益的运放以及负反馈回路减少电源扰动的影响,从而获得了低温漂高电源电压抑制比的带隙基准电压源.

1 二阶温度补偿原理

为了获得高精度的基准电压,减少温度的影响,需对基准电压进行温度补偿. 一阶温度补偿原理如图1所示,具有负温度系数的三极管基级-发射极电压VBE与具有正温度系数的热电压VT形成补偿,得到一阶温度补偿电压Vref1[11]:

Vref1 = VBE + γVT (1)

式中:γ为温度补偿系数;VT = kT/q,k为玻尔兹曼常数,q为单位电荷量.

由于VBE存在高阶温度项,热电压无法完全补偿,导致Vref1的变化在低温区为曲率上升,在高温区为曲率下降,温度系数较大. 因此,需要对一阶温度补偿电压,进行二阶温度补偿. 二阶温度补偿原理如图2所示,通过转换亚阈值MOS管漏电流Id为补偿电压,得到具有高阶温度项的正温度系数电压Vref2. 再利用正温度系数电压Vref2对一阶温度补偿电压Vref1的高温区进行补偿,得到温度系数更低的二阶温度补偿电压VREF:

VREF = Vref1 + Vref2 = VBE + γVT + Vref2 (2)

2 电路设计

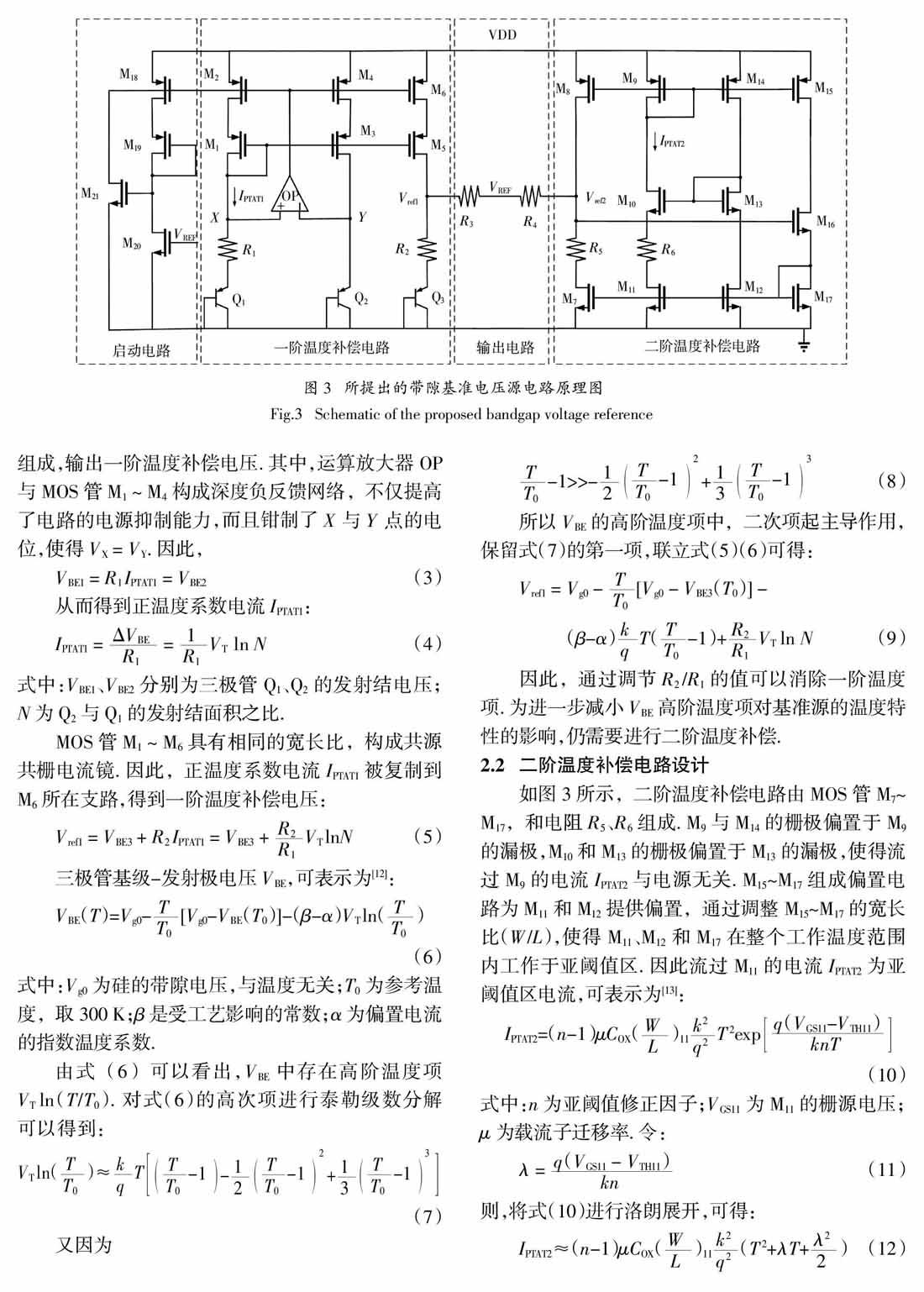

本文设计的带隙基准电压源电路如图3所示,主要由一阶温度补偿电路、二阶温度补偿电路、输出电路和启动电路组成. 利用工作于亚阈值区的MOS管产生具有高阶温度项的电流,并利用电阻将其转化成补偿电压,然后将补偿电压与传统的一阶温度补偿电压进行比例叠加,实现二阶温度补偿.

2.1 一阶温度补偿电路设计

如图3所示,一阶温度补偿电路由PMOS管M1~ M6,电阻R1、R2,三极管Q1 ~ Q3,以及运算放大器OP组成,输出一阶温度补偿电压. 其中,运算放大器OP与MOS管M1 ~ M4构成深度负反馈网络,不仅提高了电路的电源抑制能力,而且钳制了X与Y点的电位,使得VX = VY. 因此,

VBE1 = R1 IPTAT1 = VBE2 (3)

从而得到正温度系数电流IPTAT1:

式中:VBE1、VBE2分别为三极管Q1、Q2的发射结电压;N为Q2与Q1的发射结面积之比.

MOS管M1 ~ M6具有相同的宽长比,构成共源共栅电流镜. 因此,正温度系数电流IPTAT1被复制到M6所在支路,得到一阶温度补偿电压:

式中:Vg0为硅的带隙电压,与温度无关;T0为参考温度,取300 K;β是受工艺影响的常数;α为偏置电流的指数温度系数.

由式(6)可以看出,VBE中存在高阶温度项VT ln(T/T0). 对式(6)的高次项进行泰勒级数分解可以得到:

所以VBE的高階温度项中,二次项起主导作用,保留式(7)的第一项,联立式(5)(6)可得:

因此,通过调节R2 /R1的值可以消除一阶温度项. 为进一步减小VBE高阶温度项对基准源的温度特性的影响,仍需要进行二阶温度补偿.

2.2 二阶温度补偿电路设计

如图3所示,二阶温度补偿电路由MOS管M7~M17,和电阻R5、R6组成. M9与M14的栅极偏置于M9的漏极,M10和M13的栅极偏置于M13的漏极,使得流过M9的电流IPTAT2与电源无关. M15~M17组成偏置电路为M11和M12提供偏置,通过调整M15~M17的宽长比(W/L),使得M11、M12和M17在整个工作温度范围内工作于亚阈值区. 因此流过M11的电流IPTAT2为亚阈值区电流,可表示为[13]:

式中:n为亚阈值修正因子;VGS11为M11的栅源电压;μ为载流子迁移率. 令:

MOS管M8、M9、M14具有相同的宽长比,构成电流镜结构. 因此,M8所在支路的电流为IPTAT2,二阶补偿电压Vref2可表示为:

式中:VDS7为MOS管M7的漏源电压. M7与M11的宽长比和栅源电压都相同,因此M7工作于亚阈值区,其导通电阻可表示为:

为了进一步提高电源抑制比,M16、M17、M7、R5构成闭环负反馈电路. 当M16源极电位升高时,M17和M7的栅极电位升高,M7的漏极电位降低,电阻R5上端电位降低,从而M16的栅极电位降低. 由于漏极电流不变,最终导致M16的源极电位降低.

2.3 输出电路

如图3所示,输出回路由串联的电阻R3与R4组成,回路两端分别连接一阶温度补偿电压Vref1与二阶温度补偿电压Vref2,基准输出电压VREF即为电阻R3和电阻R4的连接点电压. 理想情况下,一阶温度补偿电压Vref1与二阶温度补偿电压Vref2的值相等,则输出回路没有压降,无电流流过电阻,即VREF = Vref1 = Vref2. 实际上,Vref1与Vref2之间存在较小的压降,则输出回路中有电流从高电位流向低电位,从而平衡Vref1和Vref2的差距,使之趋于一致. 因此,基准输出电压VREF可表示为:

因此,根据式(20)(21)的约束关系设置电阻值,即可得到温度系数(Temperature Coefficient,TC)近似为零的基准输出电压.

2.4 启动电路

如图3所示,启动电路由MOS管M18~M21组成,保证基准源正常启动. 其中,M18~M20的源漏极相互连接,构成从VDD到地的支路. M20的栅极与基准输出电压VREF连接;M19的栅漏极短接,并于M21栅极相连. 当电路接通电源时,所有支路处于零电流状态,M21栅极处于高电位,M21导通,并产生电流以启动电流镜,电路进入正常工作状态,输出电压使得M20导通,M21截止.

3 电路仿真与分析

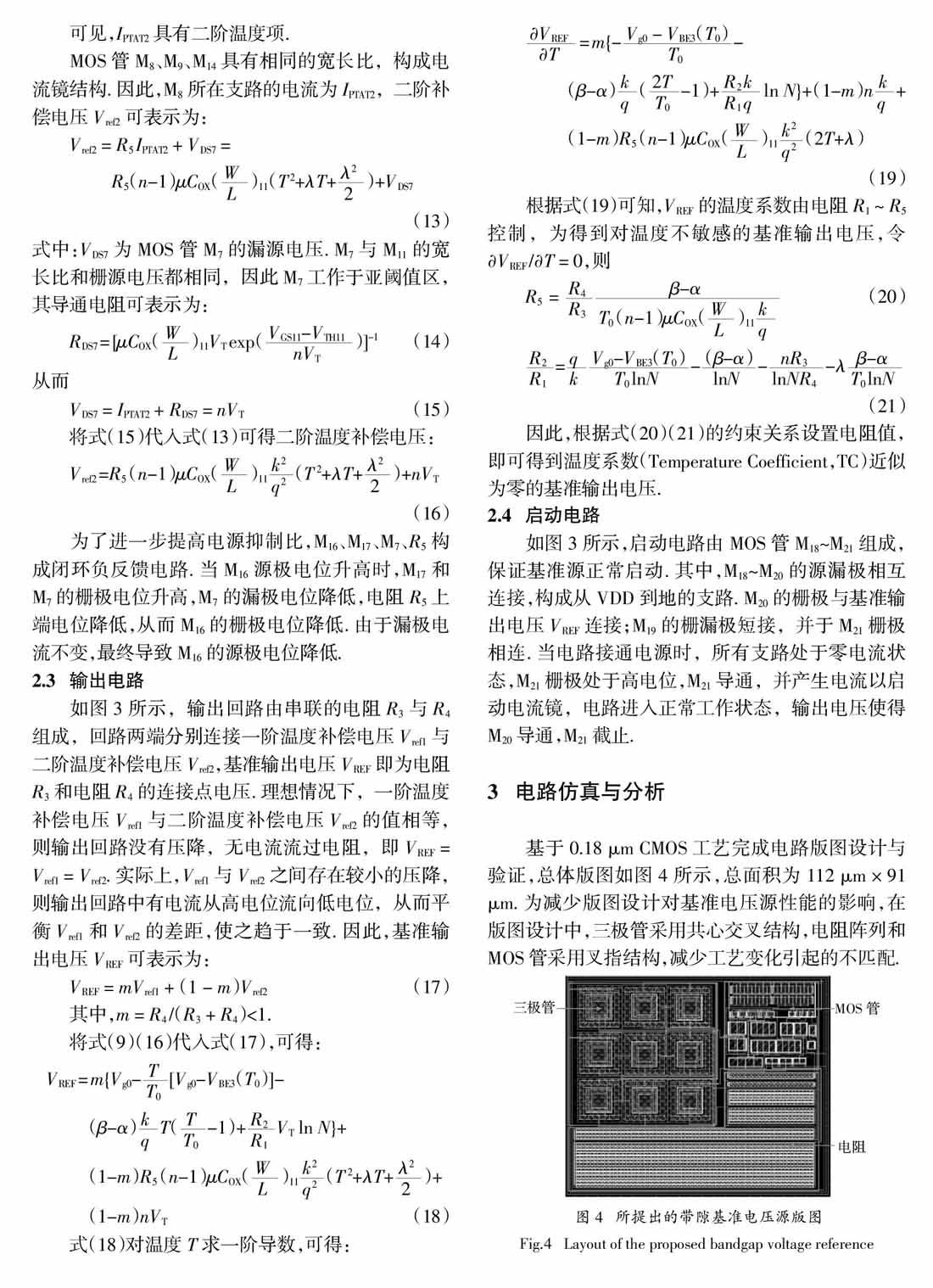

基于0.18 μm CMOS工艺完成电路版图设计与验证,总体版图如图4所示,总面积为112 μm × 91 μm. 为减少版图设计对基准电压源性能的影响,在版图设计中,三极管采用共心交叉结构,电阻阵列和MOS管采用叉指结构,减少工艺变化引起的不匹配.

采用Cadence公司的Spectre工具,完成电路前后仿真. Vref1随温度变化曲线如图5所示. 当T = 27 ℃时,Vref1 = 1.295 84 V. 当温度在-40~110 ℃变化时,Vref1的最大值为1.295 92 V,最小值为1.293 24 V. Vref1的变化量为2.68 mV,根据公式(22)可求得Vref1的温度系数为13.78 ppm/℃.

式中:VMAX与VMIN分别为输出电压的最大值和最小值;VREF为常温下(27 ℃)的输出电压值;TMAX与TMIN分别为使用温度范围的最大值和最小值.

经过亚阈值区MOS管漏电流转换电压的补偿后,基准电压VREF的温度特性曲线如图6所示. 在T = 27 ℃时,VREF = 1.220 04 V. 当温度在-40~110 ℃变化时,VREF的最大值为1.220 19 V,最小值为1.219 58 V. VREF的变化量为0.61 mV,由式(22)可得温度系数为3. 3 ppm/℃. 与一阶温度补偿电压Vref1相比,二阶温度补偿电路有效的补偿了Vref1中的高阶温度项,降低了基准输出电压的温度系数,提高了温度稳定性.

电源电压抑制比随频率的变化曲线如图7所示. 由于分别在一、二阶温度补偿电路中构建了闭环负反馈回路,该基准源在低频时具有较高的电源电压抑制比,在频率为100 Hz时,PSRR=-96 dB@100 Hz.

本文设计的基准电压源与同类带隙基准源性能对比如表1所示. 可以看出,由于采用了二阶温度补偿电路,并构建了闭环负反馈网络,该基准电压源具有小的温度系数和高的电源抑制比. 虽然采用多个电阻,使得电路易受到工艺的影响. 但电路中电阻的阻值呈比例关系,通过电路版图的匹配设计可以有效解决此问题.

4 结 论

本文提出了一种低温度系数、高PSRR的带隙基准电压源电路. 利用工作于亚阈值区的MOS管的漏电流实现二阶温度补偿,并通过推导其温度特性模型,对器件参数进行优化设计. 相比于传统的基准源,通过采用高增益运放和负反馈回路,在不增加功耗的情况下,提高了电路的电源电压抑制比. 仿真结果表明,在1.8 V的电源电压下,基准输出电压为1.22 V;温度在-40~110 ℃变化时,温度系数为3.3 ppm/℃;低频电源电压抑制比为-96 dB@100 Hz;静态电流仅为33 μA. 因此,该基准电压源虽然使用了多个电阻,但具有较高的精度和较低的功耗,能够满足高精度集成电路系统的需求.

参考文獻

[1] 曾健平,田涛,刘利辉,等. 低功耗高电源抑制比CMOS带隙基准源设计[J]. 湖南大学学报(自然科学版),2005,32(5):39—42.

ZENG J P,TIAN T,LIU L H,et al. Design of CMOS bandgap voltage reference with low power and high PSRR[J]. Journal of Hunan University (Natural Sciences),2005,32(5) 39—42. (In Chinese)

[2] BROKAW A P. A simple three-terminal IC bandgap reference[J]. IEEE Journal of Solid-State Circuits,1974,9(6):388—393.

[3] WIDLAR R. New developments in IC voltage regulators[C]//1970 IEEE International Solid-State Circuits Conference. Digest of Technical Papers. Philadelphia,PA:IEEE,1970:158—159.

[4] ZHU G Q,YANG Y T,ZHANG Q D. A 4.6-ppm/℃ high-order curvature compensated bandgap reference for BMIC[J]. IEEE Transactions on Circuits and Systems II:Express Briefs,2019,66(9):1492—1496.

[5] ANDREOU C M,KOUDOUNAS S,GEORGIOU J. A novel wide-temperature-range,3.9 ppm/℃ cmos bandgap reference circuit[J]. IEEE Journal of Solid-State Circuits,2012,47(2):574—581.

[6] DUAN Q,ROH J. A 1.2-V 4.2-ppm/℃ high-order curvature-compensated cmos bandgap reference[J]. IEEE Transactions on Circuits and Systems I:Regular Papers,2015,62(3):662—670.

[7] MING X,HU L,XIN Y L,et al. A high-precision resistor-less CMOS compensated bandgap reference based on successive voltage-step compensation[J]. IEEE Transactions on Circuits and Systems I:Regular Papers,2018,65(12):4086—4096.

[8] WANG B,LAW M K,BERMAK A. A precision cmos voltage reference exploiting silicon bandgap narrowing effect[J]. IEEE Transactions on Electron Devices,2015,62(7):2128—2135.

[9] 肖璟博,陈敏,张成彬,等. 低功耗双带隙结构的CMOS带隙基准源[J]. 湖南大学学报(自然科学版),2017,44(8):124—130.

XIAO J B,CHEN M,ZHANG C B,et al. CMOS bandgap reference of low-power-consumption double-bandgap structures[J]. Journal of Hunan University (Natural Sciences),2017,44(8):124—130. (In Chinese)

[10] CHEN H M,LEE C C,JHENG S H,et al. A sub-1 ppm/℃ precision bandgap reference with adjusted-temperature-curvature compensation[J]. IEEE Transactions on Circuits and Systems I:Regular Papers,2017,64(6):1308—1317.

[11] 毕查德·拉扎维. 模拟CMOS集成电路设计[M]. 陈贵灿等译.西安:西安交通大学出版社,2003:314—320.

BEHZAD R. Design of analog CMOS the integrated circuits[M]. Translate by CHEN G C,et al. Xian:Xian Jiaotong University Press,2003:314—320. (In Chinese)

[12] TSIVIDIS Y P. Accurate analysis of temperature effects in I/SUB c/V/SUB BE/ characteristics with application to bandgap reference sources[J]. IEEE Journal of Solid-State Circuits,1980,15(6):1076—1084.

[13] PIERRE R F. Semiconductor device fundamentals[M],Boston:Addison Wesley,1996:489—492.

收稿日期:2020-11-23

基金项目:国家自然科学基金资助项目(61404011),National Natural Science Foundation of China(61404011);长沙市科技计划重点项目 (kq1901102),The Key Projects of Changsha Science and Technology Plan (kq1901102);湖南省教育廳科学研究项目(20K007),Scientific Research Fund of Hunan Provincial Education Department(20K007)

作者简介:谢海情(1982—),男,湖南耒阳人,长沙理工大学副教授,博士

通信联系人,E-mail:zengjp@hnu.edu.cn