片上多通道低电容系统级静电防护电路设计

许建蓉,汪西虎,刘 伟,李 晶

(西安邮电大学 电子工程学院,陕西 西安 710121)

USB Type-C 是目前电子设备中使用最多的接口类型,在数据传输方面,每个通道的传输速率可以达到10 Gbps;在物理结构上,采用双面对称结构,支持正反插;在功能方面,能够集数据传输、音频传输、功率传输于一体;在应用方面,涉及手机、商务笔记本电脑、显示器等多个领域[1-2]。由于Type-C 接口的工作特性及应用环境需要其支持热插拔动作,导致接口容易受到静电放电的影响,因此需要为接口提供系统级静电保护[3]。目前,绝大多数Type-C 接口采用片外放置瞬态电压抑制二极管(Transient Voltage Suppressor,TVS)器件的方案达到系统级静电要求,不利于芯片的小型化,而且Type-C 接口对数据传输的容错率有严格要求,因此需要根据Type-C 接口的防护需求及实际工作环境在单芯片上集成多通道的系统级静电防护电路,同时保证端口的低电容特性,提高接口的可靠性。

Type-C 接口中,两组D+、D-引脚用于传输USB2.0 的数据信号;CC1 和CC2 作为配置通道,配置不同的模式;SBU1 和SBU2 作为边带通道,用来传送辅助信号[1-3]。芯片正常工作时D+、D-引脚的最高电压为5.5 V,将其定义为低压端口;CC1、CC2、SBU1 和SBU2 引脚的最高电压能够达到24 V,将其定义为高压端口。为保证接口的可靠性,对ESD(静电放电)端口防护电路提出相关可靠性指标:抗静电能力达到IEC61000-4-2 接触放电±8 kV;D+、D-端口电容需小于2 pF,CCX 端口电容需小于100 pF,SBUX 端口电容需小于10 pF。因此需要针对8 个端口提供相应的低电容、系统级静电防护方案。文献[4]提出一种衬底改造的GGNMOS,该结构具有较低的触发电压,但是由于其增加了额外的电源轨控制PMOS辅助触发衬底部分,使整体电路的版图面积和寄生电容有所增加,不适用于多通道低电容的ESD 防护;文献[5]针对可控硅整流器(SCR)防护结构触发电压较高问题,提出利用PMOS 器件触发的SCR 结构,降低了触发电压,但其容易造成闩锁问题;文献[6]对GGNMOS 结构进行改良,提出一种GGNMOS+RC NMOS 的ESD 防护结构,使电路防护能力达到IEC61000-4-2 接触放电±2 kV。以上文献中的方案只能满足部分要求,并不能同时满足多通道、低电容和系统级静电防护的要求。鉴于此,本文提出基于导流二极管与ZCNMOS 结构构建的系统级静电放电保护架构,通过ZCNMOS 结构泄放ESD 大电流,利用导流二极管隔离静电泄放器件的大电容,保证端口信号完整性。

1 电路设计

1.1 静电防护架构设计

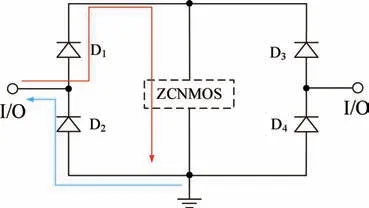

本设计分别针对低压端口和高压端口提出静电防护方案,图1 所示为基于ZCNMOS 结构的低压端口防护电路,通过导流二极管D1-D4可降低端口电容。当正向ESD 脉冲来临时,导流二极管D1和D3导通,将电流导向ZCNMOS 结构,再经ZCNMOS 结构将电流泄放至地,则I/O 端口的钳位电压约为D1正向导通电压Vbe与ZCNMOS 结构上的压降之和,同时需要保证正向脉冲来临时,二极管D2的耐压值高于I/O 端口钳位电压,防止其被反向击穿;当反向ESD 脉冲来临时,导流二极管D2和D4导通,泄放自地至I/O 端口的静电,则I/O 端口电压被D2或D4钳位在正向导通电压Vbe左右,同时需要保证二极管D2和D4具有较高的泄流能力。D+、D-两个引脚共用一个ZCNMOS 结构,可将低压端口ESD 防护电路的版图面积缩减至原来的1/2。

图1 低压端口防护电路Fig.1 Protection circuit of low-voltage port

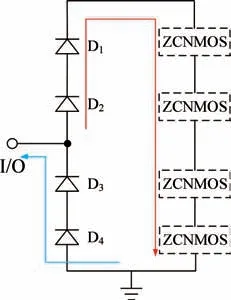

基于ZCNMOS 结构的高压端口防护电路如图2 所示,采用ZCNMOS 结构级联方式提高触发电压,大电流泄放通路与低压端口相同。由文献[7]可知,当芯片发生热插拔事件时,由于振铃效应,高压端口的瞬态电压峰值约为最高电压的1.8 倍,即44 V 左右,因此二极管D1、D4的反向击穿电压必须高于44 V;由于反向击穿电压高的二极管正向放电能力较弱,为保证过流能力,二极管的结面积必然较大,不易满足低电容的要求。为此,通过串联低击穿电压、低电容的二极管D2和D3将I/O 端口与ZCNMOS 结构中静电泄放器件的大电容进行隔离,从而降低端口电容。CC1、CC2、SBU1 和SBU2 引脚共用一个ZCNMOS 结构,可将高压端口ESD 防护电路的版图面积缩减至原来的1/4,减少整体版图面积。

图2 高压端口防护电路Fig.2 Protection circuit of high-voltage port

1.2 ZCNMOS 结构设计

GGNMOS 结构在ESD 防护电路中应用非常广泛,为了保证较大的衬底电流,MOS 管采用叉指结构,导致MOS 管中寄生双极性晶体管出现不均匀导通的现象,有可能只有2~3 根叉指优先导通。此时,ESD 防护能力相当于2~3 根叉指的防护能力,导致ESD 防护能力降低[8-9],这也是ESD 设计的瓶颈所在。因此,本文对 GGNMOS 进行优化,设计栅极耦合的ZCNMOS 结构进行静电防护。

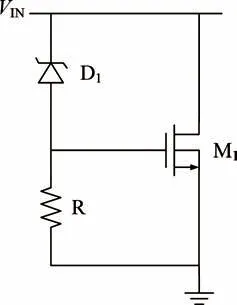

ZCNMOS 结构如图3 所示,M1表示高压隔离型5 V 静电泄放器件,为了保证过流能力,采用叉指结构,D1为稳压二极管,电阻R 用来限制流过D1的电流,防止MOS 管M1栅氧击穿。当端口发生ESD 事件时,二极管D1反向击穿,使电阻R 上产生一定的压降,M1的栅极在应力作用下被瞬时上拉[10]。当栅极电压达到阈值电压之后,MOS 管M1导通,随着电流的增加,电流向下走并从衬底流出,使P 阱电阻上的压降达到0.7 V,则寄生晶体管NPN 导通,开始泄放ESD 大电流。与GGNMOS 相比,ZCNMOS 结构利用二极管与电阻在MOS 管M1的栅极耦合一定的电压,使MOS 管M1导通,代替GGNMOS 中PN 结击穿产生的衬底电流,因此具有更低的触发电压,而且会产生更高的衬底电流,有利于双极晶体管的导通,从而保证叉指器件均匀开启[11]。

图3 ZCNMOS 结构Fig.3 Structure of ZCNMOS

根据芯片的设计要求,当芯片正常工作时,为了保证防护电路不被误触发,ZCNMOS 结构必须具有一定的耐压值。当端口发生ESD 事件时,稳压二极管被击穿,并且随着VIN的不断升高,M1的栅极电压达到其阈值电压VTH(1.5 V)时,M1管完全导通,泄放大电流,通过稳压二极管D1和MOS 管M1的作用,使ZCNMOS 结构的单级钳位电压约为二极管稳压值(6 V左右)与MOS 管栅源电压VGS之和,即7.5 V 左右。为了设计安全考虑,应保留10%的设计余量,因此M1管的漏端和源端的Vds耐压值至少需要高于8.5 V,由于本设计采用的是5 V 的MOS 管,通过增大漏端到栅端的距离提高耐压值,从而保证芯片正常工作时,防护电路关闭。

2 器件设计

Type-C 接口保护芯片采用0.25 μm 的BCD 工艺,其中主体电路采用了自对准硅化物(Silicide)和低掺杂漏(Lightly-Doped Drain,LDD)工艺技术。这些先进工艺改善了器件性能,但同时给ESD 防护电路带来了新的问题,因此需要对工艺进行改进,消除这些不利因素。

2.1 静电泄放器件优化

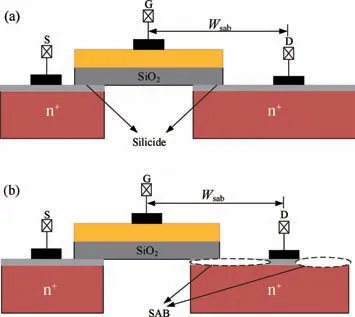

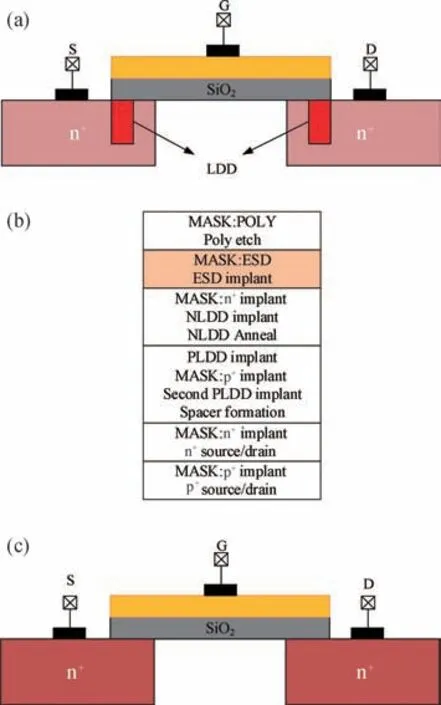

图4(a)表示Silicide 结构,通常使用Ti、W、Co等耐高温材料的金属硅化物覆盖MOS 器件的源极和漏极,形成低阻的硅化物薄膜,以降低其方块电阻和接触电阻,改善器件性能。但是当ESD 发生时,由于硅化物薄膜电阻小,使电流首先沿着有源区表面流动,导致器件发生热击穿而损坏,大幅度降低了ESD 防护性能[9]。为了解决Silicide 结构引起的ESD 防护性能降低的问题,本文在Silicide 结构的漏端采用金属硅化物阻挡(Silicide Blocking,SAB)技术,如图4(b)所示,在Silicide 结构的基础上增加一张掩膜版来阻挡金属硅化物,在漏端形成有效的镇流电阻,使ESD 电流分布更均匀。图4 中Wsab表示漏端到栅端的距离,本设计通过调整Wsab的大小保证器件的耐压值。

图4 器件结构优化。(a)Silicide 结构;(b) SAB 结构Fig.4 Optimization of device structure.(a) Structure of Silicide;(b) Structure of SAB

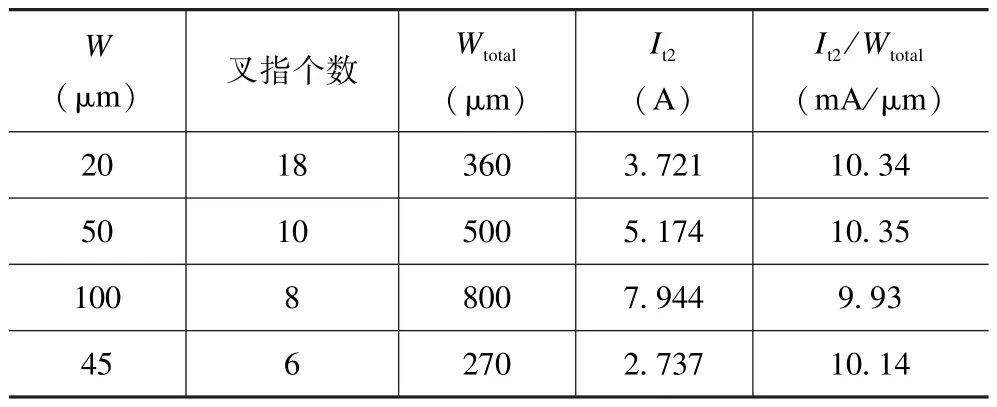

图5(a)表示LDD 结构,该结构能够缓解源漏两侧沟道处的强电场,抑制热载流子效应。但是由于LDD 结构结深只有约0.02 μm,这相当于在源极和漏极两端形成两个尖端,在静电放电过程中,较高的热量集中在这两个尖端,使其极易在高温下熔融,造成器件漏端与体、源端的短路,易在静电放电中发生烧毁。为了克服因LDD 结构造成ESD 防护能力下降的问题,本设计对器件工艺进行优化,如图5(b)所示,在源漏区注入之前,通过大角度离子注入(Electro-Static Discharge Implant,ESD_IMP)技术消除LDD 结构,降低触发电压,消除尖端放电现象,提高ESD 防护能力。工艺优化后的器件如图5(c)所示,并且对优化后栅长L为1.2 μm 的器件过流能力进行测试,结果如表1 所示,其中W表示栅宽,Wtotal表示总体栅宽,It2表示过流能力。从表1 可以发现器件过流能力由优化前的4 mA/μm 提高到10 mA/μm,提升了1.5 倍。

表1 工艺优化后器件的过流能力Tab.1 Overcurrent capability of the device after process optimization

图5 器件工艺优化。(a)LDD 结构;(b)工艺优化流程;(c)加入ESD_IMP 的NMOS 结构图Fig.5 Optimization of device process.(a) Structure of LDD;(b) Steps of process optimization;(c) NMOS structure diagram with ESD_IMP added

2.2 导流二极管优化

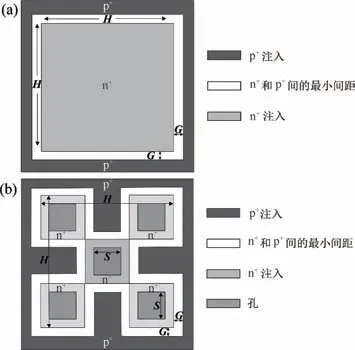

对于导流二极管而言,需要考虑其正向导通时的过流能力、反向击穿电压和电容。在本设计中,所有导流二极管的过流能力都必须大于25 A。对于低压端口防护电路中的D1-D4和高压端口防护电路中的D2、D3二极管,均采用低击穿电压和低电容的二极管,选择p+/Nwell 二极管用于高端导流二极管,n+/Pwell 二极管用于低端导流二极管,对于高压端口防护电路而言,二极管D1和D4的反向击穿电压必须高于44 V。为了减少结电容,对二极管的版图进行优化,文献[12]中已证明,随着二极管PN 结周长的增加,二极管的失效电流基本成比例增加,而且随着二极管PN结面积的减小,二极管的寄生电容减小,因此本文通过提高二极管PN 结的周长面积比来减少寄生电容[13]。优化前后n+/Pwell 二极管的版图如图6 所示,在n+注入区掏孔以减少PN 结电容,图中,H表示n+注入区的边长,G表示n+注入区和p+注入区的最小间距,S表示孔的边长。则优化后二极管PN 结周长表示为:C2=H ×4×5,与优化前二极管PN 结周长C1=4H相比,增加了:

图6 导流二极管版图。(a)优化前二极管版图;(b)优化后二极管版图Fig.6 Layout of diversion diode.(a) Diode layout before optimization;(b) Diode layout after optimization

优化后二极管PN 结面积表示为S2=5×与优化前二极管PN 结面积S1=H2相比,减少了:

则优化后二极管的寄生电容表示为:

式中:Cj为二极管单位面积寄生电容;Cjsw为二极管侧壁单位长度寄生电容。由式(1)~(3)可知,在保证二极管失效电流的情况下,适当减小PN 结面积,能够减小二极管的寄生电容,达到低电容的设计要求。

3 测试结果与讨论

采用TLP(Transmission-Line-Pulsing)和静电枪两种方法对防护电路进行测试,TLP 测试是将方波测试脉冲加到待测器件的两脚之间进行测试,能够得到较为准确的I-V曲线,而且波形噪声分量低,测试结果较稳定[14];静电枪测试是直接对芯片引脚进行接触放电或气隙放电,受环境因素影响较大,一般用于得到被测器件的损伤阈值电压[15]。

3.1 TLP 测试

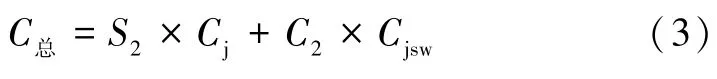

利用TLP 系统对芯片的低压端口和高压端口进行测试,得到的I-V曲线如图7 所示。对低压端口D+、D-而言,正常工作电压不超过5.5 V,从图7(a)的测试结果可以看出,低压端口防护电路的触发电压为8.6 V,维持电压为8 V,大于D+、D-端口的最大工作电压;对高压端口CC1、CC2、SBU1 和SBU2 而言,最大电压为24 V,从图7(b)的测试结果可以看出,高压端口防护电路的触发电压为29.5 V,维持电压为27.5 V,大于端口的最大电压。而且两者的二次失效电流均大于25 A,表明ESD 性能能够达到IEC61000-4-2 接触放电±8 kV,气隙放电±15 kV,即低压端口和高压端口电路均满足系统级静电防护要求。

图7 端口TLP 测试结果。(a)低压端口;(b)高压端口Fig.7 TLP test results of the ports.(a) The low-voltage port;(b) The high-voltage port

3.2 静电枪测试

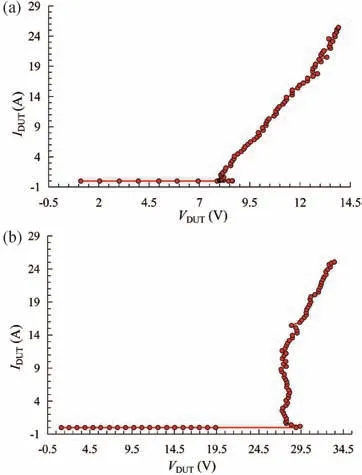

采用静电枪对芯片C_CCX 和C_SBUX 引脚进行接触放电±8 kV,观察CCX 和SBUX 引脚的波形,C_CCX引脚接触放电±8 kV 的结果如图8 所示。从图8(b)和(d)可以发现,由于静电枪注入波形不稳定,而且受到环境因素及测试线、键合丝上寄生电阻的影响,使得CC1 端口接触放电±8 kV 的钳位电压分别为372 V 和-362 V。由文献[16]可知,静电枪测试方法受测试环境影响因素较大,导致测试结果存在一定的误差,静电枪测试完成后,再对该芯片其他性能进行测试,结果表明各参数指标正常,由此说明防护电路能够达到接触放电±8 kV 的耐压能力。

图8 CC1 IEC 61000-4-2 ±8 kV 响应波形。(a) C_CC1 +8 kV;(b) CC1 +8 kV;(c) C_CC1 -8 kV;(d) CC1 -8 kVFig.8 Response waveform of the CC1 IEC 61000-4-2 ±8 kV.(a) C_ CC1 +8 kV;(b) CC1 +8 kV;(c) C_ CC1 -8 kV;(d) CC1 -8 kV

4 结论

本文提出了基于导流二极管与ZCNMOS 结构构建的静电放电保护架构,通过ZCNMOS 结构改善了GGNMOS 结构中电流分布不均匀的现象。针对静电泄放器件,采用SAB 技术和ESD_IMP 技术,提高了ESD 防护性能;对二极管版图进行优化,减少了寄生电容。测试结果表明,ESD 防护电路能够满足系统级IEC61000-4-2 接触放电±8 kV,气隙放电±15 kV 的静电防护要求,CCX 端口、SBUX 端口和D+、D-端口电容分别为74,6 和1.7 pF,满足低电容要求,电路结构简单、利于集成,具有良好的应用前景。