利用内存行激活信息的DRAM行扰动问题研究

章铁飞,徐 斌

浙江工商大学 计算机与信息工程学院,杭州310018

动态随机存取存储器(DRAM)在商业计算机系统中被广泛用作主存,其由一个电容器和一个晶体管构成,通过电容器的充放电来存储一位信息。DRAM通过减小存储单元尺寸来持续增加容量,但也导致芯片易受到干扰误差的影响,当某DRAM内存行中的存储单元因为访问被激活时,相邻行的存储单元易受到干扰,导致相邻行的数据错误[1-2],因为来自相邻行的耦合降低阈值电压并增加存储单元的漏电流,较高的漏电流引起更快的电荷从DRAM存储单元的电容器泄漏,导致存储单元丢失数据。这种相邻行因为数据访问、频繁激活而导致存储单元数据错误的现象称之为行扰动(Row Hammering)。

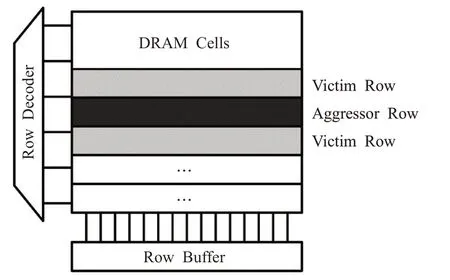

当某DRAM内存行被访问时,它必须先被激活后,才能读写数据。一内存行越频繁地被访问,则被激活的次数越多。图1显示攻击行(aggressive row)频繁地激活,导致其相邻的两个受害行(victim row)出现行扰动问题。由于漏电效应,DRAM单元默认地周期性刷新补充电荷。在刷新间隔内,如果相邻行数据频繁的激活次数超过阈值,则大概率地会导致DRAM单元出现行扰动问题。该激活的阈值,称之为行扰动阈值(RHth)。随着DRAM存储单元尺寸的进一步缩小,行扰动阈值不断降低,使得行扰动问题日益严重。此外,专门设计的恶意程序[3-4]可能会故意频繁地将缓存的内容刷新回内存,存储单元更容易地达到行扰动阈值。为保护数据的完整性和安全性,未来的DRAM必须有针对性地解决行扰动问题。

图1 行扰动问题Fig.1 Row hammering problem

为缓解行扰动问题,在受害行达到行扰动阈值之前,内存控制器主动向受害行发送内存行刷新操作,以补充受害内存行存储单元的电荷,防止受害行出现行扰动问题,这种方法称为主动激活。与主动激活相对应,被动激活发生在受害行被激活以服务数据请求时,即受害行发生读写数据操作而被激活。与主动激活相比,被动激活具有相同的防止数据丢失的效果。与被动激活发生在正常的数据读写不同,主动激活需将刷新操作插入到数据请求队列,干扰到正常的数据读写,影响内存读写的性能。因此利用被动激活,可以在不影响内存性能的情况下,规避主动激活对性能的不利影响。

本文提出一种基于内存行的最近激活信息的解决DRAM内存行扰动的方法(RACPR),该方法保护受害行免受行扰动影响。RACPR大大减少额外的数据跟踪结构,避免传统的基于计数器的策略所需的存储开销[5]。利用被动激活对行扰动具有相同的保护作用,RACPR使用行激活计数器(RAC)结构来记录受害行的被动激活信息,消除不必要的主动激活操作,因此RACPR以可忽略的存储和性能开销,提供可靠的行扰动解决方案。本文针对行扰动问题做出以下贡献:

(1)本文证明被动激活与主动激活具有相同的抗行扰动效果,且对内存访问性能没有不利影响。

(2)本文引入最近激活计数器(RAC)结构来记录受害行的被动激活信息,利用被动激活来防止行扰动。

(3)基于内存行的RAC信息,本文引入概率刷新方法,以较小的概率向行发出主动激活操作。本文的概率刷新方法不是直接发起主动激活,而是基于RAC的值充分利用被动激活,消除不必要的主动激活操作,将对性能的影响降至最低。

1 动机和观察

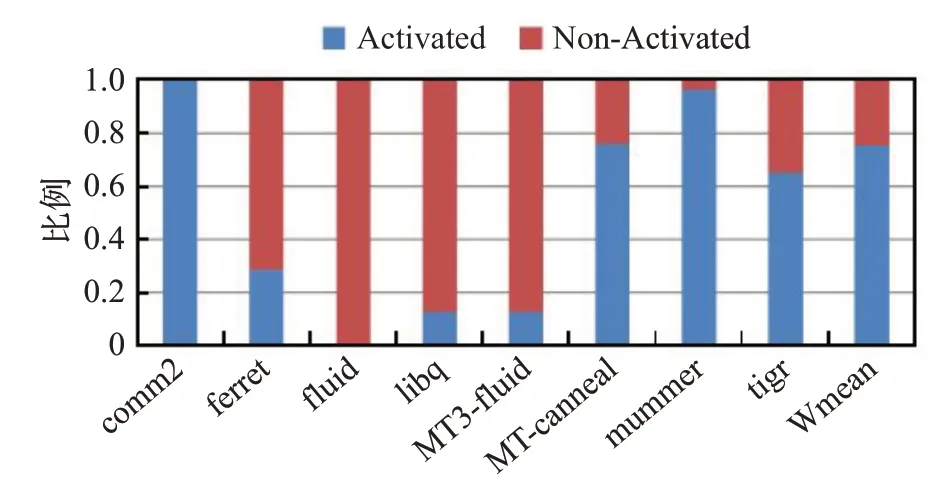

给定一攻击行,其激活次数超过行扰动阈值,系统无需发出保护受害行免受行扰动的主动激活操作,因为攻击行数千次的激活期间,受害行可能会同时经历几次被动激活。从电路的角度看,刷新内存行和激活内存行是相同的操作,因此受害行的单元在被动激活过程中完全地充满电荷,避免行扰动的数据错误。因此必须额外地检查受害行是否在攻击行超过行扰动阈值的同一时间间隔内发生被动激活,而不是只关注攻击行的激活次数是否超过行扰动阈值。图2显示在攻击行超过行扰动阈值的时间间隔内,受害行发生被动激活的比例,基准测试程序是PARSEC和SPEC,其中的行扰动阈值为32 000。

图2 受害行的被动激活百分比Fig.2 Passive activation percentage of victim rows

定位所有超过行扰动阈值的攻击行,确定达到扰动阈值的时间间隔,并在相同的时间间隔内收集所有受害行的被动激活信息。图2中所示,隶属于不同基准程序的受害行的被动激活模式相异,一个极端是comm2的所有受害行都存在被动激活,另一个极端是fluid,其所有受害行都不存在被动激活。然而数据显示应用程序中超过75%的受害行存在被动激活。由于受害行存储单元随着被动激活而充电,可以避免行扰动问题。下一章将描述基于这一观察的RACPR方法。

2 RACPR方法

利用被动激活操作,可取消一些不必要的主动激活来提升存储器性能,本文利用最近激活计数器(RAC)来记录受害行的最近被动激活信息,然后提出一种基于最近激活计数器的概率刷新方法,以可忽略不计的开销来解决行扰动问题。

2.1 最近激活计数器

要记录受害行的最近激活信息,如果简单地使用计数器[5]来存储该信息,将导致不可接受的存储开销。针对8 GB容量的DRAM存储器,按每行配以16位计数器(每行按8 KB)计算,累积需要数十兆字节的额外存储空间。此外,计数器仅记录激活的累计次数,而不记录每次激活在时间间隔内分布的具体时间信息,因此本文使用一位的最近激活计数器(RAC)来记录信息。值为1表示该行最近已被激活,而值为0表示该行在预定的时间间隔内未被激活。当最近激活计数器值为1时,可避免主动激活操作,因为目标行最近被激活并重新充电。

为利用被动激活,本文解决以下的问题:何时以及如何设置RAC,以及在哪里设置存储最近激活计数器。每次读取、写入或刷新行时,内存行的RAC都设置为1。在一个重置时间间隔(RTI)后,随机存取存储器被重置为0,在该时间间隔内,给定行的数据通过最近的被动激活被保护免受行扰动的影响,因此主动刷新是不必要的。RTI的时间长度以行扰动阈值达到所需的最少时间决定。因为只有当给定行受到的扰动次数超过阈值时,才会出现数据错误。

最近激活计数器RAC的值反映内存行是否达到其重置时间间隔。当RAC的值为1时,表示目标内存行还在最近一次被动激活操作的保护时间范围内;当RAC的值为0时,表示目标内存行不在最近一次被动激活操作的保护时间范围内,即它的重置时间到。要设置RAC的值,一个方法是为目标内存行附加一个计时器。当目标行被激活时,其RAC值被设置为1,并且计时器开始计时。当计时器达到重置时间间隔时,实时时钟被重置为0。然而,给每一行指定一个定时器是不切实际的,将导致不可接受的开销。因此,本文对所有行的RAC以周期性方式更新,只需要单个定时器控制,避免每行所需的大量独立定时器的开销。

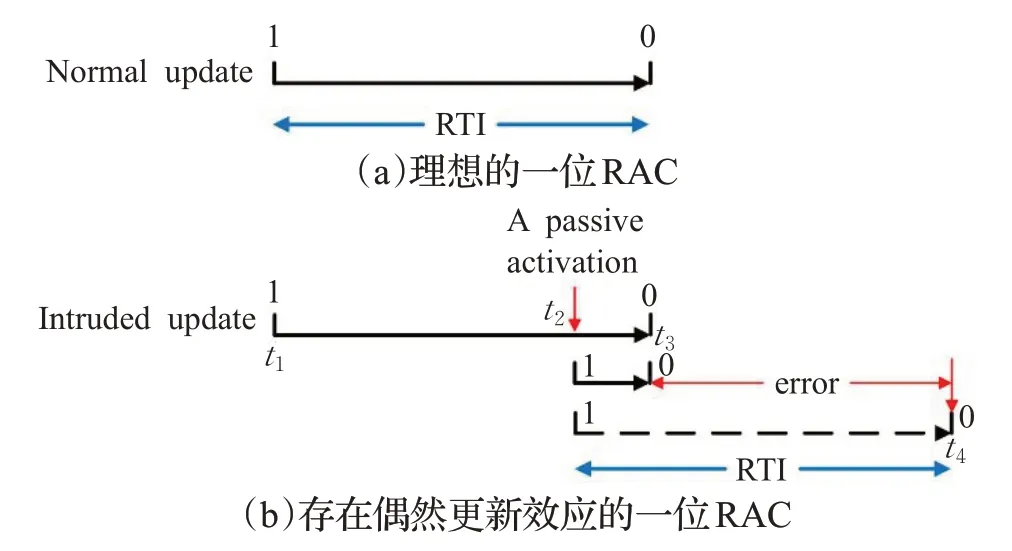

如图3(a)所示,给定行的RAC在RTI内从状态1切换到状态0。当RTI内没有被动激活操作时,RAC的值表示正确的RTI。然而如图3(b)所示,如果在RTI期间出现被动激活,t2时的被动激活将RTI延长至t4。但是默认的定期更新操作会在t3将RAC重置为0。因此,偶然的被动激活会导致RAC所指示的RTI小于实际值。这种给RTI引入错误的现象称为偶然更新效应。在t2非常接近t3的情况下,由偶然更新效应引起的最大误差可能与周期RTI一样大。假设被动激活随机分布在RTI上,那么偶然更新效应的期望误差是RTI/2。不能消除偶然更新效应,因为被动激活的发生无法预先预测,但是可以通过将一位RAC更新为二位的RAC来减少误差值。

图3 一位RAC和偶然更新效应Fig.3 One-bit RAC and accidental update effect

与一位RAC不同,二位RAC有四种状态,即11、10、01和00。当发生内存行被动激活时,RAC设置为11,并且RAC按一定的周期降序依次递减。二位RAC与一位RAC的不同之处在于其更新周期的时间长度。二位RAC的更新周期不是一个实时时间间隔,而是设置为实时时间间隔的1/3,偶然更新效应的误差与更新周期成正比,所以此时的偶然更新效应的最大误差变为重置时间间隔的1/3,如图4所示。较小的更新周期有助于减少偶然更新效应的误差,但增加更新操作的频率会产生成本问题。

图4 两位RAC的偶然更新效应Fig.4 Accidental update effect of two-bit RAC

算法1以重置时间间隔的1/3为周期更新,操作的开销可以忽略,原因以下两点:首先,内存行的RAC可以按块粒度组织,每个块由数百个RAC组成,更新操作作为一个整体对每个块执行,这意味着数百个RAC在一次更新操作进行状态切换,所以RAC更新的成本被分摊并大大降低。应用程序访问内存时,具有时间、空间局部性[6],在一定的时间间隔内,只有部分DRAM行经常被访问和激活。只有这些激活的DRAM行的相应RAC需要更新操作,因此开销可以忽略不计。

算法1两位RAC更新方法

输入:内存行的RAC值

输出:无

1.i(frow[i]发生被动激活)

2.{rac(row[i])=11;

3.}

4.fo(revery RTI/3)

5.{i(frac(row[i])>00)

6.{ rac(row[i])递减1;

7.}

8.}

2.2 基于随机存取存储器的概率刷新

传统的基于计数器的主动激活方法[5,7],主要思想是每个内存行分配计数器,每次激活则计数器累加1,根据计数器的值是否超过行扰动值,来决定是否对相邻受害行发起主动激活操作。所有基于计数器的主动激活方法的代价在于大量计数器产生的存储空间开销。本文采用概率的方法来避免这种不可接受的存储开销。

当特定内存行被访问激活时,以很小的概率向其相邻行发起主动激活操作。如果主动激活概率为1%,则每次内存行被激活时,存储器控制器都会访问随机数发生器,以确定是否对相邻受害行,发出主动激活操作。如果是,则对被访问行的相邻行执行主动激活操作。一内存行被激活的频率越高,就越有可能向其相邻行发出主动激活操作,让接近行扰动阈值的攻击行的相邻受害行有接近概率1的主动激活机会。

假设每次目标行被访问时,都以概率N向其相邻的行发出主动激活操作。假设M为行扰动阈值,系统的生命周期内M的实例数为k。在系统的整个生命周期中,因为没有主动激活,至少有一次失败的概率如下所示[3]:

面向未来的DRAM技术,假设M低至32 000。10年的运行时间里,k≈250亿。如果N分别设置为0.1%、0.2%和0.5%,相应的Pfailure分别为3.166×10-4、4.0×10-18和8.14×10-60。经实验表明,当N的值设定为0.2%时,主动激活操作在内存性能和行扰动问题的缓解之间取得良好的平衡。

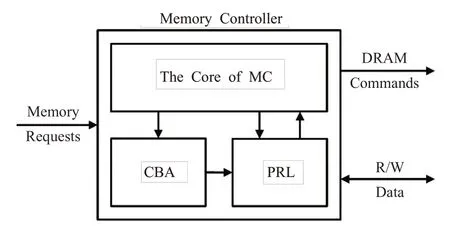

图5表示RACPR的总体设计,基于传统内存控制器的扩展,其中CBA存储内存行的RAC,而PRL是随机刷新逻辑电路。内存控制器的主要功能是将存储器命令调度到存储器,完成读或写请求。当其目标内存行被访问或刷新时,二位RAC按RTI值的1/3周期递减。RTI的下限值理论上分别由默认激活间隔(AI)和默认刷新间隔(RI)决定。默认间隔内的最大激活次数是RI/AI。给定行扰动值的情况下,RTI的下限为AI×RHth。此外,这种下限是在极端情况下获得的,在这种情况下,特定的行被连续且直接地激活RHth次。实验结果显示实际应用中RTI的值远远大于理论值。

图5 RACPR结构Fig.5 Architecture of RACPR

对于8 GB的DRAM存储器芯片,RAC的总存储空间仅为256 KB,仅占DRAM存储器空间的0.006%,与基于计数器的方案相比,这是一个显著的减少。对内存行的每次读取、写入和刷新都会对其二位RAC进行设置操作,并且RAC上的周期性递减操作会进一步增加对RAC的访问次数,因此RAC的访问容易成为瓶颈。为保证对RAC的快速访问,将RAC存储在内存控制器中。如果出于减少其存储开销的目的,RAC也可以使用计数器缓存结构,并存储在DRAM的保留区域[5]。

算法2RACPR方法

输入:内存行的RAC值

输出:无

1.i(f读写内存行row[i])

2.{产生0~n之间的随机数r;

3.i(fr≤nN)

4.{if(rac(row[i+1])==00)

5.向row[i+1]发送刷新请求;

6.i(frac(row[i−1])==00)

7.向row[i−1]发送刷新请求;

8.}

9.}

算法2显示RACPR的操作流程。受害行的RAC值,如果等于00,则主动激活操作以概率N发出。算法在[0,n]的范围内产生一个随机数,r小于nN的概率就是概率N。如果r小于nN,则PRL检查RAC模块,然后决定是否向存储器控制器的发送命令以插入主动激活命令。如果r大于nN,则不满足概率N,所以不需要发送主动激活命令。

3 实验评估

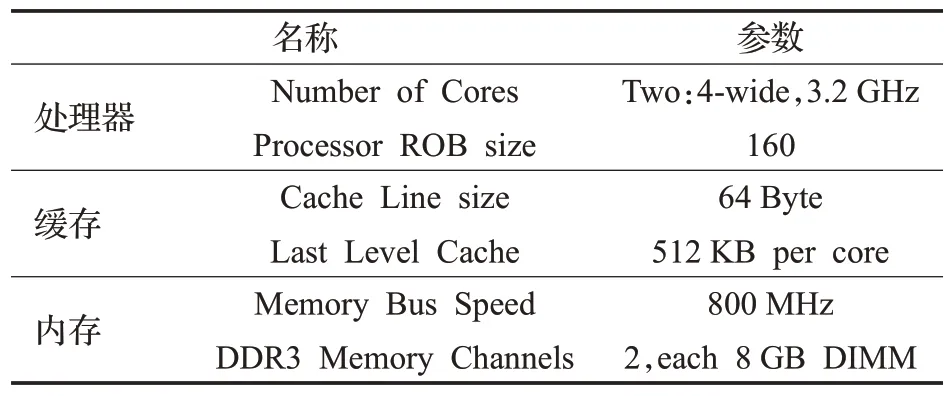

本文使用USIMM[8]内存模拟器和来自于PARSEC、BIOBENCH和商业基准程序来评估提出的方案。内存模拟器的存储芯片配置为8 GB芯片。表1显示模拟的内存系统的配置。为体现未来一代技术的发展,实验中的行扰动阈值RHth设置为32 000。

表1 系统配置Table 1 Setup of system

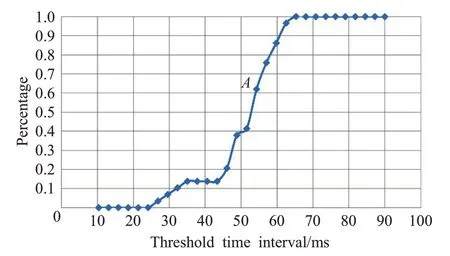

攻击行的激活次数超过RHth所需的最短时间称为阈值时间间隔(TTI)。实验跟踪不同基准的攻击行,并分别记录每行的TTI。图6显示TTI的分布,其中X轴代表以毫秒为单位的TTI,Y轴显示低于特定值的TTI的百分比值。点A表示62%的TTI小于54.3 ms。实际上,TTI决定RTI的值,因为RTI的长度是攻击行激活RHth次的最短时间。图6中,3.5%的TTI小于27 ms,6.9%的TTI小于30 ms,本文中的默认RTI设定为30 ms,主要基于如下的考虑:

图6 阈值时间间隔的百分比Fig.6 Percentage of different threshold time interval

(1)由于偶然激活更新效应引入的误差,实际的RTI比实际值平均小16.7%。测得的RTI为25 ms(默认RTI为30 ms),而25 ms以下的TTI不存在。

(2)大部分的TTI值大于30 ms。

图7根据执行时间显示主动激活对性能的影响,主动激活的概率值Pfailure从0.1%到0.5%不等。对于大多数基准测试程序,更高的主动刷新概率会降低更多性能:主动刷新的概率为0.5%,会导致执行时间增加2.5%,而主动刷新的概率为0.2%,只会导致执行时间增加1%。平均而言,0.2%的主动刷新概率会使执行时间增加约0.4%,这是一个可以忽略的性能影响。

图7 不同主动刷新概率对性能的影响Fig.7 Performance impact with active refresh

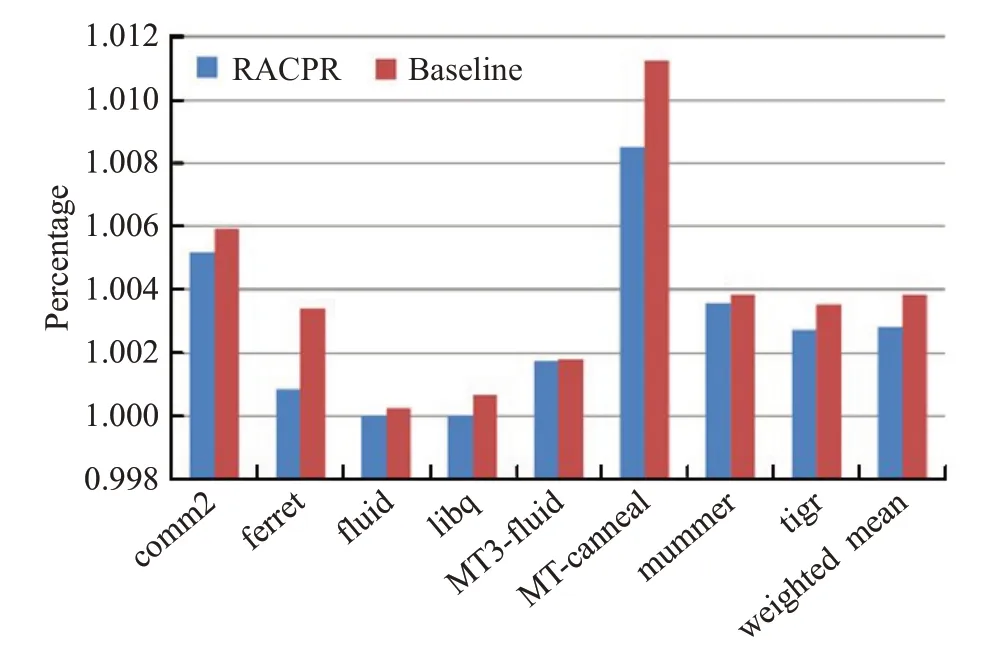

图8显示RACPR与以往的PARA[2]方法的性能对比,采用的主动激活概率均为0.2%,利用被动激活信息的RACPR可以大大减少主动刷新的次数,平均75%的主动刷新被消除。主动刷新的减少导致执行时间的减少。例如,MT-cannel将执行时间减少0.3%。通过探索被动激活信息,平均内存访问时间减少0.1%。请注意性能优势只是基准程序运行一段的收益,长期来看,累积的性能绝对优势显著,尤其是对于应用程序领域,如web服务器。

图8 RACPR与基本概率刷新方法的性能比较Fig.8 Performance comparison of RACPR and baseline

4 相关工作

随着DRAM存储器容量的增大,节点更小化,行扰动问题成为一个关键问题,不仅降低系统的可靠性,还暴露安全漏洞。奥努等人分析行攻击问题的根本原因,并研究各种解决方案[2,9-11],数据表明只需139 000次访问就能引发一个错误,每1 700个单元中最多有一个单元容易出错,并进一步提出概率邻近行激活(PARA)方法。PARA策略以很小的概率对当前访问行的相邻行执行额外的刷新。作为一种概率机制,它不能保证没有负面效果。另一方面,基于计数器的主动激活[5,12-13]在每一个动态随机存取存储器行中使用一个计数器来记录每行的激活次数,并且只对计数器值大于行锤击阈值的目标行的相邻行执行额外的刷新。这种设计保证没有负面效果,但代价是巨大的存储开销。为减少跟踪结构的存储开销,计数器可以组织成树形结构[6-8,14],每个计数器跟踪一组动态组大小的行。由于可导致相对湿度的行数受到行激活频率和动态随机存取存储器单元保持时间的最大值的限制,两次机制[1]仅使用少量计数器就可以准确检测潜在的相对湿度攻击。PRoHIT[15]提供一个概率管理的表,它以概率的方式跟踪受害者行候选,并且最上面的条目被额外刷新以缓解行攻击问题。

本文的方法主要是解决已有的PARA[2,5]方法的不足。PARA方法随机选择潜在的受害行,并对这些行执行主动激活操作。PARA方法没有考虑被动激活受害行,因此可能会对受害行进行不必要的刷新,从而导致性能开销。本文方法利用受害行的被动激活信息,克服PARA的限制,并有效解决行扰动问题。

5 结论

本文提出一种基于内存行最近激活信息来解决DRAM存储器行扰动问题的方法。本文使用RAC结构跟踪内存行的被动激活信息,并提出优化RAC的结构和操作,以降低其复杂性和开销。本文进一步在存储器控制器中实现基于RAC的概率刷新模块,以可忽略的性能开销以及0.006%的面积成本,解决行扰动攻击问题。实验结果表明,与以前的概率方法相比,本方法平均减少75%的主动激活操作,占用0.006%的存储容量,平均提升0.1%的内存访问性能。