一种超宽带超低相位噪声频率综合器

成斌 沈文渊 穆晓华 邓立科 税明月 王斌

(1. 中国电子科技集团公司第二十六研究所,重庆 400060;2. 重庆邮电大学光电工程学院,重庆 400065)

引 言

频率合成器作为电子系统的核心组成部分广泛地应用于雷达、电子对抗、通信、导航等军用和民用领域,其作用是将高稳低噪声的基准信号(例如100 MHz)通过一系列的倍频、分频和混频处理产生电子系统所需的特定频率信号[1]. 频率合成方式可以分为两种类型:直接频率合成(direct frequency synthesid,DS)和锁相频率合成(phase locked loop, PLL). DS又包含直接模拟频率合成(direct analog frequency synthesis, DAS)和直接数字频率合成(diect digital frequency synthesis, DDS),其优点是相位噪声最优,频率切换时间最短;缺点是体积和功耗开销巨大且很难实现超宽带. PLL利用鉴相器(phase detector, PD)的程控可变分频的优点,配合环路滤波器(loop filter, LF)和外置压控振荡器(voltage controlled oscillator, VCO)很容易实现宽频带、低杂散、低功耗和小型化,缺点是相位噪声水平较差. 由于频率源的相位噪声水平直接关系到雷达系统的多普勒特征提取[2],如何优化PLL的相位噪声水平成为国内外研究的热点. 文献[3]提出用光电振荡器来降低相位噪声,文献[4]提出用低噪声PD GM4704来降低相位噪声,文献[5]提出用蓝宝石振荡器来获得低相位噪声,文献[6]提出用低噪声锁相环LMK04806来获得低相位噪声,但这些文献均未达到DAS的理论相位噪声水平.

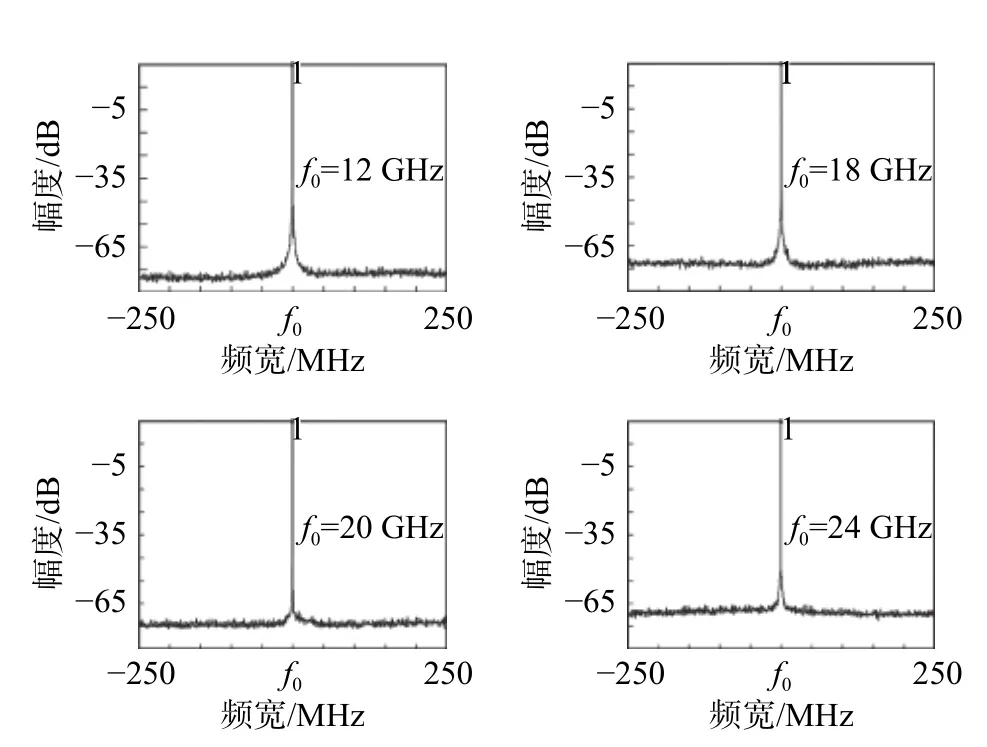

本文提出了一种联合DAS和PLL的混合合成方式,利用混频锁相实现超宽带和超低相位噪声. 设计了频率覆盖范围为12~24 GHz的频率综合器,其相位噪声指标在低频12 GHz处优于−116 dBc/Hz@1 kHz,在高频24 GHz处优于−109 dBc/Hz@1 kHz. 该混合频率合成方案达到的相位噪声指标水平与DAS方法相当,优于常规锁相方案20 dB以上.

1 混频锁相原理

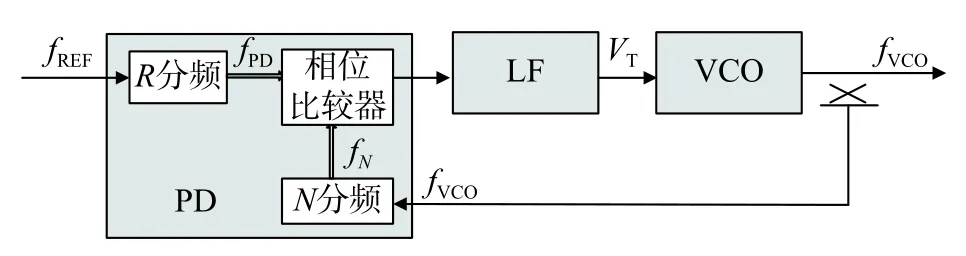

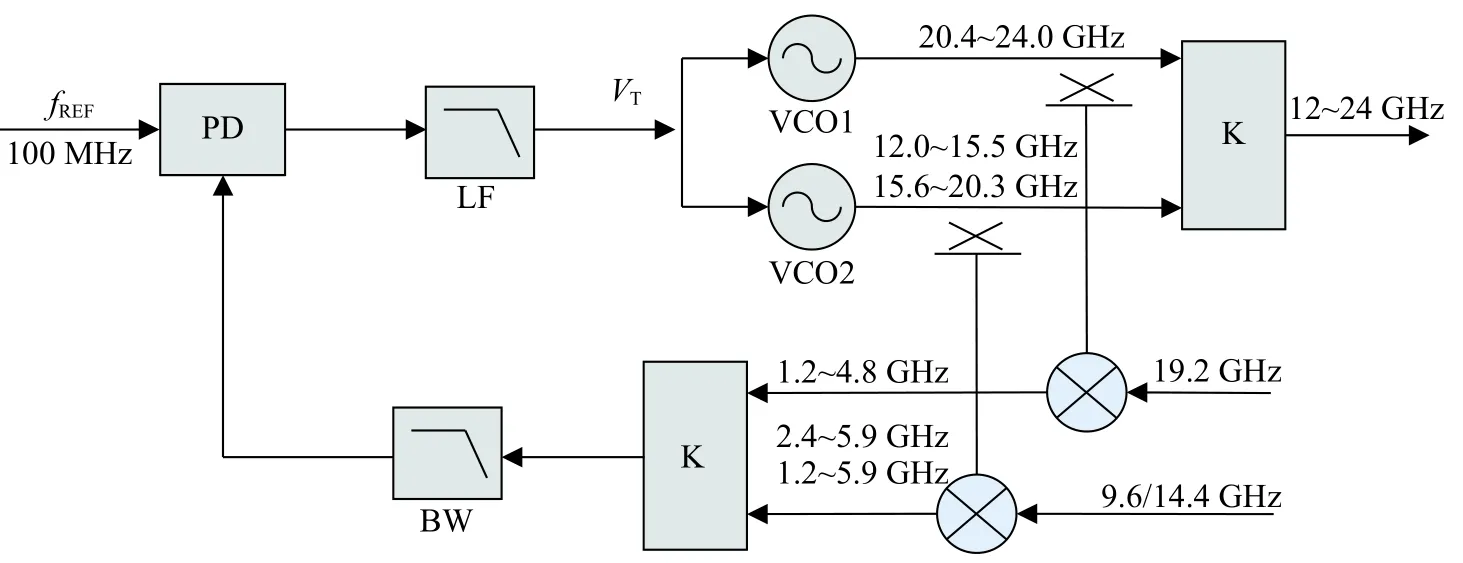

经典的PLL系统由PD、LF和VCO构成,如图1所示.

图1 锁相环结构原理图Fig. 1 Schematic structure of PLL

锁相环是一个负反馈的相位控制系统,PD内部的相位比较器对鉴相频率fPD(参考频率fREF经R分频器分频得到)和反馈频率fN(VCO频率fVCO经N分频器分频得到)进行相位比较,然后给出误差电压或电流经LF滤波处理后产生一个稳定电压VT来控制VCO的频率输出. 当环路进入锁定状态后,VCO输出频率与参考频率完全同步,即达到锁定条件:

式中:R为参考分频数;N为反馈分频数;fVCO为锁定输出频率;fREF为输入参考频率.

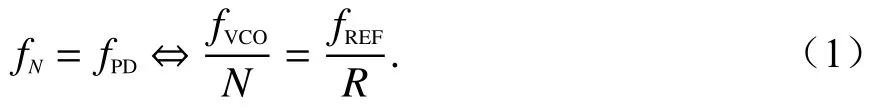

混频锁相环就是在传统锁相环路中插入一个混频器,利用偏移频率信号fRF将fVCO下混频至一个频率较低的中频fIF,然后进行鉴相比较,最终达到环路锁定. 混频锁相环的原理及其相位噪声传递模型如图2所示,图中BW表示中频低通滤波器.

图2 混频锁相环相位噪声叠加模型Fig. 2 Phase noise model of mixing PLL

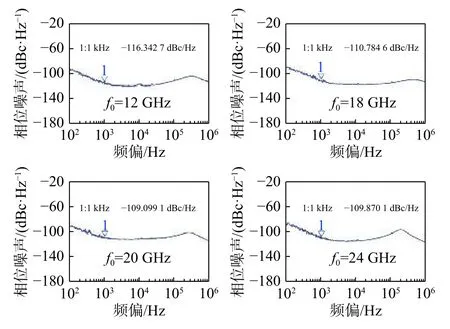

混频环锁定条件为

式中,fIF=|fVCO−fRF|.

对比式(1)和式(2)可以知道,混频锁相环中由于fRF的插入,相比于直接锁相环方案PD倍频次数由原来的fVCO/fPD减 小为 |fVCO−fRF|/fPD. 由于插入的偏移信号fRF可以通过DAS的方式产生,其相位噪声可以做到理论水平,根据混频相噪取差的原则,混频锁相环最终输出信号的相位噪声主要由PD倍频至中频信号fIF的相位噪声决定. 混频锁相环相位噪声按照线性模型传递,输出信号的相位噪声可以表示为[6-8]

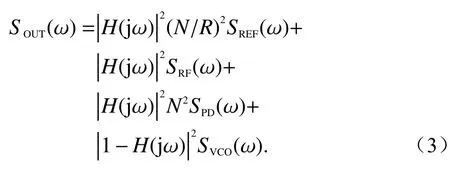

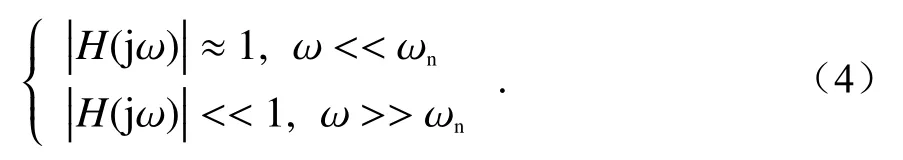

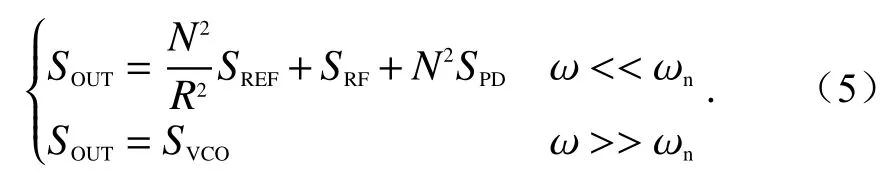

式中:H(jω)表 示环路的传递函数;ω表示角频率;SOUT(ω)表示输出信号相位噪声;SREF(ω)表示输入参考信号相位噪声;SRF(ω)表示偏移频率相位噪声,且满足SRF(ω)=M·SREF(ω),M表示倍频次数;SPD(ω)表示PD相位噪声;SVCO(ω)表示VCO相位噪声.

从式(3)可以看出,锁相环的相位噪声与输入参考信号相位噪声、PD相位噪声、LF、VCO相位噪声、输出频率(分频比R和N)相关. 由于LF通常采用的是有源比例积分电路,其传输特性接近于理想积分滤波器,可以近似为

式中,ωn表示环路带宽.

将式(4)带入式(3)可以得到

从式(5)可以看出,锁相环的相位噪声在环路带宽内主要取决于PD噪声基底和分频比,环路带宽外主要取决于VCO,在VCO选型确定的前提下,环路带宽外的相噪基本是确定的,这里不做详细讨论,本文主要讨论环路带宽内的相位噪声. 当VCO和LF确定时,参考信号的噪声通过环路倍乘,数字PD的本底噪声倍乘了N2,因此相比于单环锁相,混频锁相环采用低相噪的fRF频率作为插入偏移,可以降低PD的N值,即减小环路倍频次数,最终实现优化输出信号的相位噪声的目的.

2 频率综合器系统方案

基于混频锁相的超宽带频率合成器采用梳谱发生器激励低相位噪声的射频信号,经滤波后作为混频环的偏移频率信号进行混频,进而降低PD直接倍频次数.

2.1 频率综合器设计实现

2.1.1 偏移频率的产生

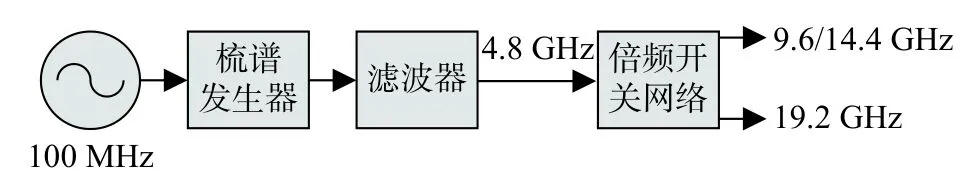

本文所述的超宽带频率综合器的频率范围为12~24 GHz,属于超宽带倍频程. 在偏移频率信号的设计上考虑多段拼接的方式. 偏移频率采用超低噪声梳谱发生器倍频产生,方案框图如图3所示.

图3 偏移频率产生方案框图Fig. 3 Schematic diagram of offset signal

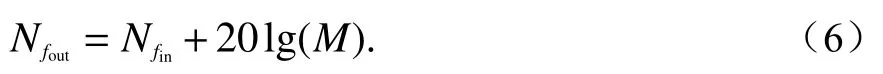

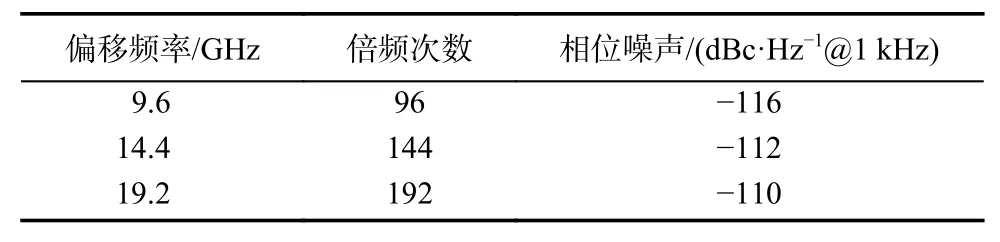

系统采用100 MHz低相噪的恒温晶振作为梳谱倍频基准,该晶振信号相位噪声指标优于−156 dBc/Hz@1 kHz. 经梳谱发生器倍频后再利用带通滤波器滤出4.8 GHz点频信号,然后利用倍频开关网络对该信号进行2倍频、3倍频和4倍频处理,得到三个偏移信号,频率分别为9.6 GHz、14.4 GHz和19.2 GHz.由于采用的梳谱发生器和倍频器为低相位噪声器件,最终输出的三个频偏信号的相位噪声可以通过倍频公式进行计算:

式中:Nfout表示输出信号相位噪声;Nfin表示输入信号相位噪声. 式(6)表示的相位噪声均为取对数后的dB单位.

根据式(6)计算得到的偏移频率信号相位噪声如表1所示.

表1 偏移频率相位噪声指标Tab. 1 Phase noise of the offset frequency

2.1.2 混频锁相环设计

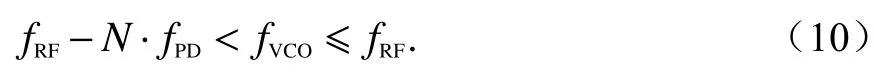

PLL方式通过VCO来实现宽频带覆盖. 由于目前市面上尚无直接覆盖12~24 GHz的VCO器件,本文选择两款ADI公司的VCO进行拼接:一款型号为HMC733LC4B,频率覆盖范围为10~20 GHz;另一款为HMC738LP4,频率覆盖范围为20~24.5 GHz.然后,利用射频开关切换合路最终输出完整的宽带频率信号. 混频锁相环的反馈支路采用偏移频率进行混频,混频后的中频信号经低通滤波后给PD鉴相,中频滤波器截止频率WFB=7 GHz(WFB为低通滤波器的带宽),混频锁相环的设计实现如图4所示,图中K表示射频开关.

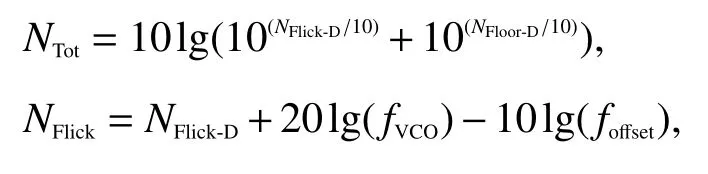

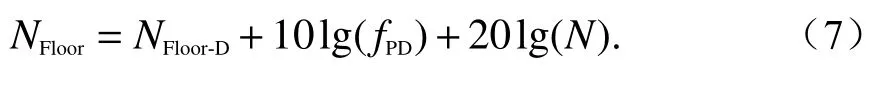

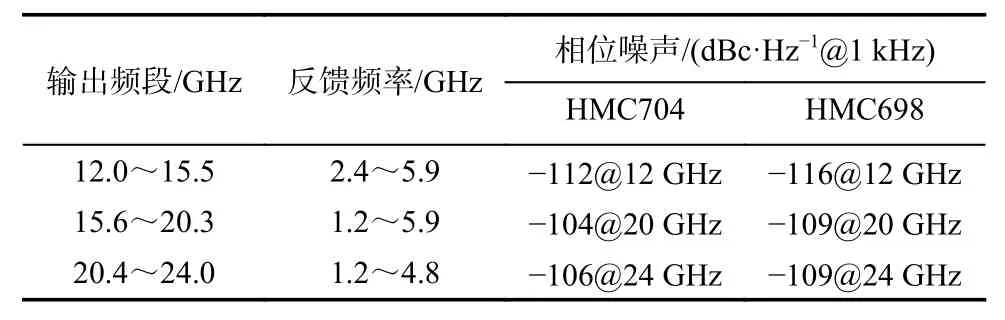

当偏移频率的相位噪声指标达到理论倍频水平时,PD噪底就决定了最终输出信号能达到的相位噪声指标水平[4]. PD主要分为数字PD和模拟PD两种,目前市面上数字PD噪底水平最优为ADI公司的HMC704芯片(国产器件对应型号为振芯电子的GM4704),相位噪声基底NFloor-D=−233 dBc/Hz,闪烁噪底NFlick-D=−270 dBc/Hz. 该类型PD相位噪声计算公式如下:

式中:NTot为最终输出信号相位噪声的对数表示;NFlick为闪烁噪声值的对数表示;NFloor为相位噪声值的对数表示.

图4 混频锁相环的设计实现Fig. 4 The design of mixing PLL

模拟PD的器件噪底差别不大,这里选择ADI公司的HMC698芯片进行计算,噪声基底NFloor-D=−145 dBc/Hz. 该类PD的相位噪声计算公式如下:

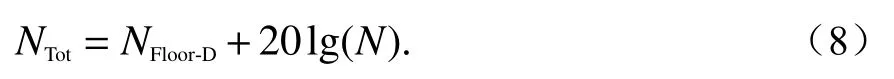

根据式(7)和式(8)可以分别计算两种类型PD对应混频环的鉴相中频信号的相位噪声,本文所述的12~24 GHz频率综合器频段设计和相位噪声指标理论计算统计如表2所示.

表2 频率综合器的相位噪声计算Tab. 2 The design of frequency-band and phase noise calculation of frequency synthesizer

从2.1.1节可知,最高偏移频率19.2 GHz相位噪声为−110 dBc/Hz@1 kHz,为了最大限度地发挥该信号的低相位噪声性能,选择中频相噪与之相比拟的模拟PD HMC698. 根据表2理论计算,最终输出信号相位噪声指标优于−109 dBc/Hz@1 kHz.

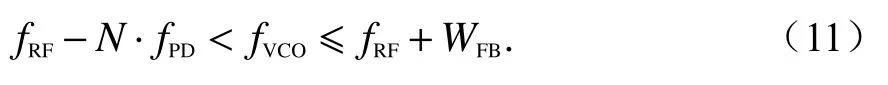

2.2 宽带混频锁相环防错锁设计

根据前文混频锁相环的原理分析以及式(2)可以知道,混频环锁定对应的fVCO频率有两个解,也就是混频器的上边带和下边带,这种现象也叫混频环的错锁. 窄带混频锁相可以通过窄带VCO型号的选择来避免fVCO频率同时出现上下边带的可能,而宽带混频环不可避免同时出现上下边带,因此解决错锁问题是宽带混频锁相的关键[7],下面首先分析宽带混频环的锁定条件.

混频锁相环正常锁定的条件为fIF=N·fPD,可以分为以下情况讨论.

Ⅰ当fVCO≥fRF时,可分为两种情况:

A 当N·fPD>fIF时,即N·fPD>fVCO–fRF,环路驱动VT↑→fVCO↑→fIF↑,使得fIF逐渐趋于fPD而进入锁定.

B 当N·fPD≤fIF时,即N·fPD≤fVCO–fRF,环路驱动VT↓→fVCO↓→fIF↓,使得fIF逐渐趋于fPD而进入锁定.

进一步的,在此情况下如果fVCO–fRF>WFB,将导致反馈频率fIF被滤掉而不能进入PD鉴相,最终导致混频环失锁,因此这种情况下混频环的捕捉带为

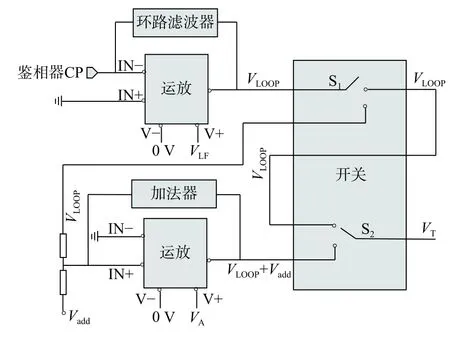

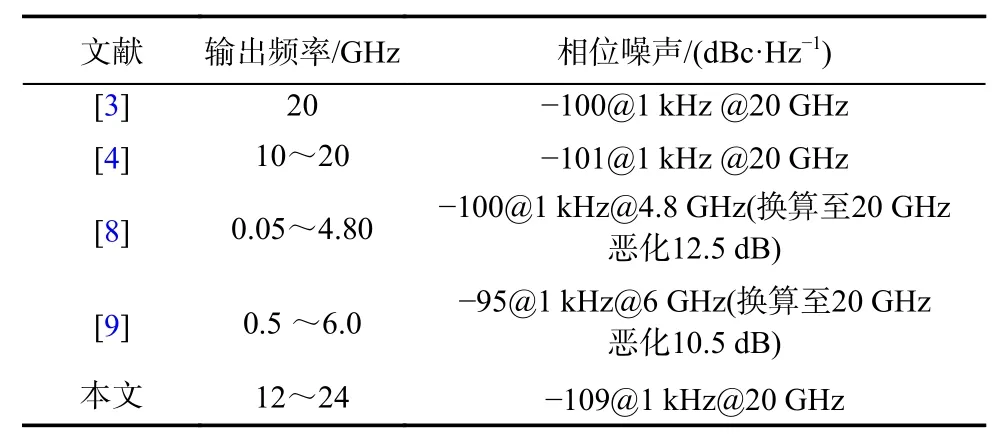

Ⅱ当fVCO A 当N·fPD>fIF时,即N·fPD>fRF–fVCO,环路驱动VT↑→fVCO↑→fIF↓,使得fIF越来越小,最终趋于0,然后进入Ⅰ-B状态,最终使得fIF逐 渐趋于fPD而进入锁定. B 当N·fPD≤fIF时,即N·fPD≤fRF–fVCO,环路驱动VT↓→fVCO↓→fIF↑,使得fIF越来越大,最终使得锁相环失锁. 所以此时混频环的捕捉带为 结合式(7)、(8)可以得到混频环的锁定条件为 由式(11)进一步可知,宽带混频锁相环必须采取防错锁设计使得环路拉低或拉高失锁时fVCO满 足式(11)限定的区间范围. 为了满足宽带混频锁相环的锁定要求,本文设计了如图5所示的防错锁电路. 采用加法器联合模拟开关环路切换的方式实现. 图中所示LF的运放高电压为VLF,环路输出电压为VLOOP;同相加法器的运放高电压为VA,加法器所加电压为Vadd,环路最终输出压控电压为VT. 下面通过图5分别讨论每个频段的防错锁设计实现. 图5 宽带混频锁相环防错锁电路Fig. 5 Anti-error lock circuit of broadband mixing PLL 当锁相环输出频段为12.0~15.5 GHz时,S1和S2模拟开关设置为直通,即满足0≤VT=VLOOP≤VLF;此频段偏移频率选择9.6 GHz,通过式(11)可以计算捕获范围为7.2 GHz 当锁相环输出频段为15.6~20.3 GHz时,S1和S2模拟开关将加法器切入环路,即Vadd≤VT=(VLOOP+Vadd)≤VA;该频段偏移频率选择为14.4 GHz,此时计算捕获范围为13.2 GHz 当锁相环输出频段为20.4~24.0 GHz时,S1和S2模拟开关也设置为直通,即满足0≤VT=VLOOP≤VLF;该频段偏移频率选择为19.2 GHz,此时捕获范围为18.0 GHz 通过以上加法器和开关电路设计,有效地解决了超宽带混频锁相环错锁问题. 按照前文设计对超宽带超低相位噪声频率综合器进行版图设计和加工,实物如图6所示.利用频谱分析仪和信号源分析仪对频率综合器 图6 频率综合器实物照片Fig. 6 Physical picture of frequency synthesizer 进行性能测试,图7所示为工作频段内四个频点12 GHz、18 GHz、20 GHz和24 GHz的频谱测试图,图中横纵f0表示对应的中心频率,纵轴表示幅度,可以看出该频率综合器杂散抑制优于80 dBc,频谱纯度非常高. 图8所示为频率综合器输出信号的相位噪声测试曲线,实测12 GHz信号相位噪声指标达到−116 dBc/Hz@1 kHz,20 GHz和24 GHz信号相位噪声指标为−109 dBc/Hz@1 kHz,与理论计算值一致. 图7 不同中心频率频谱测试图Fig. 7 Spectrum test diagram of frequency synthesizer 图8 不同中心频率相位噪声测试曲线Fig. 8 Phase noise test diagram of frequency synthesizer 表3所示为本文与相关文献报道的频率综合器输出频率和对应相位噪声指标的对比,可以看出:相同输出频率20 GHz相位噪声对比,文献[3]和[4]指标相当,为−100 dBc/Hz@1 kHz左右,比本文所达到的指标−109 dBc/Hz@1 kHz差8~9 dB;文献[8]为传统单环锁相方案,文献[9]为经典传统锁相器ADF-4106,通过式(6)理论换算至本文输出频率20 GHz,相位噪声相比于本文差20 dB以上. 表3 相关文献报道的指标对比Tab. 3 The performance comparison of other literatures and this paper 超宽带和超低相位噪声是频率综合器发展的重要方向,本文采用DAS方法产生低相位噪声的偏移频率插入环内混频,实现了12~24 GHz超宽带频率输出. 经实验测试表明:该混频锁相方案具有与DAS相当的相位噪声性能. 在低频段12 GHz处实现相位噪声优于−116 dBc/Hz@1 kHz,高频段24 GHz处相位噪声优于−109 dBc/Hz@1 kHz,均优于统锁相方案20 dB以上. 该频率合成方法克服了单一的DS频带窄的劣势,弥补了单一的锁相方法相位噪声指标差的缺陷,解决了超宽带混频锁相的错锁问题,具有较好的应用前景.

2.3 性能测试及分析

3 结 论