一种1394总线事务层功能验证关键技术研究

魏美荣,田 泽,3,王世中,王宣明

(1.航空工业西安航空计算技术研究所,陕西 西安 710068;2.西安翔腾微电子科技有限公司,陕西 西安 710068;3.集成电路与微系统设计航空科技重点实验室,陕西 西安 710068)

0 引 言

1394总线具有高带宽、低延迟和高可靠等特点,很好地满足了航空电子系统的应用需求,支持异步传输和等时传输方式,其中事务层支持异步传输读取、写入、锁定操作的CSR结构请求、响应,等时传输由应用程序直接驱动[1]。

随着可编程逻辑器件的广泛应用以及用户对产品质量要求的提高,传统的仿真验证已难以满足日益增长的可编程逻辑器件验证需求[2]。研究表明,越是高层次的验证效率越高,越是低层次的验证则准确性越高[3]。UVM通用验证方法学已经成为芯片验证行业最新的验证标准[4],基于系统级硬件描述语言SystemVerilog,具备面向对象编程的思想和功能[5-7],主要对结构相似的DUT(device under test)进行验证。由于其具有面向编程语言的特点[8-10],可以将很多方法和函数封装成不同的库类使用,通过接口的形式将待测模块与验证平台连接起来并且具有良好的可重用性[11]。

为有效模拟1394总线协议实现过程中软硬件模型交互在宿主机上复杂的工作场景,文中以该芯片中的事务层功能验证作为主要分析对象,对其验证过程中数据处理关键技术进行研究,给出一种基于UVM的1394总线SoC芯片事务层协议处理功能验证的解决方案。通过采用基于UVM的验证分层结构,重点研究软件程序和硬件组件激励程序的执行效率和软硬件验证程序运行中占的比重,提取一套通用性强的软硬件交互机制。该方案中采用软硬件结合的方式可以简化系统,提高系统的可靠性及性能,其中硬件部分能够保证更加准确地使用预定义的网络带宽和预定义的帧周期,软件又可以灵活地去操纵通信过程中的接收和发送,有效实现1394协议。

1 虚拟验证策划

文中提到的1394总线SoC芯片是目前国内自研的首款集成了军用1394协议、链路层协议、物理层协议以及嵌入式处理器的芯片,其设计复杂度高,不但对设计本身满足复杂的功能和较高的性能提出要求,更对系统中软硬件划分、验证和测试带来巨大挑战。文中在对1394总线SoC事物层系统功能进行分析的基础上,制定了相应的验证策略与方法,并详细介绍了虚拟验证平台组件和工作原理。

1.1 系统功能分析

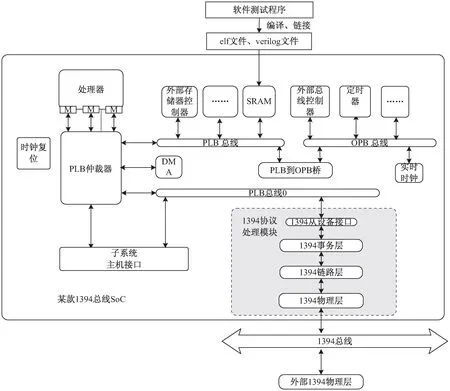

图1是1394总线SoC芯片体系架构,是一款集成了嵌入式处理器、PCI主机接口、JTAG接口、SDRAM控制器、外部总线控制器(EBC)、直接存储器访问控制器(DMA)、1394总线协议事务层、1394链路层、1394物理层、通用输入输出接口(GPIO)等资源的片上系统,还包含PLB总线和OPB总线两种总线。可实现1394总线协议处理、以太网协议栈解析以及文件系统管理等功能,具备智能化、通用化、小型化的优点。文中重点对1394总线事务层协议处理功能特点进行分析,主要包含:

图1 1394总线SoC芯片体系架构

(a)处理器验证软件主要功能:初始化SoC内部设备、按照不同工作场景对各相关设备进行配置、通过简单运算产生激励、处理各种事件中断,对芯片内部状态、数据进行判断比较,打印各种信息;

(b)外部硬件验证组件主要功能:通过软硬件交互实现寄存器/存储器访问,利用随机约束产生满足1394协议通信事务数据包,并对收发数据包完成数据有效性检查;

(c)1394事务层功能:支持PLB总线接口,访问数据缓冲区DPRAM支持单拍和多拍操作;支持在不同数据传输速率S100B、S200B、S400B下,异步和等时传输模式数据通信机制;支持IEEE1394协议约定的异步包、等时/异步流包、物理层等数据包的收发等。

1.2 验证策略与方法

通过上述的系统功能分析,文中采用当前主流的UVM验证方法学搭建系统验证架构,并制定出一套通用性强的1394总线协议处理的软硬件交互虚拟验证方法。改善以往由处理器软件负责的数据运算等大量占用仿真时间的任务,交给SystemVerilog语言搭建的硬件验证组件去完成。而处理器软件在虚拟验证过程中只负责记录一些简单的状态报告、寄存器配置等操作,由此提高处理器运行效率。文中阐述的虚拟验证平台组件具体描述如下:

1.2.1 虚拟验证平台组件

虚拟验证平台组件中的软硬件控制信息交互区、数据交互区,具体描述如下:

(a)软硬件控制信息交互区。

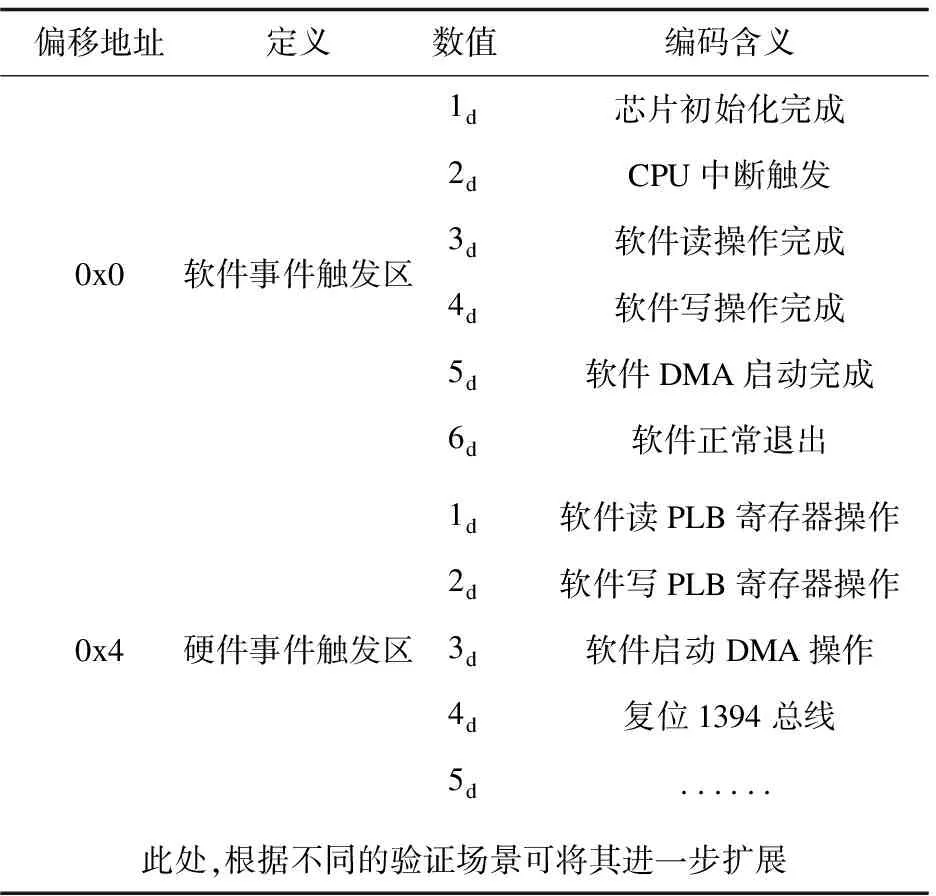

在整个SoC芯片虚拟验证过程中,该交互区为处理器软件和硬件验证组件之间提供交互的控制状态和数据交换区域,并存储当前SoC的内部状态信息。硬件验证组件根据交互区偏移地址的数值,依照事先定义好的编码含义驱动软件对芯内部各设备进行配置,当软件配置完成之后,并在软件事件触发区填写相应值,供硬件验证组件进行查询。最后,由硬件验证组件来进行状态的判断、数据运算,以此确定处理器软件的下一步操作。其中,软件通过EBC特定地址范围来访问该区,硬件验证组件是通过存储器的后门接口来访问信息交互区的,软硬件交互在EBC上的存储地址范围2’hD800_0000~32’hDFFF_FFFF,具体定义如表1所示。

表1 软硬件控制信息交互区定义

(b)数据交互区。

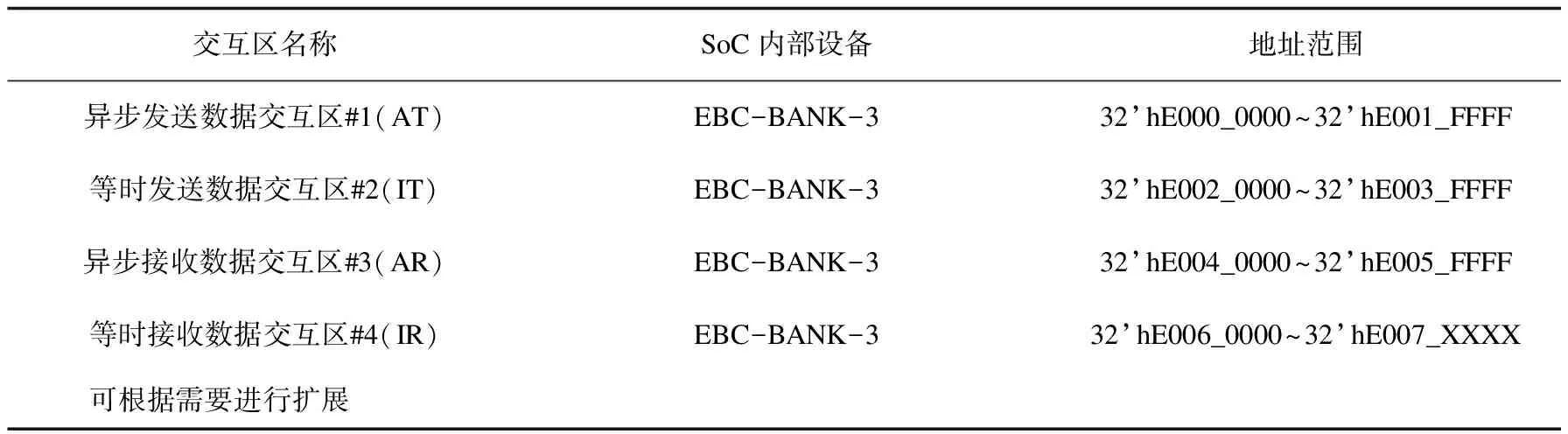

数据交互区用于存储硬件验证组件产生的待发送的数据包和总线节点间通信接收到的数据包,该交互区存储的数据类型包括异步发送数据交互区#1(AT)、等时发送数据交互区#2(IT)、异步接收数据交互区#3(AR)和等时接收数据交互区#4(IR)。处理器软件和硬件验证组件均可访问此区域,文中数据交互区容量设计为128 MB,根据不同的验证场景可将其进一步细分,其访问地址如表2所示。

表2 数据交互区的地址分配

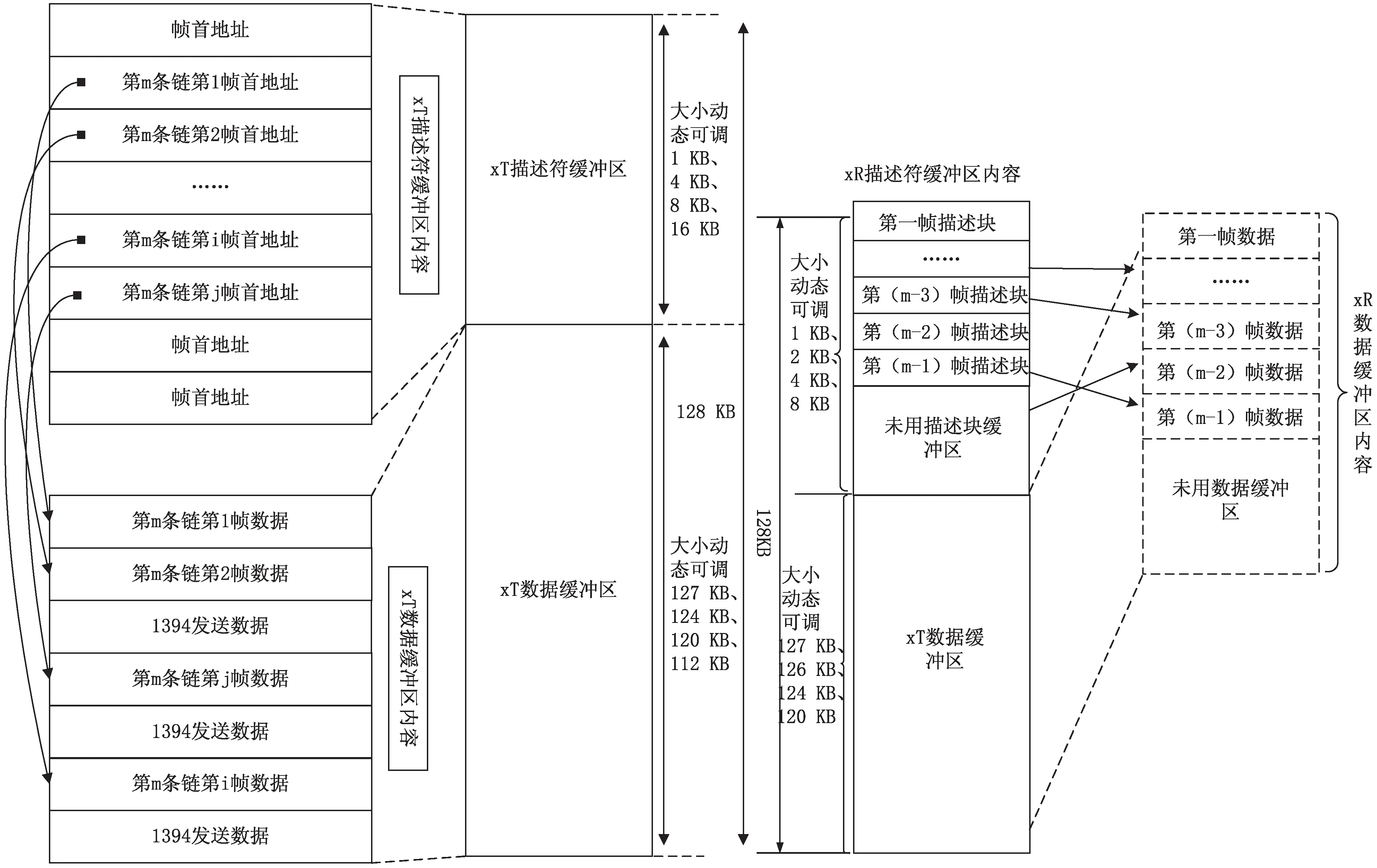

数据交互区#1、#2、#3和#4分别是映射SoC内部事务层的内部异步发送(AT)、等时发送(IT)异步接收(AR)、等时接收(IR)缓冲区。除了基地址不一致,其他所有信息保持一致。数据交互区#1、#2、#3、#4的存储结构如图2所示。

图2 数据交互区xT和xR数据结构

在虚拟验证过程中,数据交互区#1、#2内部的空间划分、数据填写完全由硬件验证组件管理;处理器软件只是负责把数据交互区#1、#2的内容复制到事务层内部异步发送(AT)、等时发送(IT)缓冲区对应位置上,不对数据交互区#1、#2进行任何写操作。

1.2.2 工作原理

虚拟验证平台运行过程中,软硬件交互机制工作过程如下:

(a)软件触发硬件机制:软件根据表1的内容对信息交互区偏移地址为0x0的位置进行相应写操作,硬件功能模型检测到不同的写操作之后,触发相应的事件;

(b)硬件触发软件机制:硬件验证组件根据表1的内容对信息交互区偏移地址为0x4的位置进行写操作,然后触发外部中断。当软件检测到外部中断后,读取信息交互区偏移地址为0x4的数据,根据译码含义进行相应的软件操作;

(c)虚拟验证平台的定时机制,利用SoC内部定时时钟和硬件验证组件的事件函数进行计时。

具体1394总线SoC协议处理事务层系统级发送和接收机制如图3所示。

图3 1394总线事务层发送和接收数据包机制

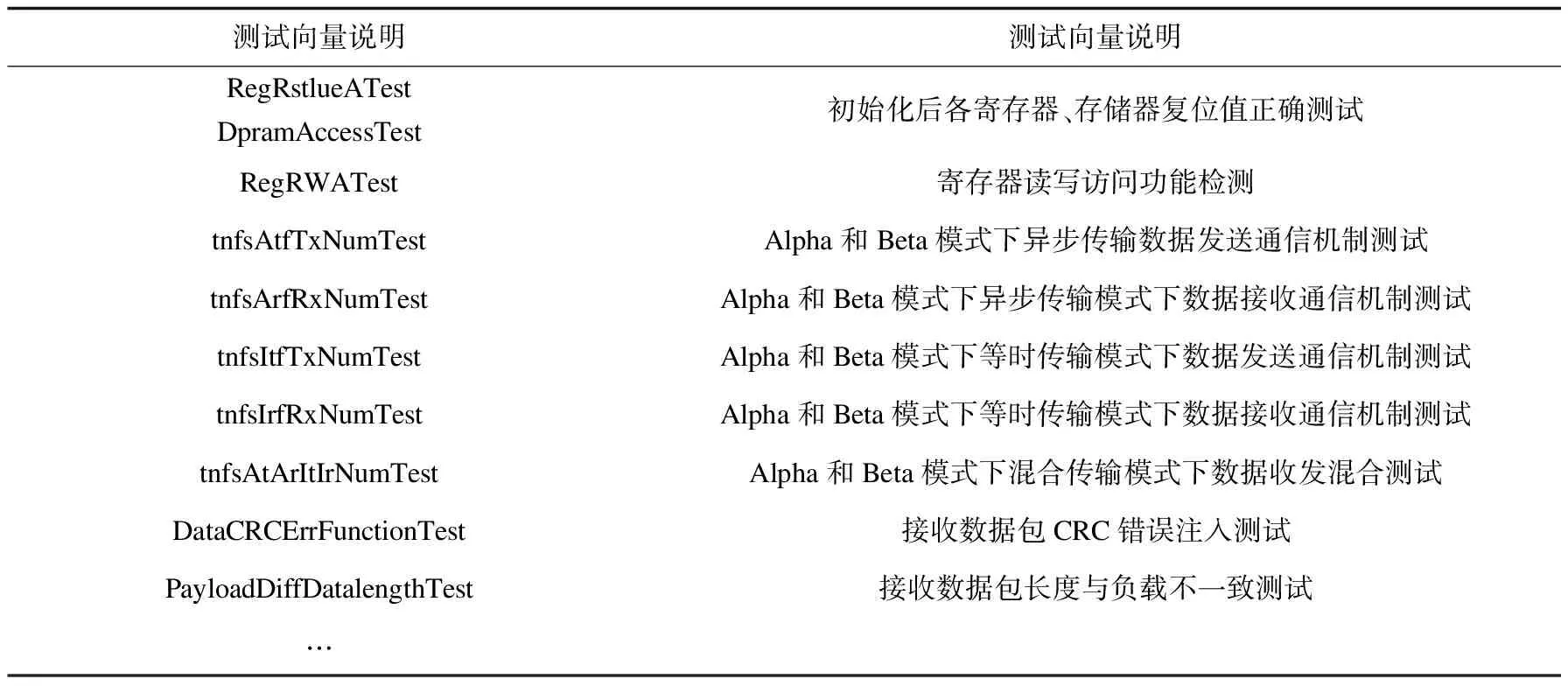

根据1394总线SoC事务层的功能特点设计的系统级部分主要测试用例如表3所示。

表3 测试向量

其中,针对寄存器测试在平台中搭建扩展uvm_reg的寄存器模型来模拟主机读写行为,根据每个寄存的名称、地址、读写属性、复位值等信息生成register map,测试test中实现reg_model.regName.read(stautus,rddata)和reg_model.regName(stautus,wrdata)的形式进行后门直接访问,不占用仿真时间,不仅可以避开总线、减少波形上显示,还能加快仿真速度。

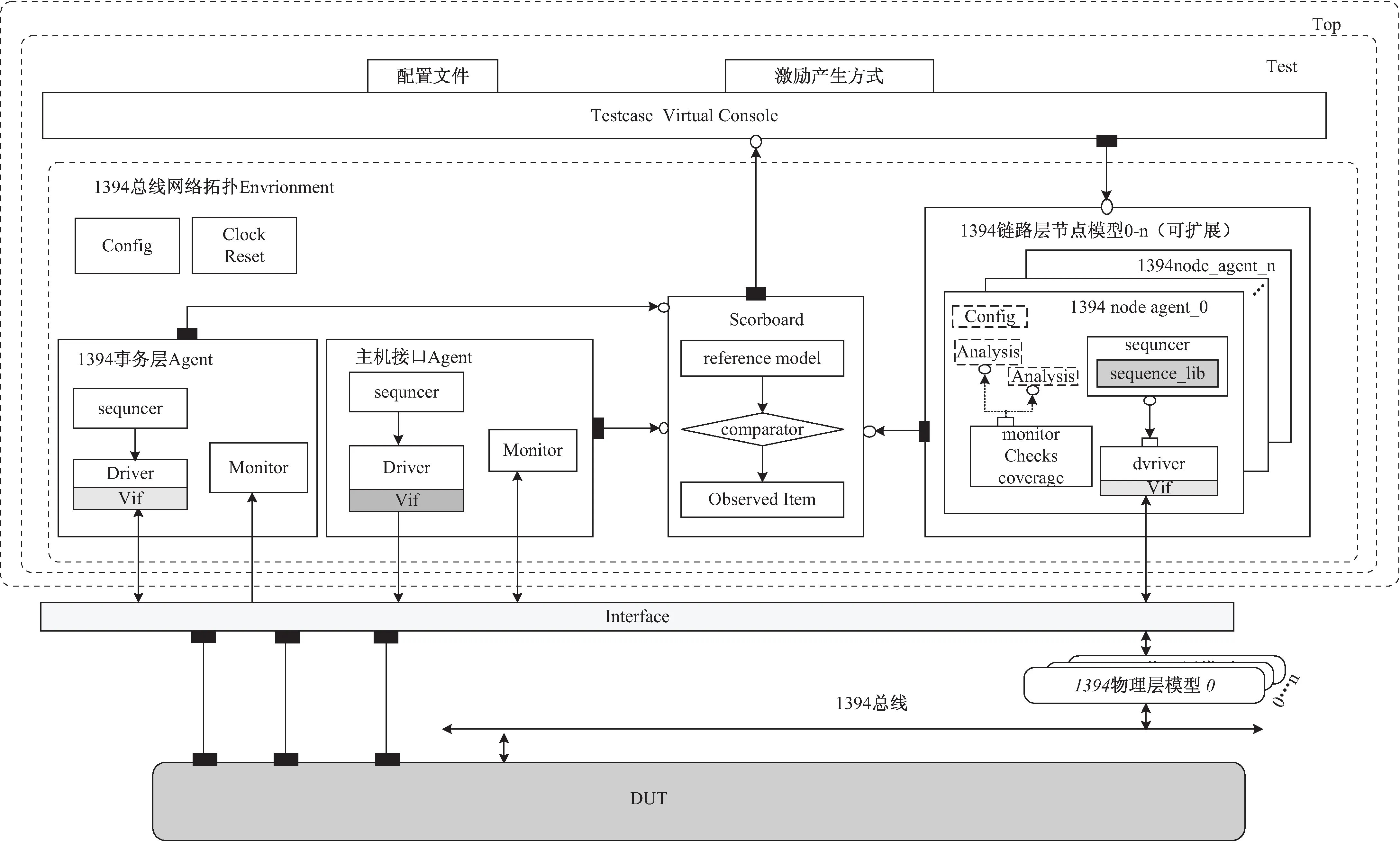

2 基于UVM的验证平台设计

根据上节1394总线SoC协议处理芯片的验证策略与工作原理,采用UVM高级验证方法搭建了虚拟验证平台,如图4所示。

图4 基于UVM的1394总线SoC验证平台设计

其中,1394总线SoC芯片的RTL作为DUT与验证环境通过接口相互连接,测试平台包括环境配置组件、激励产生、事务层agent、主机接口模型agent,1394总线链路节点UVC和计分板(Scoreboard)驱动器等UVM验证组件,其构成的1394总线网络拓扑环境能够很好模拟1394总线请求节点主机驱动、1394总线响应节点的信号输入输出以及对DUT总线接口时序监控和信号采样的完整性功能。整个验证环境是由采用了面向对象的技术,通过类的继承和多态性定义验证组件和激励数据,在testcase对象的创建过程中实例化不同的验证环境,即实现了不同的testcase需要不同的验证场景的要求,激励是在仿真运行期间动态产生,数据生命周期结束后自动释放内存空间。每一个testcase都是由主机接口模型、收发帧模型、验证激励库等几部分组成,并通过UVM_sequence_item类将不同的数据信息封装进不同packet包,并向不同的agent中的sequencer发送transaction进行测试。transaction是基于事务级的数据,经过driver将数据按特定的协议和时序关系进行转换,DUT输出端的时序级信号通过monitor进行采集、解析并转换为事务级数据递给Scoreboard进行比较,如果错误则会打印UVM_ERROR信息,从而验证不同功能的正确性。验证环境与被测试对象是通过interface相连接,此外激励和平台结构分离、验证组件间采用TLM标准接口,使整个平台具有灵活配置、可重用、可扩展升级等优点,其主要验证组件功能如下:

(a)主机接口Agent:实现处理器验证软件驱动层的功能,实现对“信息交互区”软硬件事件触发区寄存器读写操作,同时把事物层响应的信息转化为硬件接口上的信号时序驱动,同时把硬件接口上数据状态反馈给事物层;

(b)1394事务层Agent:实现“外部硬件验证组件”和“1394总线事务层功能”相应关事务操作激励,通过评估DUT的特性,确定data_item应用的属性、约束、task和function,继承uvc_sequence_item,达到描述事务级的功能属性,并将1394总线节点通信过程的状态信息传递给主机接口模型和记分板;

(c)1394总线链路节点UVC:实现1394总线节点链路层的功能,和物理层功能模型连接,模拟1394总线上的拓扑结构,并且提供链路层功能行为、处理网络上传递过来的各种请求事务响应处理和统计,同时把内容结果传递给计分板进行比较分析;

(d)计分板(Scoreboard):DUT输出端处理过的时序级信号通过主机接口模型agent、事务层agent和1394总线链路节点UVC的monitor进行采集和解析,将时序信号转换为事务级数据传递给计分板,计分板将这些信息与预先期望的参考模型进行比较,从而验证不同功能的正确性,以通过生成的log文件中的报告及断言来检测DUT的正确性[12-13]。

3 验证结果及分析

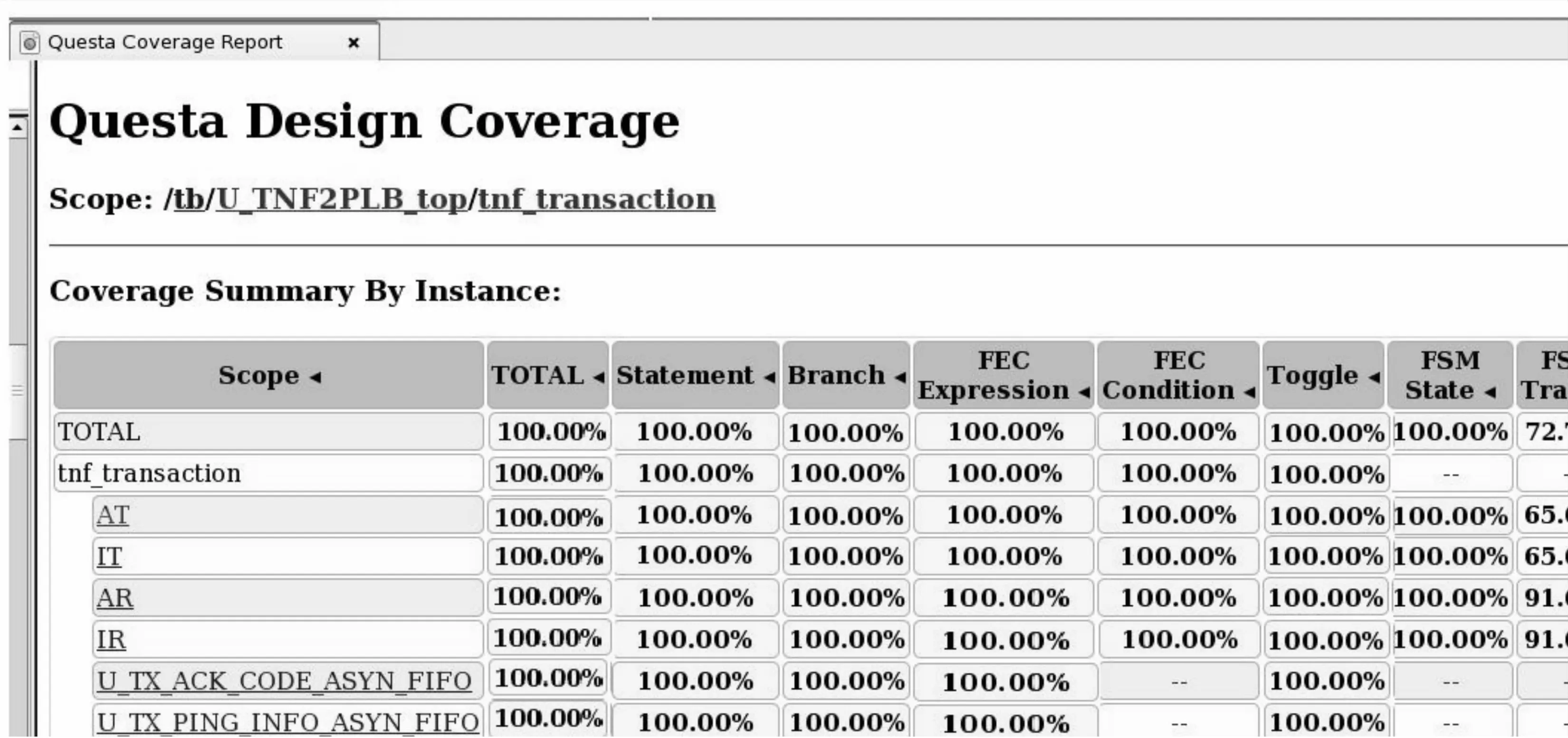

文中采用Linux运行环境QuestaSim10.2c功能仿真环境,通过SystemVerilog、Makefile编程语言及脚本语言,将编译、仿真、测试选择、覆盖率收集等功能设计为自动化流程。以AT和AR通信测试向量仿真结果为例,运行UVM仿真平台,得到的仿真结果波形如图5所示。由VCS仿真的结果可知,当异步通信事务过程发送包和接收包个数分别是57和79,将所有测试向量测试完毕后,进行回归测试并进行覆盖率统计,将输出结果进行打印,如图6所示,整体覆盖率已达到100%,满足上述表3系统级规划的测试功能需求,说明该模块已通过设计验证,达到了预期验证目标。

图6 覆盖率报告

4 结束语

文中通过对1394总线SoC系统功能进行分析,在保证1394效率的基础上,提出一种基于UVM的1394总线事物层软硬件协同验证方案,并制定出详细的虚拟验证策略与方法,搭建基于UVM的分层结构验证平台,给出具体工作原理。最后通过实际仿真测试和覆盖率收集分析可知,该方案不仅有效满足了系统级验证总体需求,灵活完成1394协议解析,提高了验证效率,增强了系统通用性,还具有易维护、可重用、高效率、灵活等特点。