模块化中频信号源设计

李映晟,严厚伟,杜 睿

(中国船舶重工集团公司第七二三研究所,江苏 扬州 225001)

0 引言

高速电路调试时,经常需要接入多路时钟信号和中频信号。要搭建这样的调试工装,需要多台信号源或者相关仪器,同时调试高速电路往往需要较为高端的大型台式仪器,导致工装显得较为臃肿。如果进一步搭建自动测试系统,可能还需要特定型号或者品牌的仪器,多台贵重仪器的同时使用,给整个单位或实验室内的仪器调配带来很大的困难。如果能够自研一台小型模块化仪表,不仅能够简化工装搭建,还能缓解仪表紧缺的情况[1]。

1 设计要求

本文以集成高速ADC/DAC 的电路为研究对象,研制一台小型模块化信号源。根据当前测试需求,自制模块化信号源需要输出两路不高于2.8 GHz的时钟点频,杂散优于-60 dBc,功率大于-2 dB,单点偏差±5 kHz;以及一路150 MHz~850 MHz 可调中频,杂散优于-45 dBc,功率-2 dBm~-8 dBm,频率精度优于200 Hz。信号源在满足指标要求的同时,需要尽量缩减体积。

2 方案设计

2.1 方案选择

信号源设计方案一般有3 种实现方式:

第1 种,使用模拟电路搭建信号源,是利用分立器件构成振荡回路,使其产生自激振荡,输出信号。但是该方案易受外界因素影响,不够稳定。

第2 种,使用锁相环(PLL)产生信号的方案。亦可称为间接频率合成。该方案的信号源,可以在很宽的频谱范围内产生信号,有很好的杂散抑制能力,但是频率切换速度较慢,并且不能达到较高的分辨率[2-3]。

第3 种,直接数字频率合成(DDFS)方案。当前常用的实现方法是使用DDS 和DAC 芯片搭配MCU 或者FPGA。随着高性能芯片不断出现,两种方案已经没有太大的差别,DDS 芯片方案能够节约成本和研发时间;DAC 方案精度更高,能输出纯度更高的谱型[4]。

根据以上分析,结合设计要求,时钟信号采用基于锁相环的方案,以得到频带内信号保真度更高,相位噪声更好的时钟信号。本文设计的信号源、后续可能在其他项目使用,所以需要具有通用性,中频输出路采用DAC+FPGA 方案更加符合要求[5]。

2.2 整体设计

该信号源选用4U 小型仪表机箱,机箱内可装入9 个宽度为6HP(约3 cm)的模块,如图1 所示。机箱中的每个模块由标准3U 的信号产生板和6HP 面板组成。信号产生板上集成了DAC、PLL、FPGA、LAN 协议芯片、RS-232 芯片、总线协议芯片等。根据实际使用情况,预留7 路模块安装槽。每个模块拥有两路输出:一路时钟,一路中频输出。使用时,同一个模块只能输出时钟或中频信号其中一种,可以根据使用情况进行调节,选择需要的输出。机箱内包含一块母板和一路220 V 转5 V 和12 V的电源。箱体背部留有LAN 和RS-232 的插座以及220 V 电源输入口。

图1 结构设计

3 信号产生板设计

3.1 设计方案

信号产生板上的时钟信号由PLL 产生,中频信号由FPGA 控制DAC 产生。根据小型化设计的要求,模块采用内置VCO 的小型片上PLL——ADF4355,输出频率范围为3.4 GHz~6.8 GHz,可进行最高64 分频[6]。DAC 采用14 位芯片AD9739,采样率最高达2.5GSPS[7]。ADF4355 有两路输出,可以通过FPGA 打开和关闭。为了达到小型化、独立模块化设计的要求,该DAC 无外部时钟输入,采用片上PLL 的其中一路输出作为时钟信号。模块功能设定为输出中频信号时,PLL 产生的一路输出会直接接入DAC;当模块功能设定为输出时钟信号时,DAC进入休眠模式,PLL 的另一路信号直接对外输出。中频信号的输出频率,可以通过LAN 或者RS-232 由测试软件界面更改。图2 为信号产生板布局示意图。

图2 信号产生板布局示意图

3.2 PLL 与DAC 直连的应用

信号产生板采用小型3U 标准,根据设计要求,需要具有产生高质量中频信号和时钟信号的能力。由于印制板面积限制,信号产生板上PLL 与DAC间不使用时钟缓冲芯片。

PLL 和DAC 间采用直连方式提供时钟,需要考虑PLL 输出时钟的摆幅,是否符合DAC 时钟输入的要求。

图3 为ADF4355 在理想状态下的输出功率和频谱关系。AD9739 芯片所要求的差分时钟输入摆幅Vpp范围为1.2 V~1.8 V,最低摆幅需求为1.2 V。PLL 和DAC 间的接口为50 Ω。

图3 AD4355 输出频率与最大功率关系

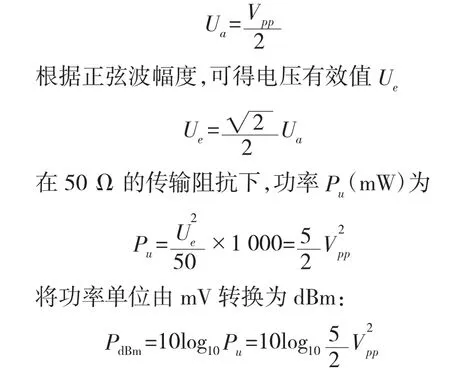

ADF4355 输出为正弦波信号,正弦波峰值为有效值的倍。峰峰值为2 倍的峰值。正弦波信号其幅度应为Ua

当Vpp=1.2 V 时,对应的PdBm≈5.563 dBm。

由图3 可知,ADF4355 的输出频率约为2.1 GHz时,器件输出功率接近5.563 dBm。该功率、频率关系图中的功率值,是取自官方的评估板,考虑到实际设计时很难达到这种近乎理想的状态,同时为了提高输出信号质量,需要对系统进行降频[8]。根据奈奎斯特采样定律,输出最大频率fmax与采样时钟最大频率fsmax的关系:系统中DAC 输出最大中频频率为fmax=850 MHz,要满足要求,fsmax≥1.7 GHz,本设计中fsmax取1.7 GHz,此时根据上式计算Vpp≈1.3 V,符合设计要求。

3.3 FPGA 选型

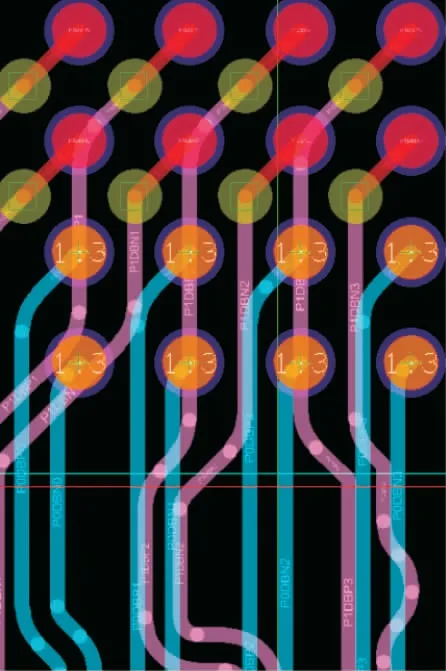

AD9739 与FPGA 之间的接口预计需要使用30对LVDS,其他通信及总线接口预计使用约100 个管脚。由于FPGA 不允许LVDS 信号定义到不同BANK,所以选取的FPGA 中需要至少有两个BANK有14 对LVDS。

AD9739 采用双通道数据传输,可将传输速率降为DACLK 的二分之一。同时数据采集采用一个时钟周期内采样两次的DDR 模式,传输速率还可再降低一半。即AD9739 与FPGA 间实际传输速率为四分之一的DACLK,为425 MHz[9]。综合考虑了器件布局、印制板尺寸及开发成本等,这里选用Intel 公司的EP3SE110F1152I3。

3.4 阻抗层叠设计

板上集成多种类型芯片,电源电压种类也较多,同时多种电压需要模数分开,所以印制板布局要求较高。考虑到成本和制作周期,板材采用性能与FR-4 接近的IT-180A,10 层的层叠设计,分为2个电源层,4 个地层,2 个信号层。阻抗方面,各层的单端信号采用50 Ω 阻抗、差分信号采用100 Ω 阻抗设计。可以根据下式计算得出各层线宽:

式中,Er为板材介电常数,H 为参考平面距离,T 为铜皮厚度。表1 为计算得出的各层线宽。

表1 阻抗线宽结果

使用仿真软件SI 9000 进行仿真后,经过调整,导入相关阻抗、叠层信息,如图4 所示。

图4 阻抗叠层仿真

3.5 电源设计

信号产生板上共有两个电源输入,一路输入5 V,一路输入12 V。其中,5 V 输入电压隔直后,分别送给两片双路8A 的稳压芯片LTM4616。整板电源分布如图5 所示。

图5 电源分布图

两片LTM4616 通过调节反馈电阻,分别产生1.1 V、3.3 V、2.5 V 和4 V,其中,3.3 V 供大部分芯片使用,1.1 V 为FPGA 核电压;2.5 V 输出后分为两路,一路为FPGA 的IO 电压,一路供给下一级直流稳压器LT1764-ADJ;产生的4 V 供给下一级稳压器LT1764-3.3 进行二次降压稳压。

LT1764 是最大电流3A 的快速瞬态响应低压差稳压器。由于AD9739 和ADF4355 的供电电压中,3.3 V 和1.8 V 都需要分为数字和模拟电压输入,所以LT1764-3.3 的输出通过电感分成数字和模拟两路。LT1764-ADJ 的电压调节为1.8 V,也分为模拟和数字两路。

ADM7150 适用于为电源敏感的RF 器件提供高质量电源,板上输入的12 V 经过隔直滤波后分为两路,一路经ADM7150-5.0 降压后变为5 V,供给需求5 V 的电路,包括总线协议芯片、RS-232 协议芯片和ADF4355 的模拟电压输入。一路经另一片ADM7150-5.0 降压后变为5 V,单独作为ADF4355的数字5V 电源输入。

3.6 DAC 设计

AD9739 与FPGA 接口主要为:数据总线DB0和DB1;用于读写寄存器状态的SPI;数据同步时钟DCI 和DCO。

DB0 和DB1 是高速数据位,该处设计直接影响印制板性能。这里采用带状线的设计。DB0[13..0]通过盲孔扇出到第3 层,DB1[13..0]通过过孔到第7层,两组数据线阻抗路径一致,仿真结果如图6 所示。

图6 DCI、DCO 的约束仿真

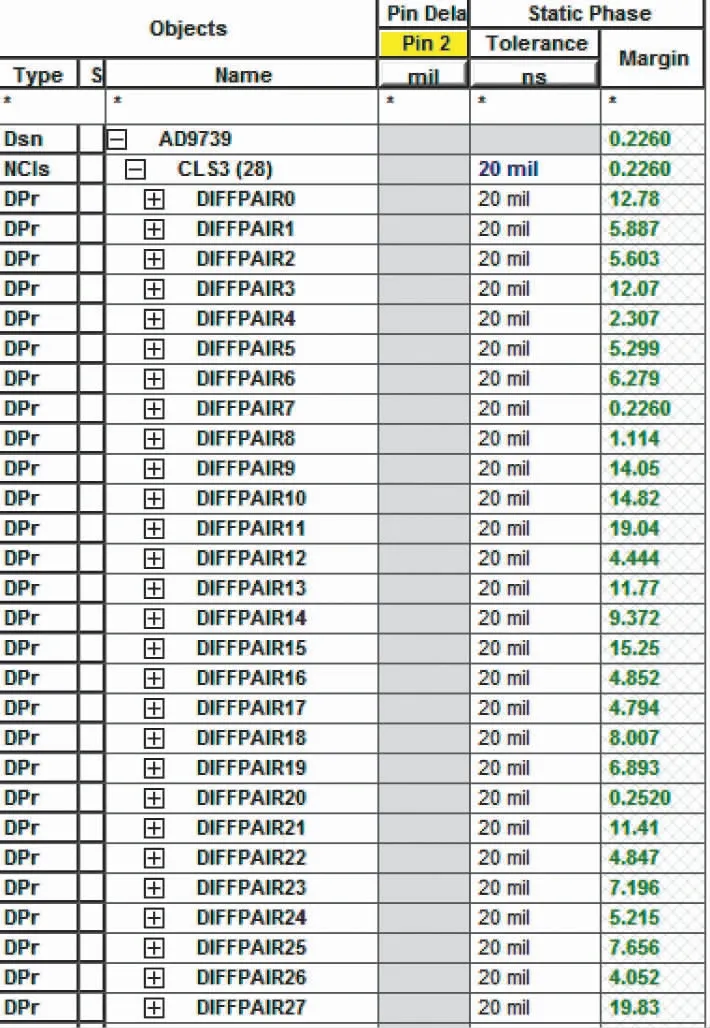

在PCB 设计约束设定中,两组共28 对信号,彼此线对间差值最大20 mil,每对信号内两线等长,差分对之间传输延迟误差保证在400 ps 内。同时如图7 所示,使用蛇形走线,最大程度保证信号完整性。

图7 AD9739 局部扇出

3.7 PLL 设计

ADF4355 与EP3SE110 通过SPI 通信,其他接口包括复位、使能、片选等。ADF4355 有两路相同的差分输出RFOUTA和RFOUTB。本文的设计中,RFOUTA的输出经变压器转为单端信号后,作为信号产生板的对外时钟信号输出。RFOUTB与AD9739 的时钟输入端口相连,作为AD9739 的输入时钟。图8 为ADF4355管脚连接示意图。

图8 ADF4355 管脚连接示意图

3.8 接口设计

信号产生板的对外接口有:网络、串口、并口。

网络通信通过集成全硬件TCP/IP 协议的网络控制器W5100 实现。W5100 使用SPI 与FPGA 之间进行数据传输,有效简化网络通信部分的设计[10]。W5100 的内外电路结构如图9 所示。

图9 W5100 结构图

RS-232 协议芯片采用MAX3232,预留了两路RS-232。信号产生板的对外总线接口,预留给测试和以后功能升级使用,共有48 输入输出。总线协议芯片为SN74LVCC245,输入输出的方向由FPGA 控制。

4 测试与分析

使用频谱仪对信号产生板的中频信号进行测量,如图10 所示。信号输出功率在150 MHz 时为-2.01dBm,临界最大值,测试是在相对理想状态进行,实际使用时会有其他因素影响,所以该指标符合设计要求。谐波杂散在频率高端较为临界,经多次测量,未出现超过指标的情况,也符合要求。

图10 中频信号频谱

在输出端加入50 MHz 带宽的带通滤波器,再对产生的时钟信号进行测量,取200 MHz,2 GHz,

2.8 GHz 3 个典型时钟频率,测量结果如图11、图12所示。

图11 时钟信号功率

图12 时钟信号杂散

从图中的测试结果可以看出,时钟输出功率在-0.02 dBm~0.59 dBm 时,杂散均优于-70 dBc,各项指标均符合设计要求。

目前该信号源产品已经成型,通过了验收,并应用到部分项目的调试中。信号源成品如图13 所示。

图13 信号源成品图

5 结论

本文设计的自制信号源,能够有效缓解高速电路调试时对台式源的需求,同时提供多路时钟和中频信号。并且该信号源能够根据实际需求,对输出频率进行实时更改,使用起来灵活、方便。