一种基于SAEAS5643协议的1394B总线监控设计与实现

徐文杰

【摘要】 SAE AS5643协议具有确定性、高可靠性的特点,并已成功应用在航空航天等高安全关键领域。文中对SAE AS5643协议进行了特征分析。提出一种基于AS 5643协议的1394B总线监控设计方法,采用FPGA实现对总线数据的实时监控,并通过DMA高效传输至CPU模块中。文中详细讨论了硬件、逻辑和软件等设计方法与实现,通过不同的场景的测试验证。结果表明,该监控设计方法满足基于SAE AS5643协议的总线监控要求。

【关键字】 AS5643 总线监控 1394B 预分配通道号及带宽

一、概述

基于SAE AS5643[1]协议的1394B总线通信技术,具有高传输带宽、热插拔、传输距离长等特点[2],文中首先介绍SAE AS5643的技术特点,其次分析了总线监控设计的逻辑设计及具体工作流程,然后提出了软件设计,最后对设计进行功能测试验证,最后给出了监控功能的设计结论。

二、AS5643协议分析

作为一种确定性安全网络,SAE AS5643采用异步流包[3]进行固定帧速率的传输方式,通过静态分配通道号及控制传输偏移等技术手段实现了确定性传输,并通过增加垂直奇偶校验(VPC)等方式,进一步加强数据完整性,提高安全性,确保其应用在关键安全可靠领域。

2.1固定帧速率

SAE AS5643协议中,除物理层包数据意外,其他总线通信均采用异步流包格式。为了确保通信的确定性,协议采用一种固定帧速率的方式来实现各个网络节点的时间同步,具体操作为:在每条总线上,CC节点会以固定的帧率(如:12.5ms)传输STOF包(一种特殊的异步流包),用来通知总线上的所有节点一个新帧周期的起始。依据STOF包的1394总线的时间同步,是SAE AS5643协议通信的基础。

2.2预分配通道号及带宽

基于SAE AS5643协议的1394总线采用异步流包在异步周期内发送的等时包,寻址方式采用通道号。在机载航电等应用领域,采用预先静态分配通道号的固定方式进行确定性通信。网络通信时,不同节点按照预先定义的通道号进行包数据通信,而接收节点也会按照预先定义的本通道号进行接收,保证确定性。

系统设计者在网络拓扑固定之后,在通过预分配通道号和总线带宽,来确保所有节点按照确定的发送、接收偏移时刻进行包数据的分时传输,提高了网络可靠性。

2.3垂直奇偶校验(VPC)

垂直奇偶校验是个无符号长整型数,其计算方式为:对包的有效数据的每个32位字按位异或(无进位),其本身除外,最终对异或的结果按位取反得到VPC值,示例如下:

1. VPC=ASM头的消息标识;

2. VPC=VPC 异或 ASM头的安全字;

3. VPC=VPC 异或 ASM头的节点标识字;

4. VPC=VPC 异或 ASM头的优先级/有效数据长度字;

5. VPC=VPC 异或 有效数据的健康状态字;

6. VPC=VPC 异或 有效数据的心跳字;

7. 继续与所有的余下的有效数据的字 异或;

8. VPC=VPC 异或 包尾的STOF TX偏移量;

9. VPC=VPC 异或 包尾的STOF RX偏移量;

10. VPC=VPC 异或 包尾的STOF DP偏移量;

11. VPC=VPC 按位取反。

三、监控设计

本文设计中,1394总线监控设计,主要考虑故障情景再现,及为系统设计者提供有利的网络规划参考依据,主要的设计需求[4],包括:1.监控整个网络包流量情况,主要包括:异步流包和物理包;2.保证包数据的順序完整性;3.标记相对时间戳;4. DMA监控数据,上报至CPU模块;5.特殊包消息的过滤监控等。

3.1硬件设计

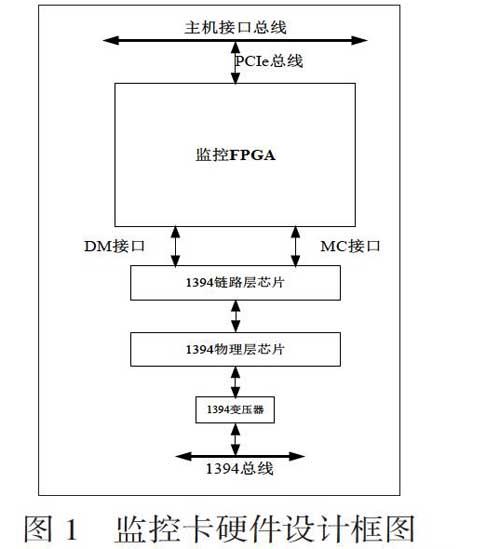

鉴于上述监控需求,设计监控模块的硬件原理,如图1所示。硬件设计,主要包括:监控FPGA、1394链路层芯片、1394物理层芯片及1394收发器等,此外还包括:电源电路、时钟电路、复位电路等基础电路。

3.2逻辑设计

如图1所示,监控FPGA为监控模块中的核心设计,主要完成基于SAE AS5643协议的1394总线监控功能,其设计框图,如图2所示。

如图2所示,监控FPGA完成了监控设计的主要功能,其子功能主要包括:支持DMA传输的PCIe接口功能[5][6]、时间计时器、调度功能、接收接口功能、DMA轮询控制功能、全监控包缓存及信息FIFO、特色监控包缓存及信息FIFO、控制及状态寄存器功能、时钟功能、配置SPI读写控制功能等,下面对每一个功能进行详细描述。

支持DMA传输的PCIe接口功能,主要实现PCIe接口功能,包括:空间配置等,其主要采用FPGA的IP核实现;时间计时器,主要功能为:在模块上电时,同时维护记录两个时间计时器,分别为:上电计时器和STOF计时器。在实际捕获的包数据中,每个捕获包消息,均要标记上述两个时间戳,方便后续重现分析;调度功能,主要作用为:对捕获到的包数据进行过滤分析,对特殊监控的包消息,特别分发在特殊监控包缓存FIFO和特殊监控包信息FIFO中;接收接口功能,主要功能为:上电初始化时,完成对LLC链路层芯片的配置;对LLC芯片中的包数据进行实时监控接收;DMA轮询控制功能,主要作用为:采用乒乓操作对接收到的全监控包消息和特色监控包消息,轮询调度至PCIe接口;全监控包缓存及信息FIFO和特色监控包缓存及信息FIFO,分别存放两类包消息,便于逻辑设计的跨时钟数据传输;控制及状态寄存器功能,主要作用为:软硬件接口实现。实现逻辑控制和状态上报等内容;时钟功能,主要实现逻辑内部的时钟资源生成,采用FPGA内部的时钟IP核实现;配置SPI读写控制功能,主要实现FPGA逻辑配置的在线升级功能。

3.3软件设计

软件设计在监控设计中相对比较简单,其主要功能包括:1.实现对监控逻辑的配置,包括:速率配置、DMA基址配置、软复位、监控特殊消息ID等;2.获取监控设计的状态信息,包括:计数寄存器、中断状态、物理端口状态、BIT状态等信息,并汇总各种消息之后,上报CPU模块本节点状态;3.数据迁移功能,在监控FPGA将监控包消息上传至指定区间后,软件将该数据搬移至非易失存储器上。

四、验证测试

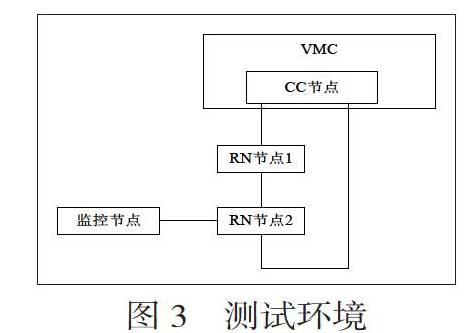

基于SAE AS5643协议的1394总线监控设计的验证测试,除了基本端口及功能的测试外,还重点在测试场景的合理模拟,主要考虑如下几点:1.总线复位之后的物理层包监控;2.特殊监控包消息的监控;3.时间戳的合理标记;4.包顺序的完整性。综合上述考虑,搭建1394总线验证测试环境如图3所示,主要包括:基于VMC的CC节点、节点1、节点2及监控卡等。

结合监控测试场景特點,设置主要测试项目如表1所示

1 特殊监控包消息 设置不同的特殊监控消息ID,查看特殊监控包消息是否正确监控

2 DMA传输 分别设置特殊监控消息和全监控消息监控,通过PCIe总线查看DMA轮询控制功能及DMA传输功能的正确性

3 时间戳 设置不同的STOF包周期、上电复位等情绪下,两个计时器是否合理工作,体现了包的先后顺序

4 包顺序的完整性 设置总线复位场景,监控总线复位前后,监控设计是否完整展现总线复位前及总线复位后的包消息数据的完整性

通过上述主要用例的功能检测,结果表明:本监控设计适用于不同场景下的包数据捕获,完整保持了消息的顺序完整性,再现了总线通信实情,满足了基于SAE AS5643协议的1394总线监控要求。

五、结束语

本文通过对基于SAE AS5643协议的理解和研究,在原有1394B总线通信基础上,提出了一种总线监控设计方法,实现了总线数据的全消息监控、特殊消息监控和DMA上传等功能,经测试验证,该监控模块具备实现高流量、DMA高效率传输、完整再现顺序完整性的数据监控能力。

参 考 文 献

[1]SAE-AS 5643:IEEE-1394B interface requirements for military and aerospace vehicle applications[S].2006

[2]李肇庆,朱线峰. IEEE1394接口技术[M]. 北京:国防工业出版社,2004.

[3]王宣明,田泽,魏艳艳,牛少平,徐文进.SAE AS5643协议分析及设计实现[J].计算机技术与发展.第25卷第7期,2015年7月.P213~215.

[4]韩一鹏,田泽,牛少平.一种SAE AS5643三节点仿真设备设计与实现[J].计算机技术与发展.2016年第26卷第3期. P202~204.

[5]廖寅龙,田泽.FC网络通信中PCIe的接口的设计与实现[J].航空计算技术.2010,40(4),P127~P130.

[6]马鸣锦,朱剑冰,何红旗,等.PCI,PCI-X和PCI Express的原理及体现结构[M].北京:清华大学出版社,2007