一种某型雷达阵面信息互连系统的FPGA实现方法

中国电子科技集团公司第二十研究所 李海成

为了提高某型相控阵雷达阵面多通道数据传输速率,设计了一种利用高速收发器进行数据高速传输的信息处理系统;通过合理的功能模块设计,实现了模块间多路1.8Gbps高速信号通信与模块间多路3.125Gbps高速光信号通信的信息互连系统。经整机调试表明,该高速信息互连系统,其性能稳定,满足该型雷达对于数据处理的高宽带、高速率要求。

随着军工设备性能的提升,数据量呈现爆炸式的增长态势,信号处理系统对于信号带宽、传输速率和通道数量等方面的要求愈发强烈。随着工艺技术的发展,满足各种应用场景FPGA产品应运而生。其中集成多路高速收发器的FPGA芯片,逐渐受到各大厂商以及客户的青睐。本文主要介绍一种模块间多路1.8Gbps高速信号通信与模块间多路3.125Gbps高速光信号通信的信息互连系统,其整体性能稳定、满足某型相控阵雷达对于高数据量、高速率传输的要求。

1 信息互连系统

信息互连系统接收到1路触发信号后,经过驱动将触发信号送入FPGA,在FPGA内部经过校正时钟采样后进行延迟,再分为16路,经延迟后进入时钟buffer,再将分配后的重频触发脉冲送至高速连接器与无源分配板相连接。

信息互连系统接收到从分配板送来的16对高速数据和指令进入FPGA,通过GTX转换至FPGA内部逻辑,对高速数据和指令进行打包及速率变换处理,转换成8条高速数据和8条高速指令信号,通过GTX发送至光模块,经由光纤传输至信号与处理分系统。

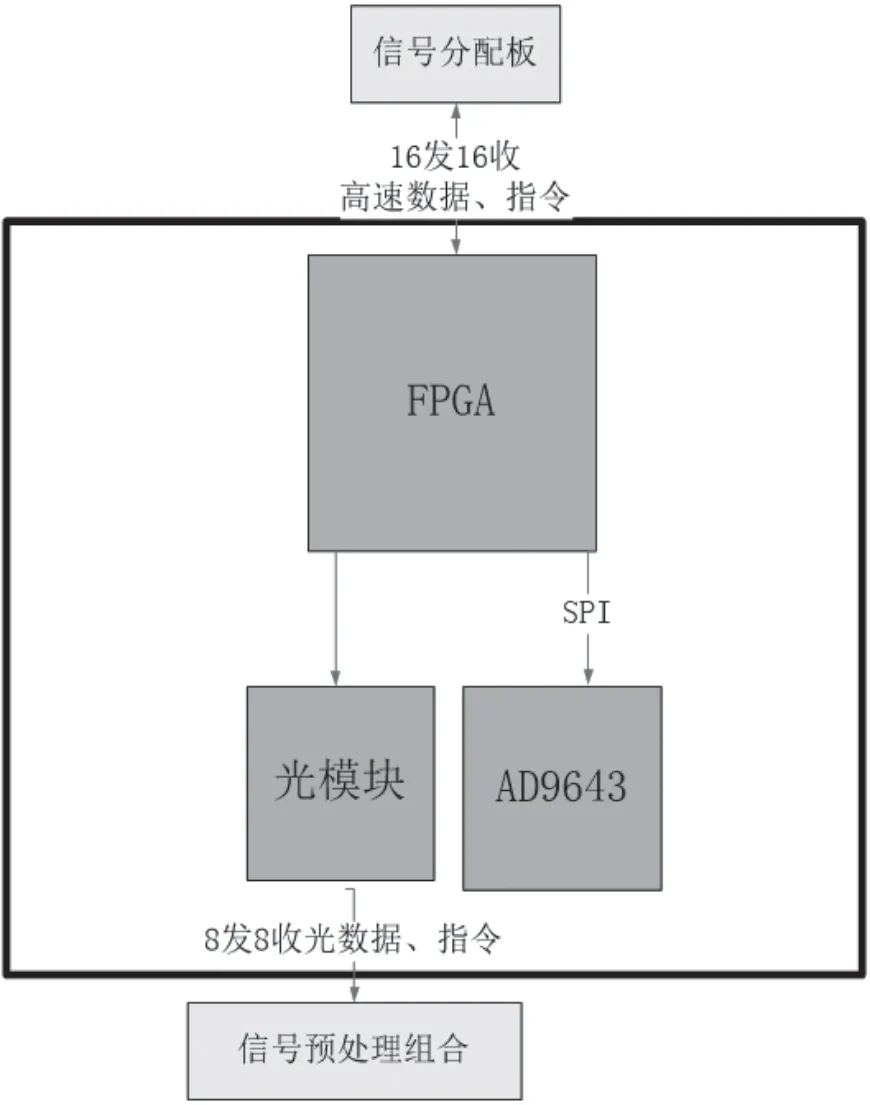

模拟中频信号进入信息互连系统后经过开关带通滤波组件后,进入ADC器件,经过高速采样进入FPGA进行DDC处理后,通过光纤发送给信号预处理组合。基准时钟分配给FPGA作为定时信号校正时钟,用于定时校正,同时基准时钟进入锁相环后,进行倍频产生所需的240MHz采样时钟,再进入时钟分配,对该时钟进行同步分频,输出120MHz时钟进入FPGA,作为系统时钟和GTXREFCLK。其所运行的系统组成框图如图1所示。

图1 信息互连系统框图

2 基于FPGA的信息系统转换

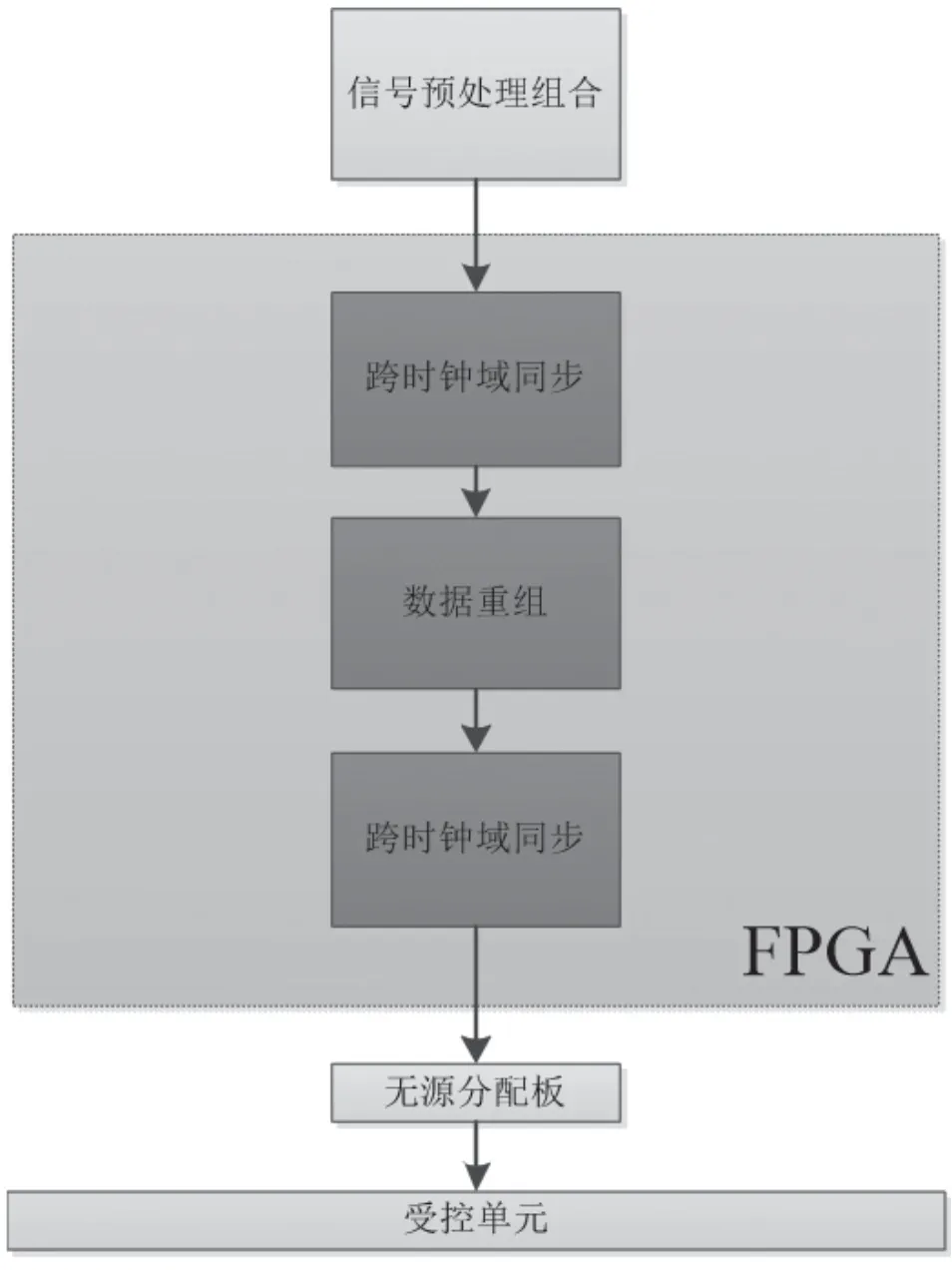

系统设计以Virtex-7690t FPGA芯片为核心,首先将指令以3.125Gbps速率的光信号写入RAM,经过跨时钟域同步,将解析完成的协议以1.8Gbps速率的电信号发送至16个受控单元。在接收到16个受控单元返回的协议数据时,进行解析并将故障信息按照约定,加载在协议数据中,经过跨时钟域处理以3.125Gbps的速率发送至不同的8个光传输链路。受控单元根据解析的协议,控制DA/AD进行波形产生以及波形采样,将采样的数据按照约定,通过高速接口将数据传输至信息交互系统,信息交互系统将相邻两路数据合成,通过光链路发送至信号预处理分系统。该高速信息互连系统,其性能稳定,满足该型雷达对于数据处理的高宽带、高速率要求。其结构图如图2所示。

图2 接口关系框图

2.1 FPGA功能及连接设计

该系统由数据通信模块、数据采集模块以及数据重组模块组成。数据通信模块采用高速Aurora协议实现;数据重组模块按照既定数据传输格式进行数据重新解码编码操作;数据采集模块是将中频信号进行滤波处理之后,利用AD9643芯片对数据进行欠采样,并经过DDC下变频处理,按照协议要求进行抽取处理,并将抽取之后的数据按照协议进行传输。

2.2 上行链路功能设计

该链路主要涉及功能有数据通信、时钟同步以及数据重组。信息交互系统在接收到信号与处理组合下发的协议数据时,首先经过跨时钟域同步处理,在将数据按照既定方案进行解析,并按约定的数据格式对数据进行重新组合,下发至受控单元,受控单元解析相应命令并开始工作。其工作流程如图3所示。

图3 上行数据链路框图

2.3 下行链路功能设计

该链路由两条支路组成,根据不同的工作模式,切换不同的工作通道。在正式工作模式下,一是受控单元将温度、丢包标志等故障信息添加在协议数据中,通过高速传输链路传输至信息交互系统模块,信息交互系统模块将16个受控单元的故障信息进行收集,重组在协议数据中传输至信号预处理组合;二是受控单元将按命令将数据传输至信息交互系统,信息交互系统将相邻的数据重新组合在一起传输至信号预处理组合。

在非正式工作模式下,信息交互系统接收来自受控单元的协议数据以及中频信号,协议数据主要是用于传输必要的命令以及报送故障信息,中频信号主要是模拟受控单元的数据,在受控单元关闭的情况下,交验整机的工作状态。其链路框图如图4所示。

图4 下行数据链路框图

3 实验结果

该信息交互系统在设计中合理使用PLL和DCM,合理约束软件时序,保证了软件的稳定工作。在整机工作过程中,一方面保证在正式工作状态下,故障信息回传、回波数据传输稳定;另一方面在非正式工作状态下,AD采样稳定以及按照协议进行DDC下变频处理并稳定回传数据。

4 结论

基于FPGA的信息互连系统具有高宽带、高速率、误码率低的特点。该系统采用光信号与电信号之间的高速率转换,实现信号的高速稳定传输。经过雷达整机调试表明,该高速信息互连系统,性能稳定,满足该型雷达对于数据处理的高宽带、高速率要求。