某模/数转换器低温下输出异常失效分析

白璐,朱恒静,高炜祺

(1.中国电子科技集团第24研究所,重庆 400060; 2.中国空间技术研究院,北京 100094)

引言

我单位设计的某10位模/数转换器在我单位筛选、检验过程中未发现任何异常。但是用户在使用过程中发现了如表1所示的异常现象,此种异常电路占总数的17 %,即:

用户与我单位进行电话沟通后,将异常电路退回。收到退货电路后,我单位按照原测试系统、测试方法进行低温复测,即:在低温箱-60 ℃条件下放置30 min后,将电路取出进行测试。所有电参数全部满足指标要求,未发现用户反馈的异常现象。但是按照用户的测试方法,将电路在低温恒温下测试,发现当模拟输入电压大于5 V时,故障电路最高位数字输出出现随机变低的现象,低9位数字输出正常,即在低温恒温下功能异常,无法正常工作,故障现象得到确认。

1 失效原因分析

1.1 功能简介

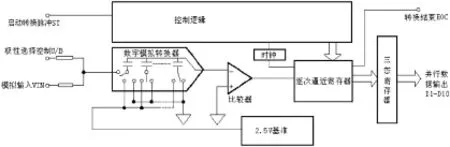

此次反馈的异常电路为一款模数转换器,当控制端ST为高电平时,转换器处于复位状态,模拟输入经衰减后进入电荷重分布数/模电路进行采样。当ST变低后,电荷重分布数/模电路进入保持状态,控制逻辑控制时钟开始振荡,在时钟的控制下电荷重分布数/模电路从最高权重位开始逐位置“1”,比较器比较置位后的电荷重分布数/模电路输出,逐次逼近寄存器锁存比较结果。在12位权重位比较完成后,控制逻辑将转换结束信号置低,将转换结果通过三态寄存器输出到引出端。其功能原理图如图1所示。

1.2 失效原因分析

基于上述失效现象和电路工作原理,造成最高位数字输出随机变低的现象有几种可能性,包括:①内部比较器错误;②时序冲突。

1.2.1 内部比较器错误

如果比较器本身在低温下比较结果错误,则电路会输出错误结果。但在转换过程中比较器比较错误后,最高权重位一旦存贮错误结果,则低9位应该为全“1”,而失效电路低9位与正常结果一致,说明此时比较器工作正常,未发生比较错误,且转换过程中存贮(低9位)的所有数据均正常。因此,可以排除比较器比较错误的情况。

1.2.2 时序冲突

从测试结果可以观察到,最高位只会随机从“1”变为“0”,而未出现从“0”变为“1”的情况当输入0.4 V模拟信号时,输出数据始终小于512,说明最高位始终为0,当输入5.3 V时,有时会出现小于512的情况,说明最高位跳变为0。当出现时序冲突时,在逐次逼近寄存器中会出现误脉冲,导致锁存错误结果,所以,不能排除由于时序冲突造成电路故障。

1.2.3 小结

电路低温故障可能是由于时序冲突造成。

2 失效机理分析

2.1 时序冲突机理分析

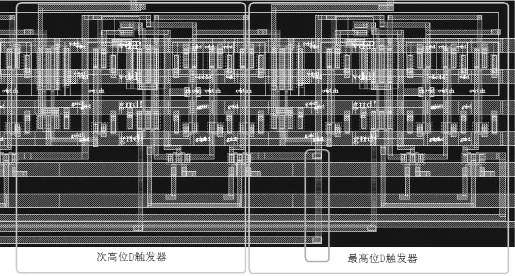

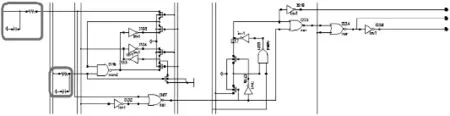

图2 是逐次逼近寄存器组的电路原理图,图3是单个逐次逼近寄存器的电路原理图。

表1 故障电路在用户整机上的表现情况

图1 某模数转换器功能原理图

图2 逐次逼近寄存器组电路原理图

如图2所示:整个逐次逼近寄存器组由两层寄存器组成,底层为13个D触发器,用于依次逐位置“1”,上层为12个电平触发器,用于锁存比较器的比较结果。在D触发器逐位置“1”过程中,若相邻两个D触发器的数据分别为“1”和“0”,则I107异或门会输出高电平,电平触发器输入MOS管导通,输入比较器比较结果,并置位电平触发器的输出。在下一振荡周期,相邻两个D触发器的数据均被置“1”,I107异或门输出低电平,电平触发器关断输入MOS管,锁存比较器比较结果,并将该结果输出。

当整个转换完成后,转换状态寄存器将复位13个D触发器,为下一次转换做准备,如果13个D触发器的复位速度不一致,就会在I107异或门上形成误脉冲,导致对应的电平触发器误触发,锁存错误结果。从电路上看,13个D触发器的电路基本一致,最高位D触发器的输出仅多了一个控制采样的门电路负载。

最高位和次高位D触发器(见灰色方框)的版图如图4所示,由于该转换器采用的是双层布线工艺,因此最高位D触发器输出驱动控制采样的门电路时,采用了一段多晶走线(见黑色方框)。当氧化工艺出现圆片间厚度偏差,多晶走线下的氧化层变薄时,该多晶走线到地会形成一较大的寄生电容,降低最高位D触发器的复位速度。如果最高位D触发器本身由于MOS管工艺偏差的原因,导致复位速度低于次高位[1]。同时低温环境下,温度越低,用于复位的PMOS管阈值电压越低,充电速度急剧下降,导致D触发器复位速度进一步降低。这几个方面影响的叠加,就会使对应的I107异或门出现较高的误脉冲,导致最高位电平触发器出现误动作,锁存错误结果。由于转换结束后比较器正处于复位状态,所以最高位会根据比较器的复位速度随机锁存数字“0”。其他的D触发器由于版图完全一致,因此复位速度仅由MOS管工艺偏差影响,不会引起误脉冲[2]。

图3 单个逐次逼近寄存器电路图

图4 最高位D触发器版图

图5 模拟寄生电阻和寄生电容的单个寄存器电路图

该转换器的模拟输入范围为0~10 V,只有当模拟输入电压高于5 V时,最高位才为“1”,因此电路将表现为低温输入大信号时,最高位输出随机出现“0”,而对低于5 V的模拟输入信号则输出正确转换结果。

2.2 仿真试验

计算逐次逼近寄存器组的D触发器复位端和最高位D触发器的输出端的多晶走线寄生电阻和电容,按照工艺线提供的pdk,多晶走线的方块电阻为13~21 Ω/□,寄生电容为0.052~0.072 fF/um2,栅氧寄生电容为2.55~3.01 fF/um2,用rpoly1和cpoly两种元件模拟其效果,模拟的电路如图5所示,其中,所有D触发器复位端根据多晶走线的宽度和长度计算寄生电阻为260~420 Ω,我们取中间值340 Ω,寄生电容计算值3.7~5.2 fF,我们取中间值4.5 fF。最高位D触发器输出端根据多晶走线的宽度、长度和负载MOS管长宽比计算寄生电阻为170~276 Ω,我们取中间值223 Ω,寄生电容计算值15~23 fF,由于该寄生电容为影响复位速度的关键元件,我们分别取中间值19 fF和最大值23 fF。寄生元件位置在方框标记处。

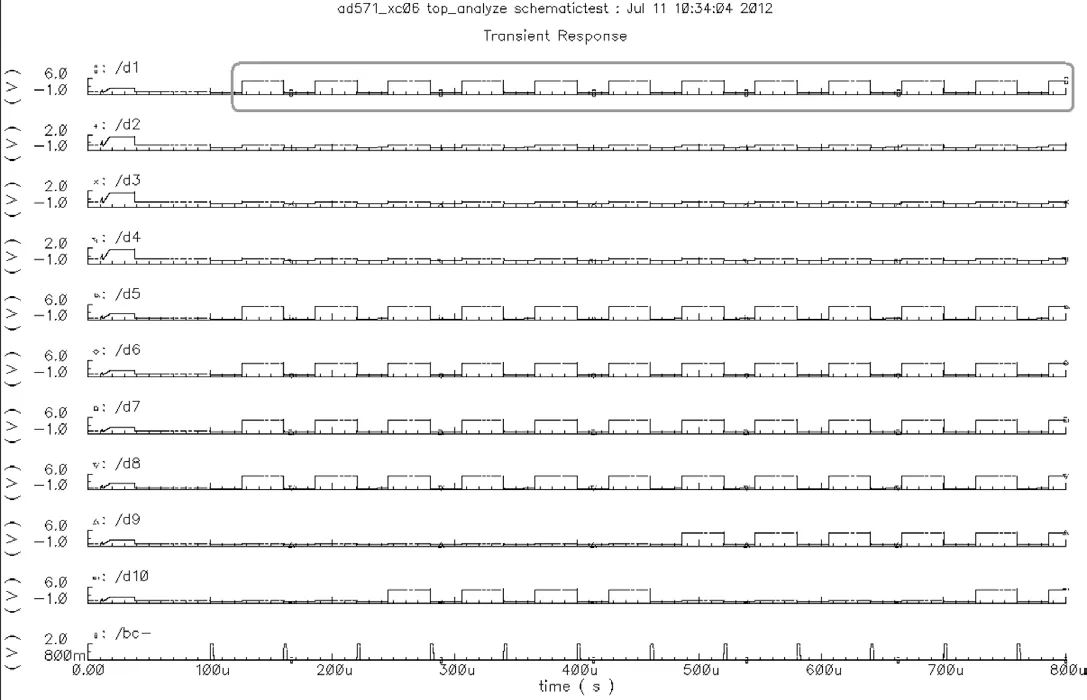

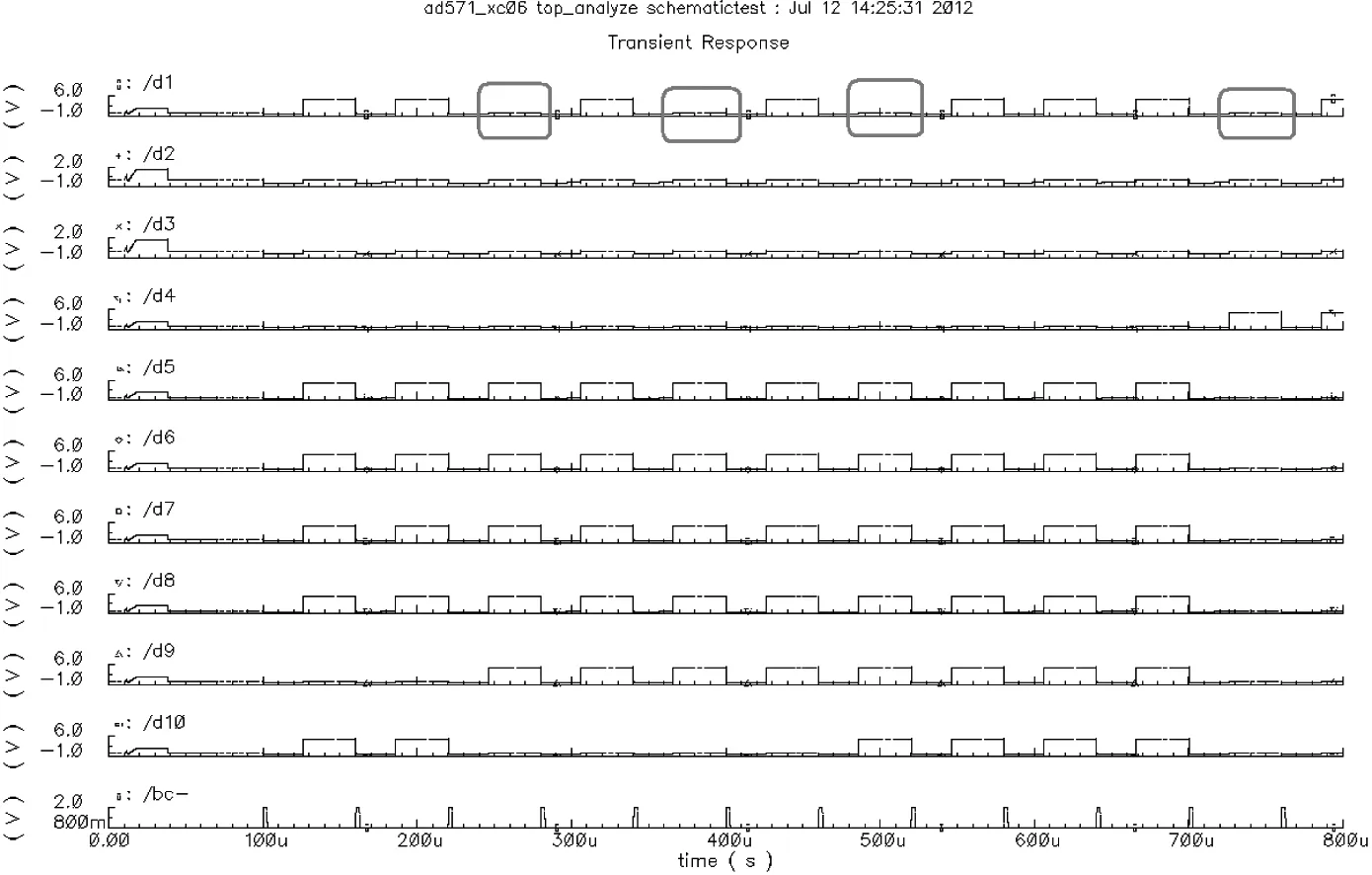

模拟输入外加5.6~10 V的斜坡信号,ST脉冲宽度2 us,周期60 us,模拟输入信号每个周期增加1/4LSB,23 fF寄生电容-40 ℃的仿真结果如图6所示,23 fF寄生电容-55 ℃的仿真结果如图7所示,19 fF寄生电容-55 ℃的仿真结果如图8所示。

从图6中可见,寄生电容为23 fF时,-40 ℃环境下d1~d8输出位不变,最低两位d9、d10除起始周期外,每四个转换周期变化1LSB,与模拟输入情况完全一致。而在图7中,-55 ℃,寄生电容为23 fF的情况下,d2~d10位变化情况与图7一样,仅初始值不同,但d1最高位随机出现变“0”的情况,与测试结果一致。而图8,-55 ℃,寄生电容为19 fF时的情况与图7基本一致,仅最低两位d9、d10初始值有所不同(见图6、图7、图8方框标记处)。

图6 23 fF寄生电容-40 ℃仿真结果图

由此可见,当最高位D触发器输出端的寄生电容取工艺偏差的最大值时,仿真复现的现象与低温长线测试的结果完全一致。经询问用户,同批次该转换器共使用34只,有6只出现同样故障,并非所有电路均存在故障,故障率约17 %。因此,在用户处转换输出偏低的原因是,由于局部氧化层厚度和MOS管特性的工艺偏差,导致寄生电容容值不同,寄生电容较大的电路中本来应该同时复位的寄存器组出现了延时,最高位寄存器滞后复位,从而引起误脉冲,锁存数据的电平寄存器出现误动作,锁存了错误的结果。导致在输入大信号(大于5 V)时,最高位输出“0”,数据结果直接减少512,控制器判断出现欠压,进入保护状态。为此,可以确定失效电路的输出偏低是由于工艺偏差引起误脉冲,导致电平寄存器误动作,锁存错误结果所致。

3 结论

综上所述,此次异常的电路低温故障是由于工艺偏差导致复位PMOS管阈值电压变低,充电速度下降,最高位寄存器滞后复位,在电路内部触发误脉冲所致[2]。同时,因测试方法的差异,导致故障电路筛选过程中未能有效剔除而流入用户。

4 后续改进措施及建议

1)经与该用户现场协商,后续针对提交该用户的该转换器电路需采用输入固定模拟电压低温在线测试的方法进行加严筛选、控制。已交付用户的原状态尚未经历低温试验的产品建议用户返回进行低温在线测试筛选,剔除不合格品。

2)优化线路结构和版图,采用三层铝布线[3],降低寄生电容效应,从设计上彻底杜绝误脉冲的产生,更改后的产品送该用户验证。

图7 23 fF寄生电容-55 ℃仿真结果图

图8 19 fF寄生电容-55 ℃仿真结果图