DM642嵌入式图像融合处理系统硬件设计研究

郝雅婷,马立新

(中国矿业大学,北京,100083)

在工业监督控制、机器视觉、医学影像处理领域会应用一些复杂的算法来进行多图像处理数据,基于这样的要求传统的图像处理系统很难满足系统处理要求。文章面向实时图像处理,采用模块化的设计思想以新一代高性能多媒体专用DSP芯片DM642为核心,打造了体积小、能耗低、应用性强的嵌入式实时图像处理可拓展硬件平台。

1 DM642嵌入式图像融合处理系统的总体架构设计

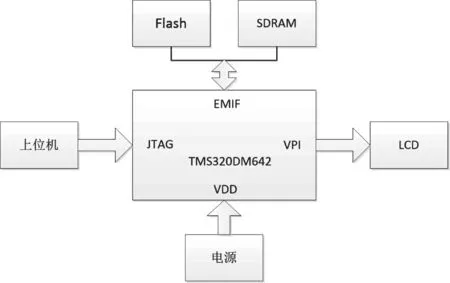

DM642嵌入式图像融合处理系统是基于专用数字媒体应用的高性能32位定点芯片DM642进行设计开发的,系统以DM642为核心,由 图 像 采 集 模 块、图像处理模块、图像存储模块以及电源模块等构成。系统 的具体工作原理如下所示:在系统通电之后 从 FLASH 加载程序, 完成对DM642 的 初 始 化 并 通 过 I2C 总线来实现对视频编解码芯片的参数设定。在设定好参数之后开展进行图像信息的采集整理,从四路图像传感器采集到的模拟图像信号经过解码转换成数字图像信号后会通过DM642视频接口传送到DSP中,再经由内部图像处理后,通过DM642视频接口解码传出显示。

DM642嵌入式图像融合处理系统总体架构如图1所示。

图1 DM642嵌入式图像融合处理系统架构

2 DM642嵌入式图像融合处理系统的内部配置

■2.1 系统存储空间

DM642嵌入式图像融合处理系统程序或者数据存储空间地址以字节为基本单位进行统一编写,整个寻址空间的大小为4G,片上存储器、片上外设、外部的储存器都能够映射到4G的字节空间中。DM642通过EMIF接口访问片外存储器。

CEO空间,DM642嵌入式图像融合处理系统CEO子空间会被配置成64位的SDRAM接口,在配置之后信息会同时外扩给SDRAM使用。

CEI空间,DM642嵌入式图像融合处理系统的CEI空间配置为八位异步静态存储器接口,将接口信息分配给系统的Flash、状态控制寄存器使用。

■2.2 Video Port的配置

DM642嵌入式图像融合处理系统设置了三个视频口,其中的VP2是单一功能的视频口,VP0和VP1则是与McBSP或McASP复用。其功能选择由DM462上的外设配置寄存器进行配置管理。VP0配置VP0A和VP0B为两个八位BT.656视频输入口,用来连接两路BT.656标准数字视频输入信号。VP1配置VP1A和VP1B为两个八位BT.656视频输入口,用来接通两路BT.656标准数字视频输入信息。VP2配置VP2A为一个八位BT.656视频输出口,用来输出一路BT656标准数字视频输入信息。

■2.3 I2C总线配置

DM642嵌入式图像融合处理系统上集成一条I2C总线,在总线系统中的每一个设备都会有一个对应的唯一地址,可以根据此地址来判断信号对应哪一个设备。I2C总线对设置为从模式的SAA7121H和TVP5150PBS进行配置。

3 DM642嵌入式图像融合处理系统硬件设计

DM642嵌入式图像融合处理系统硬件结构如图2所示。

■3.1 视频编解码芯片的选择

DM642嵌入式图像融合处理系统的视频解码芯片选择有TVP5150芯片、SAA7115芯片、ADV7181芯片,文章现就这几种视频解码芯片的使用进行综合分析。从市场价格上来看,TVP5150芯片的价格相对较低,其价格大约上是另外两种视频解码芯片价格的三分之一。从大小上来看,TVP5150芯片的封装较小,在使用的时候具备连线操作简单的特点。从性能上看,TVP5150芯片的性能虽然没有SAA7115芯片、ADV7181芯片的性能理想,但是它也相对耗能低。在选择芯片的时候需要综合考虑封装大小、功能要求、成本、耗能等因素。所以,本设计应用四片TVP5150芯片用于视频输入和一片SAA7115芯片用于视频输出以适用于对能耗消耗要求比较高的便携电子产品。

图2 DM642嵌入式图像融合处理系统硬件结构图

■3.2 电源模块设计

DM642嵌入式图像融合处理系统在运作的时候需要得到高精准度、高稳定度的双电源供电系统支持,系统在设计的时候采用了两个5V电源驱动开关电源调整器(TPS54310)分别供给DSP的内核电源电压CVDD(1.4V)和外围数字电源电压DVDD(3.3V),外部附加简单的延时电路,确保内核电压先于数字电压上电。TPS543l0(TI)的输出精度是1%,完全满足DSP工作要求。视频编码器、时钟芯片、通用异步收发器和CPLD等还需要3.3V和1.8V供电,选用AMSlll7-3.3V和LM1117-1.8为这些器件供电。在PCB设计中,需要注意把模拟电源和数字电源分割开以免造成噪声干扰。

■3.3 存储器模块设计

本设计需要处理大量的图像数据,需要通过EMIF增设两块同步动态随机存储器,SDRAM具有容量大、读写速度快,成本小的特点。DM642的数据总线、地址总线和控制引脚都通过一个33Ω的电阻与SDRAM相连接,用以高频噪声的过滤,保证信号的平稳。DM642同时需要扩展FLASH存储器存储断电后仍需保存的数据,FLASH具有容量大、体积小、价格低廉的优势。

■3.4 I2C接口设计

由于一片TVP5150PBS视频解码器只能配置为2个不同的从设备地址,需要采用一个I2C通道控制芯片SN74CBTLV3257实现与四片TVP5150PBS的通讯,从而实现多路图像信号的采集。

■3.5 CPLD模块设计

DM642的GPIO口只有16个,为进行I/O口的扩展本设计采用CPLD复杂可编程逻辑器件,其型号为EPM3064ATC100,有73个引脚可以配置为I/O口,可以满足许多功能的拓展需求。

■3.6 时钟模块设计

本系统中存在多个不等的时钟频率,无法采用标准晶振达到理想效果,因此选用可编程时钟芯片CY22381,可以通过编程提供所需多路时钟信号,同时还能节省电路板的面积。

■3.7 串口模块设计

UART是一种不带同步调制的全双工串行传送方式,为了能够实现DM642嵌入式图像融合处理系统和PC机的实时性通信获得理想的数据信息,系统选择应用具有较高数据传输速率的通用异步收发器TL16C752B,运行速率能够达到3.125Mbp,在顺利连接之后能够完成RS285/RS422电平转换。

■3.8 JTAG接口模块设计

DM642的JTAG为14pin双排插口,DM642可以通过TRST#引脚复位,使DSP初始化。

4 结束语

综上所述,文章所研究的DM642嵌入式图像融合处理系统在运作的时候具备成本低、体积小、可拓展性强、稳定性高的特点,图像通过视频的解码芯片能够将模拟图像信息转换为一种DM642能识别的数字信号。在DM642嵌入式图像融合处理系统内经过高效率的图像识别算法处理能够实现对预定目标信息的融合处理,处理之后的数字信号会被视频解码芯片转变为模拟信号,之后在显示器上输出。本设计基于DM642将信号格式扩展到四路视频采集整理,由此扩大了视角的范围。未来还可根据应用实际情况,在现有的基础上在预留的存储器空间和I/O口对系统进行更深入的拓展,因此本设计具有重要的参考价值和推广意义。