基于AD9914的多参数可控频率源设计

曾超林,李希密,尹红波,王洪林

(中国船舶重工集团公司第七二三研究所,江苏 扬州 225101)

0 引 言

在现代雷达系统和电子对抗设备中,频率源起着无可比拟的作用。传统的频率合成器波形单一,参数不可调节,无法适应现代战场复杂多样的电磁环境,而基于现场可编程门阵列(FPGA)+直接数字频率合成(DDS)技术的DDS设备具有参数可控制,发生方式简单,灵活多样等优点,能够快速实现复杂的波形发生系统[1]。

DDS是一种新型的频率合成技术,具有相对带宽大、频率转换时间短、分辨率高和相位连续性好等优点,较容易实现频率、相位以及幅度的数控调制,广泛应用于通信领域。

基于DDS的以上特点,选用ADI公司的多功能集成芯片AD9914完成了多参数可调节的频率源设计。

1 硬件设计

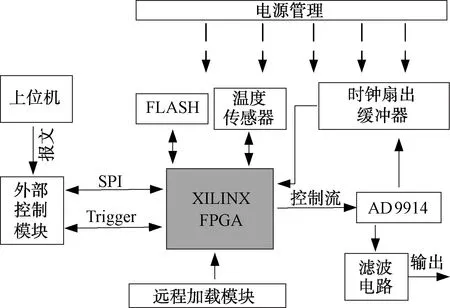

整个系统电路如图1所示,包括上位机、外部控制模块、FPGA外围电路、AD9914电路、时钟管理电路、低压差分信号(LVDS)驱动电路、电源管理、远程加载模块以及滤波电路。

图1 系统结构框图

1.1 系统工作原理

上位机软件使用RS232串口实现计算机和外部控制模块的信息交换,它按照通信协议向控制模块发送不同的指令,Xilinx FPGA加载AD9914,从而使频率源处于合适的工作状态。

外部控制模块采用Intel公司的EPM570T144I5作为主芯片,产生波形触发信号,负责通用异步收发传输器(UART)信号向串行外设接口(SPI)信号的转换,并将频率源的状态信号上报给上位机软件。为了保证信号传输成功并且降低信号之间的串扰,选用MAX9122芯片将单端信号转成差分LVDS信号,LVDS在2根导线中都传输了电压,具有很好的抗干扰性。

Xilinx FPGA型号为XC6SLX100,它工作时仅需3.3 V供电,供电方式简单,有利于模块的小型化。此外,BANK2同时支持低压TTL(LVTTL)和LVDS 2种电平标准,将外部输入的LVDS信号接入BANK2,利用FPGA内部输入缓冲器完成电平转换工作。

由于FPGA芯片一般不能掉电保持固件,因此需要外部FLASH存储FPGA固件,在上电的时候再将固件配置到FPGA中。同时,使用了1片远程加载芯片,它采用封装内系统(SIP)技术集成了单片机和千兆以太网物理层,将JTAG链路转换成网口信号,可以远程升级代码,具有体积小、易于远程维护升级等突出优势,极大降低了外场试验、微波暗室等条件下雷达整机调试的难度。

温度传感器型号为DS18B20,测温精度达到0.1 ℃,测温范围在-70 ℃~+150 ℃之间。DS18B20采用单一数字总线通信,仅需使用一个输入/输出(IO)资源,便能实现环境温度的监测。

1.2 DDS原理

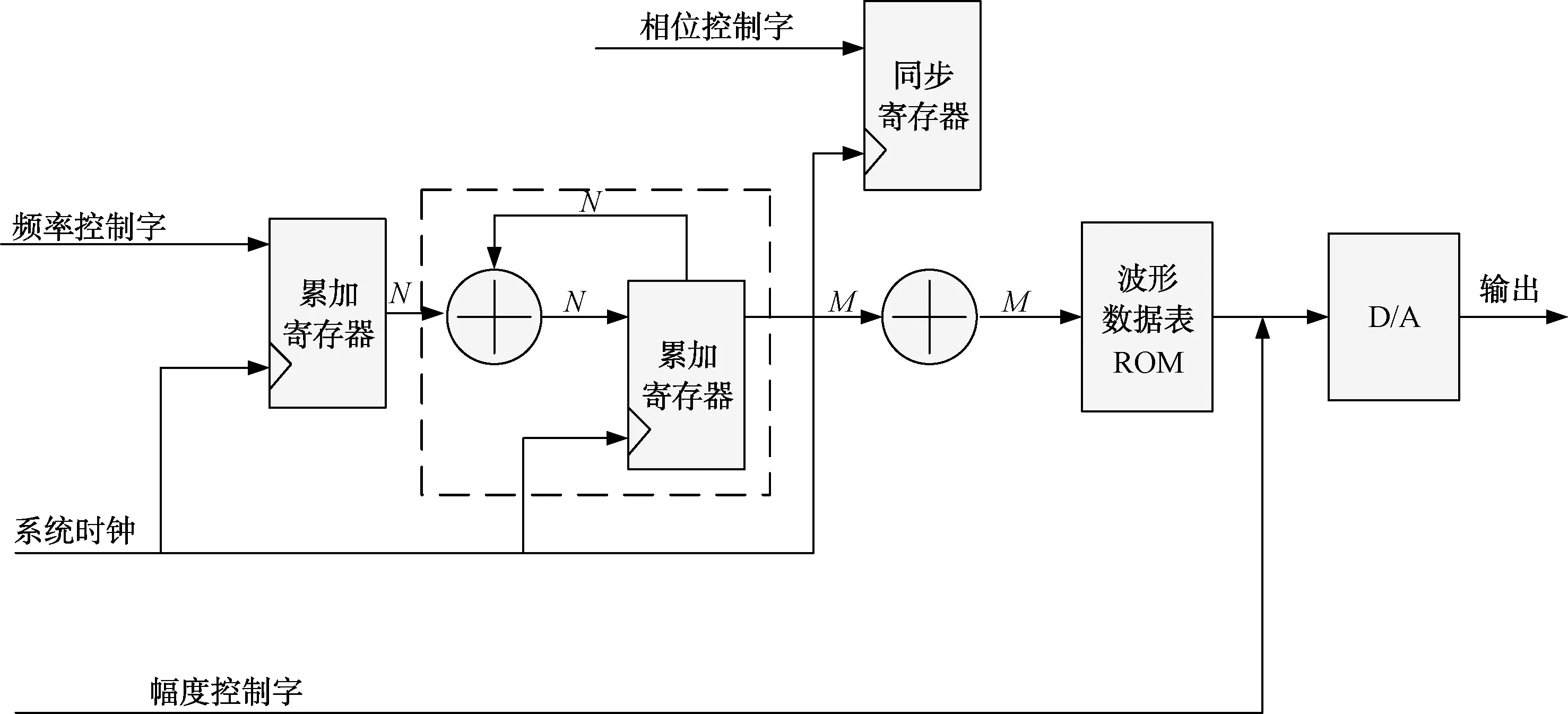

AD9914内部的DDS结构如图2所示。

图2 DDS基本结构图

由图2可知,DDS主要由相位累加器、相位调制器、波形数据表以及D/A转换器组成。相位累加器由N位加法器与N位寄存器构成,它输出的数据就是合成信号的相位。相位累加器的溢出频率就是DDS输出的信号频率。用相位累加器输出的数据作为波形存储器的相位采样地址,这样就可以把存储在波形存储器里的波形采样值经查表找出,完成相位到幅度的转换,并通过在采样点序号上加一个相位控制字实现相位的调整,最后由波形存储器输出数据,并由幅度控制字调节数据大小。波形存储器的输出数据送到D/A转换器,由 D/A 转换器将数字信号转换成模拟信号输出。若DDS的时钟频率为Fclk,频率控制字为1,则输出频率Fout=Fclk/2N,这个频率是1个基频。若设频率控制字为B,B只能是整数,且有以下公式:

(1)

理论上由以上3个参数就可以得出任意频率和幅度的输出波形,且可得到频率分辨率由时钟频率和累加器的位宽决定。参考时钟频率越高,累加器位数越多,输出频率分辨率越高。

1.3 AD9914工作方式

AD9914共有5种工作模式[2-3],本文使用了并行数据端口模式、PROFILE调制模式和数字斜坡调制模式。在并行数据端口模式中,DDS的控制参数直接由32位并行端口调制,功能引脚F0~F3定义了32位并行端口控制DDS的哪个参数。此种模式适用于相位编码信号的产生。

在PROFILE调制模式中[4],DDS控制参数直接由32位并行端口控制,利用外部PROFILE控制引脚PS0~PS2选择整机想要的PROFILE,实现对DDS控制参数的调制。若需要对幅度参数进行调节,需要开启外部输出幅度键控引脚OSK。此种模式适用于脉冲调制,当不需要输出波形时,配置幅度控制字对应的PFOFILE为最小值;当需要输出波形时[5-9],配置幅度控制字对应的PFOFILE为最大值。

在数字斜坡模式中,DDS控制参数由数字斜坡发生器DRG直接提供,斜坡发生参数由并行IO端口控制,它控制着斜坡的上升和下降斜率、斜坡上下限值、上升和下降的步长和步率。通过并行编程方式对AD9914内部寄存器进行配置,即可控制DRG的各种参数[10]。

选用数字斜坡模式中的非驻留斜坡高位和非驻留斜坡低位产生正负线性调频信号。在非驻留斜坡高位模式中,斜坡方向引脚DRCTL正向转换时,启动正斜坡斜率,在达到上限值之前会始终以正斜率斜坡输出,达到上限值之后会立即跳转到下限值,如果工作参数不变,DRG会始终保持该限值输出。非驻留斜坡低位工作方式与高位类似,这里不做赘述。利用非驻留斜坡和PROFIL模式,能够实现线性调频脉冲信号的发生。

2 软件设计

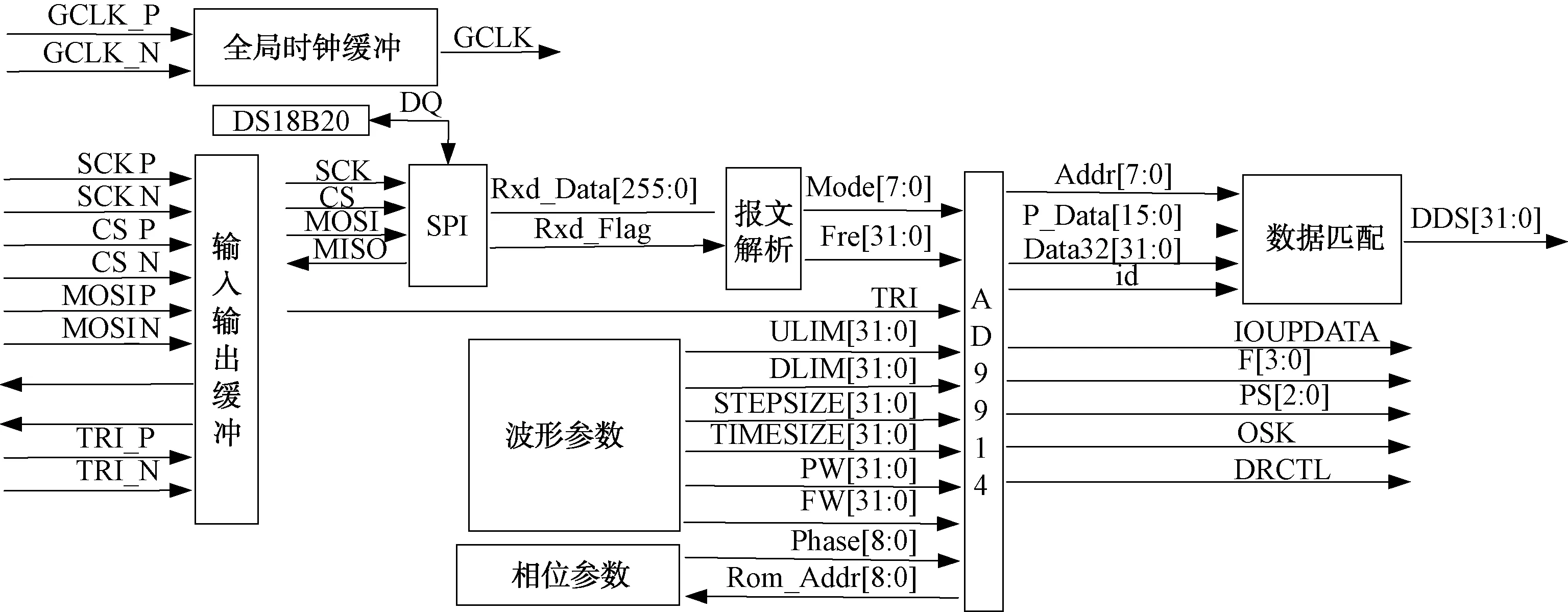

采用Verilog HDL硬件描述语言,并借助Xilinx公司ISE14.7开发软件完成了代码编写,软件框架按功能划分为3个部分,包括报文接收模块、报文处理模块以及波形发生模块,其结构如图3所示。

图3 软件基本结构图

2.1 报文接收模块

频率源和外部控制模块之间采用LVDS进行时钟信号、触发信号的传输。本设计采用Xilinx公司提供的原语将差分信号转换成单端信号,实现输入信号的缓冲。使用IBFGDS将差分时钟信号GCLK_P,GCLK_N转换成单端信号,再用BUFG实现时钟信号的全局缓冲,使它的时钟延迟和抖动最小;使用IBFDS将差分触发信号TRI转换成单端信号。

整个频率源系统主时钟的频率为120 MHz,为了确保系统的稳定性,需要对全局时钟进行约束,在ISE的UCF文件中添加时序约束语句:TIMESPEC TS_CLK_P=PERIOD “CLK_P” 120 MHz HIGH 50%。

SPI模块用于向外部发送频率源状态信息,并接收单端SPI报文信号。本设计采用右移操作实现SPI数据的接收:首先定义一个256位的寄存器Rx_Data_Reg[255∶0],当片选信号CS为低时,开始接收数据,时钟信号SCK的下降沿每来1次,将数据{MOSI,rxd_data_reg[255∶1]}整体右移1次,当CS为高时,将Rx_Data_Reg赋值给Rx_Data,更新一次接收到的报文数据,并将Rxd_Flag置高。

2.2 报文解析模块

报文解析模块将报文信息解析,得到报文头、频率源的频点信息Fre、工作模式信息Mode和校验以及报文尾,和校验为所有字节相加并加1,如果和校验正确,则将报文信息发送给下级AD9914模块。

2.3 波形发生模块

波形发生模块是整个软件设计的核心部分,它包括波形参数模块、相位参数模块、AD9914模块和数据匹配模块。其中,波形参数模块使用了FPGA内部的查找表,它寄存了不同工作模式下DDS的各种调制参数,包括调频时间tFM、调频带宽BFM、数字斜坡下限值NDLIM、数字斜坡上限值NULIM、数字斜坡频率步进sSTEP和时间步进sTIME,参数值均根据Mode样式来设置。为了保证线性调频的效果,这里按照最小数字斜坡时间步进调节,即sTIME固定为1,其余数字斜坡参数计算公式如下:

NULIM=(F0+BFM/2)·1 491 308

(2)

NDLIM=(F0-BFM/2)·1 491 308

(3)

(4)

式中:F0为中心频点;fsysclk为AD9914参考时钟频率。

Phase_Rom模块存储了伪随机相位编码,这里使用EXCEL产生512位伪随机相位编码,调用ISE里的Block Memory Generator IP核,将其设置成单端口只读存储器(ROM),并且设置ROM的深度和数据位宽与Coe文件对应,将Coe文件添加至此单端口ROM。

AD9914模块根据输入的频点信息、工作模式、调频带宽、调频时间、重频等信息,配置AD9914的内部寄存器,使其输出对应的波形。

AD9914模块包含了多波形发生器的加载,其中波形样式分为点频、正线性调频、负线性调频、相位编码4类,每类波形均对应1个线性序列机。根据线性序列机的思想,使用1个计数器不断计数,每个计数值都会对应1个时间,该时间符合操作信号的时间刻,并对该信号进行操作,从而完成AD9914内部寄存器的加载,下面将以正线性调频为例,介绍AD9914寄存器的配置流程。

(1) 地址0x0F:使能自动数模转换器(DAC)校准,触发内部校准程序,从而优化DAC内部时序的建立和保持时间,校准失败会影响功能和性能,因此校准时间需要满足一定条件:

(5)

式中:fs为AD9914参考时钟频率。

(2) 地址0x01:对输出幅度调制时,需要置位外部OSK使能和OSK使能。

(3) 地址0x05:并行端口的频率、相位和幅度会通过不同的路径传达给DDS内核,导致不同的传播延迟,因此,本文调制多余1个参数时需要置位匹配延迟使能位,从而均衡并行端口至DDS内核的每个DDS参数。此外,还需置位SYNC_CLK,它是并行端口的数据时钟,同时还作为FPGA的输入时钟。

(4) 地址0x07:使能数字斜坡非驻留高位。在数字斜坡非驻留高位操作期间,DRCTL引脚正向转换时,会启动正斜率斜坡,频率到达上限值时,DRG会自动掉到下限值。

(5) 地址0x11:设置数字斜坡下限值低16位。

(6) 地址0x13:设置数字斜坡下限值高16位。

(7) 地址0x15:设置数字斜坡上限值低16位。

(8) 地址0x16:设置数字斜坡上限值高16位。

(9) 地址0x19:设置数字斜坡频率步进低16位。

(10) 地址0x1B:设置数字斜坡频率步进高16位。

(11) 地址0x21:设置数字斜坡速率。

其余波形样式寄存器加载方式与此方式类似,这里不做赘述。

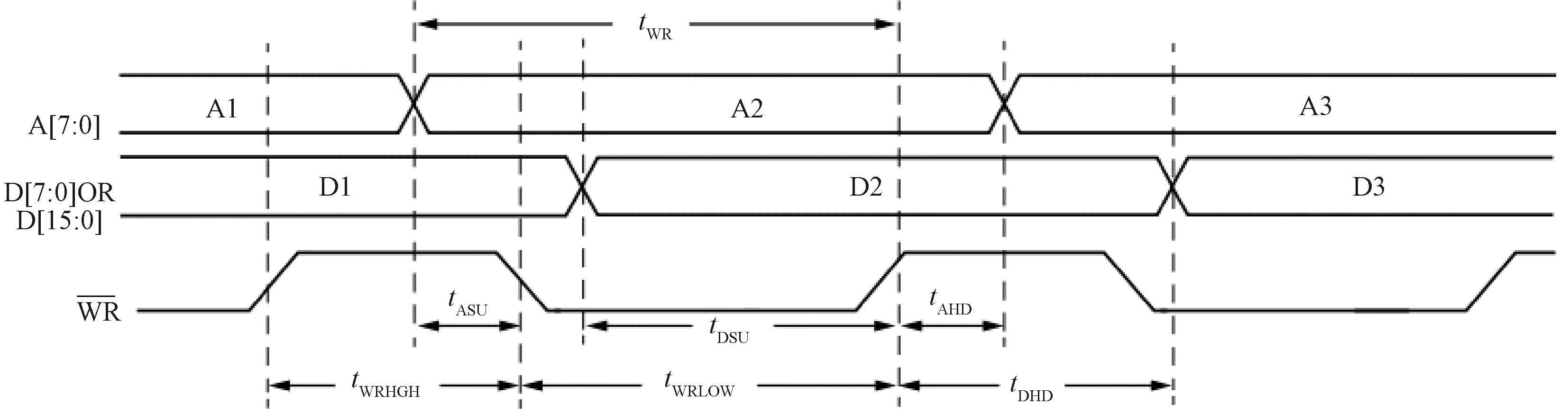

将功能引脚F0~F3配置为全0,通过并行编程实现对AD9914寄存器的加载,写入时序图如图4所示。

图4 并行编程写入时序图

所有的寄存器配置完成后,并行端口数据并不会发送给DDS内核,需要置位IOUPDATE引脚,数据才会发送到DDS内核。当外部控制设备的同步触发脉冲TRI来临之后,将DRCTL引脚由0置为1,保持至少2个周期之后再置为0,并使能幅度控制引脚OSK,AD9914开始输出,当满足调制时间之后,将OSK管脚拉低,AD9914停止输出,1次调制周期结束,系统等待下一个同步触发脉冲的到来。

3 测试结果

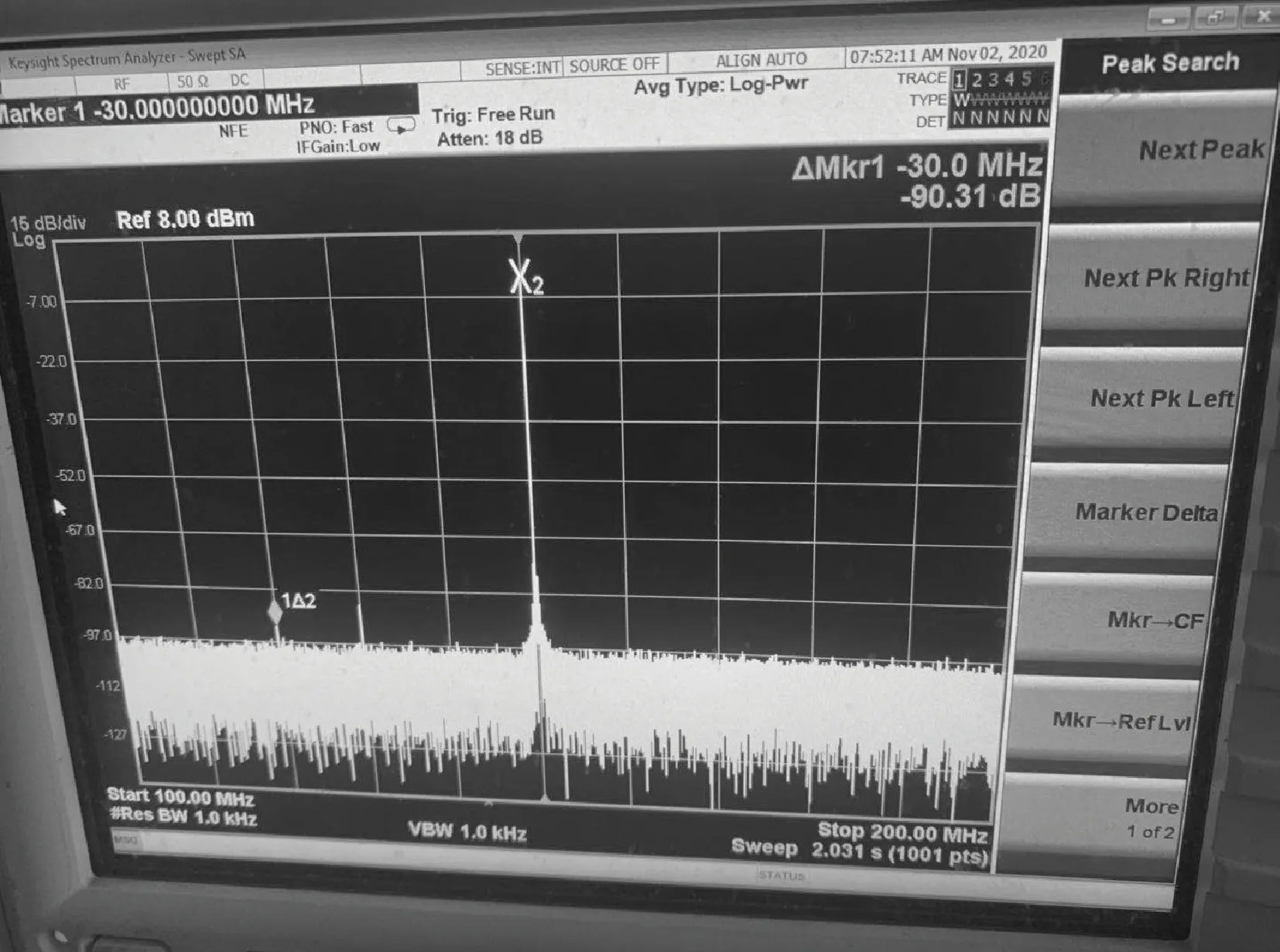

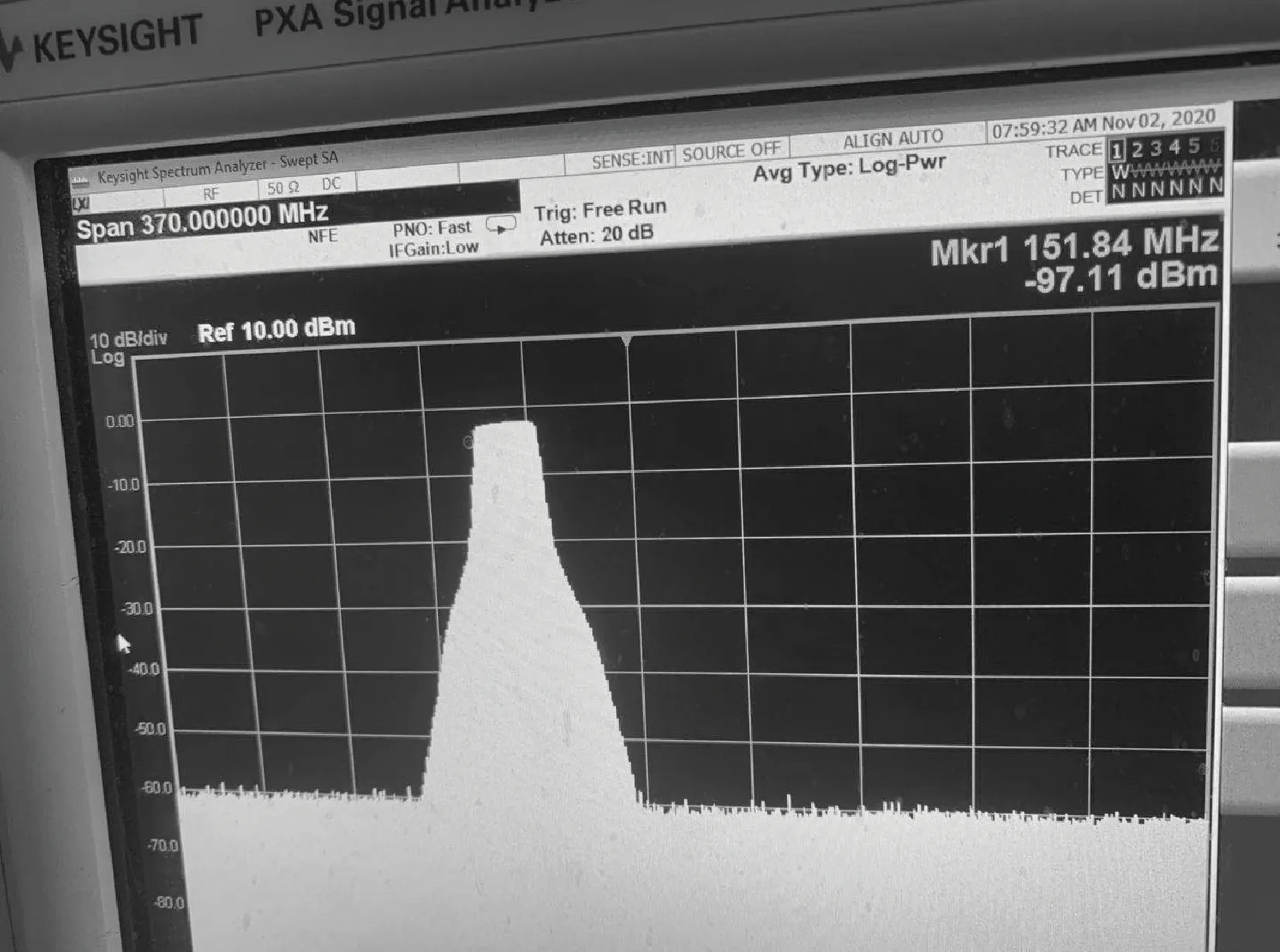

使用频谱仪和示波器对实物进行最终测试,测试过程及结果如图5~图8所示。图5是频率切换时间,切换时间小于250 ns。图6是150 MHz连续波,在100 MHz窄带内杂散抑制达到75 dBc。图7和图8分别是5 MHz带宽和20 MHz带宽的线性调频信号。

图5 频率切换时域图

图6 150 MHz连续波实测图

图7 5 MHz带宽线性调频实测图

图8 20 MHz带宽线性调频实测图

4 结束语

介绍了一种基于DDS的多参数可调频率源,并对其工作原理进行分析,测试结果表明该频率源具有较低的杂散,并且能够实现单频、正负线性调频、脉冲调制等多波形输出。本组件采用DDS技术,集成度高,性能优越,易于装配和调试,具有广阔的应用前景。