基于FPGA的USB3.0通信接口设计

刘林仙,乔楠楠,童 强,王朝阳,马 奎,李 升,杨佳苗

(1. 山西大学 自动化与软件学院,山西 太原 030013;2. 上海交通大学 电子信息与电气工程学院,上海 200240)

0 引 言

随着大数据的兴起和人工智能的发展,高速采集传输系统在数据采集、 数据接收、 数据缓存、 数据传输等方面,都必须满足处理高速数据的条件,尤其对大批量原始数据进行快速稳定的传输提出了更高的要求[1-3].

目前主要使用的高速数据传输方式有USB3.0、 千兆以太网等[4,5]. 千兆以太网理论传输速度为1 Gbps,USB3.0理论传输速度为5 Gbps,因此在涉及大批量数据传输应用时,USB3.0在传输速度上比千兆以太网具有更大优势,而且数据传输稳定性更高[6-8]. 同时,由于FPGA具有数据并行处理能力和高度灵活性,因此在数据采集和高性能数字信号处理领域等方面有广泛应用. 但是由于常用的USB3.0通信接口并不适配于FPGA开发使用,因此开发人员在使用过程中都需要自己设计通信接口,严重降低了开发效率[9-11].

因此本文设计了一款基于FPGA的USB3.0通信IP核接口,最大限度发挥FPGA的并行数据传输速度和USB3.0的高性能传输方式,对未来高速数据传输的发展具有重要意义.

1 系统总体方案

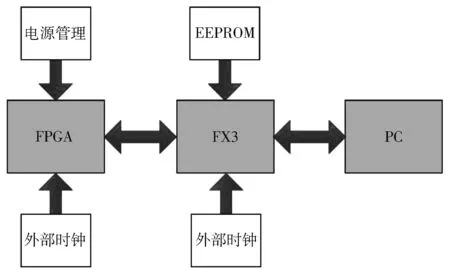

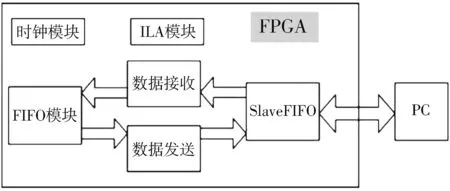

系统总体框图如图1 所示,系统工作流程包括发送控制命令和上传数据,其中FX3和FPGA分别采用独立的外部时钟进行工作. 当发送控制命令时,PC端首先通过上位机软件写入命令,通过FX3芯片将命令发送到FPGA,FPGA通过IP核解析命令并缓存到RAM中; 当系统上传数据时,FPGA读取内部数据,利用USB3.0接口将数据发送到FX3上,最后将数据传输到PC端.

图1 系统总体框图Fig.1 Diagram of system block

系统的USB3.0芯片选取Cypress公司FX3系列的CYUSB3014; FPGA芯片选择为Xilinx公司的XC7A35TFTG256; EEPROM为MICT-MT41K128M16JT-96. 其中CYUSB3014芯片内嵌32 b ARM9系列微处理器,同时可以通过并行可编程接口GPIF II将芯片与任何ASIC和FPGA相连接,芯片向下兼容USB2.0模式,开发人员可以通过编程设置芯片工作模式.

2 USB3.0固件设计

本文采用Cypress官方提供的设计固件Slavefifo_2bit接口验证FPGA接口的IP核. 该固件在加电后,由EEPROM加载到CYUSB3014中,并在其中运行,其作用是控制硬件来完成预期的设备功能. GPIF II接口是USB3.0芯片与外部通信的主要接口部分,理论上可以通过该接口与FPGA实现无缝衔接,进行高速并行数据传输. GPIF II接口的参数均可以在可视化界面进行修改,主要参数为: (1)外设接口,如I2C,I2S,UART等; (2)数据模式: 大端模式(big endian)、 小端模式(little endian); (3)标志位: FLAGX[12,13].

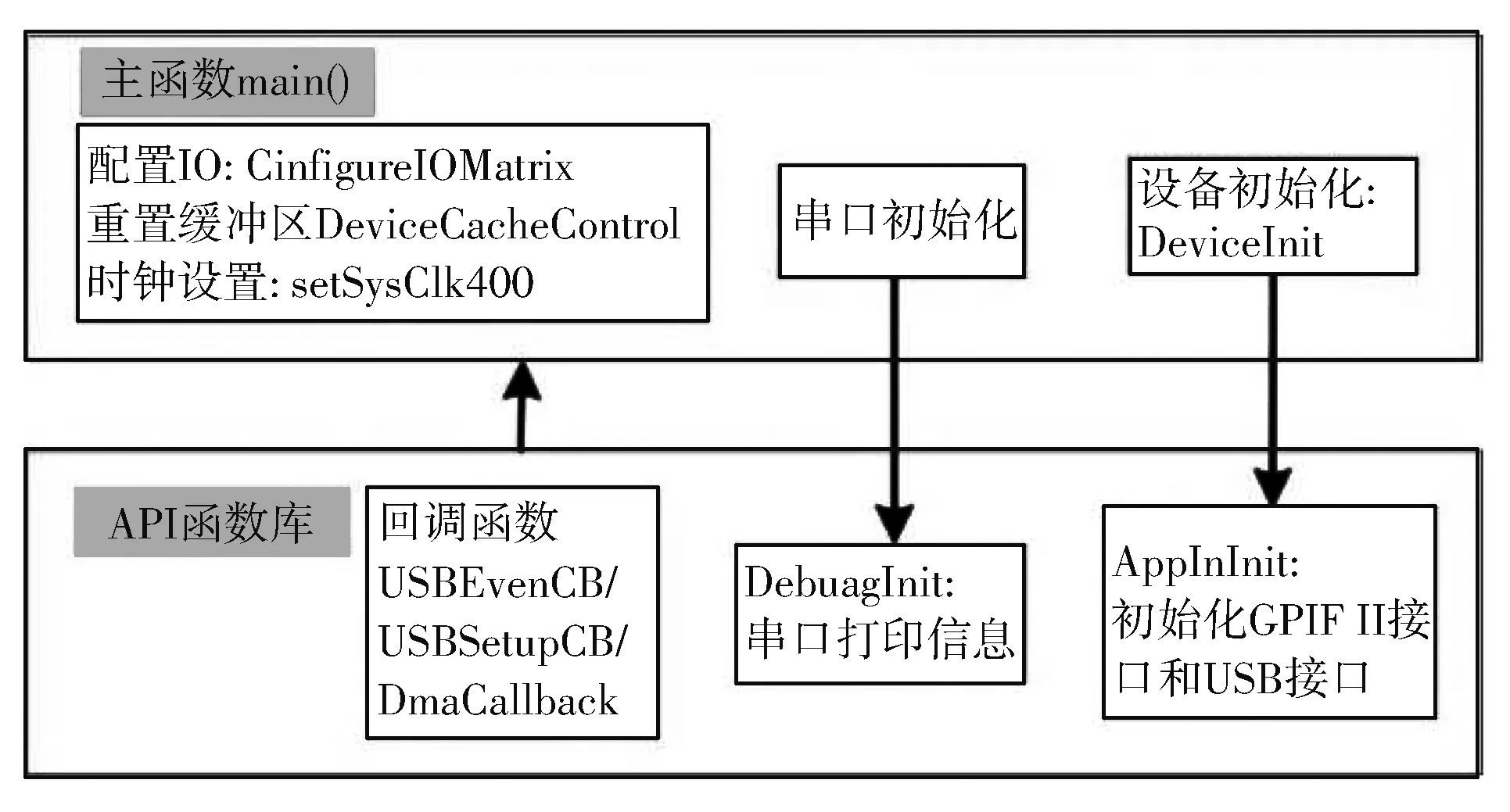

Cyfxslfifosync.c是固件Slavefifo_2bit的主程序,主要包含: IO矩阵配置函数、 初始化应用线程函数、 端点和DMA配置函数、 USB模块的回调函数、 调试信息打印函数. 固件使用流程为: 1)对时钟模块进行配置,令系统时钟工作频率为400 MHz; 2)初始化GPIF接口和USB接口,配置GPIF II接口和固件信息; 3)缓存区进行初始化,选择UART接口打印调试信息[14,15]. 在固件工作过程中通过回调函数进行数据和命令处理,其工作示意图如图2 所示.

图2 固件工作示意图Fig.2 Schematic diagram of firmware work

3 FPGA接口电路设计

FPGA接口既要完成与USB控制器GPIF II的对接,同时也要提供对FPGA内部逻辑模块的数据传输接口. FPGA接口逻辑是本系统的核心,它作为主设备,控制着从设备GPIF的工作状态. FPGA接口逻辑模块内部有一些标志工作状态的寄存器,用户可以通过上位机软件来配置这些寄存器,从而指定整个系统的工作模式. 因此,在执行某种操作之前,需要通过上位机软件先对FPGA接口逻辑模块进行配置.

FPGA接口逻辑除了具有与GPIF Ⅱ相连接的接口外,还提供了其他接口与FPGA内部其他逻辑模块相连接,接口信号如图3 所示.

图3 接口信号示意图Fig.3 Schematic diagram of interface signals

3.1 数据读写状态机

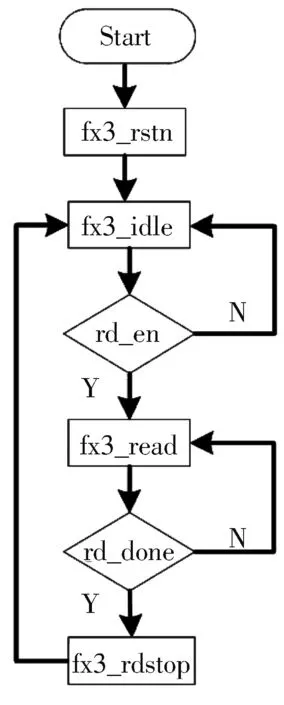

fx3数据读状态机的状态迁移如图4 所示,上电状态为fx3_rstn,随后就进入fx3_idle状态,首先等待fx3的SlaveFIFO有可读数据,然后进入fx3_read状态读取数据,接着进入fx3_rdstop状态停留一个时钟周期,最后回到fx3_idle状态.

图4 fx3数据读出状态机Fig.4 State machine of fx3 data read

fx3数据写入状态机的状态迁移如图5 所示,上电状态为fx3_rstn,随后就进入fx3_idle状态,此时判断SlaveFIFO是否可写入,若可以写入则进入fx3_write状态,写入刚刚读取的所有数据到fx3的SlaveFIFO中,接着进入fx3_wrstop状态停留一个时钟周期,最后回到fx3_idle状态,如此反复.

图5 fx3数据写入状态机Fig.5 State machine of fx3 data write

3.2 FIFO模块和时钟模块

在FPGA程序设计中,除了最主要的USB3.0读写状态,还包含在线逻辑分析仪、 FIFO模块和时钟模块,如图6 所示. 其中ILA在线逻辑分析仪IP核模块主要用于观察数据信号和控制信号,判断信号的时序是否符合要求.

图6 程序主要模块Fig.6 Main modules of the program

在测试回环过程中,FIFO模块主要用于缓存数据写入和读出,不涉及到时钟域和数据位宽的变换. FIFO写入和读出数据位宽均为32 bit,写入和读出数据深度均为1 024,可存储4 KB数据. 时钟模块的输入时钟为FPGA系统时钟 50 MHz,通过锁相环产生4路时钟,频率分别为25 MHz,100 MHz(相位180°),50 MHz,100 MHz(相位0°). 同时对输入时钟模块的复位信号以及时钟模块锁定后的复位信号进行“异步复位,同步释放”的处理,确保系统的复位信号稳定可靠.

4 测 试

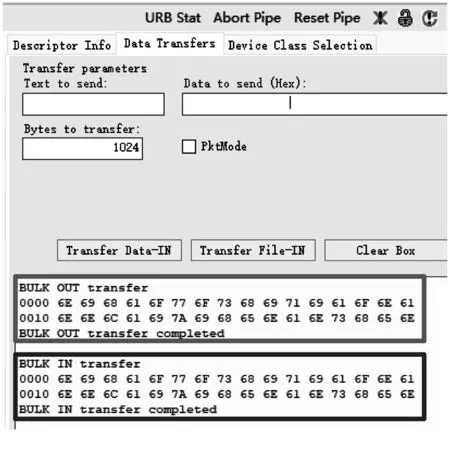

在进行数据传输测试时,首先对USB3.0硬件平台进行连接,USB3.0固件枚举工作正常,设备信息描述符无异常. 数据传输过程中,使用Cypress官方提供的数据测试软件,通过固件枚举,利用端点0x01和0x81实现数据传输,测试结果如图7 所示. 首先上位机软件通过端点0x01向FPGA发送数据流6E 69 68 61/6F 77 6F 73/68 69 71 69/61 6F 6E 61/6E 6E 6C 61/69 7A 69 68/65 6E 61 6E/73 68 65 6E,如图7 上方框选所示,同时在FPGA中利用在线逻辑分析仪观察,在上位机发送到FPGA的数据流波形图中,第一组数据为61 68 69 6E,根据GPIF II的小端模式可以验证下位机接收到的数据和上位机发送的数据一致,表明数据下行传输正确,如图8 所示.

图7 上位机测试结果Fig.7 Test results of upper computer software

图8 上位机发送到FPGA的数据流Fig.8 Data from upper computer to FPGA

如图9 所示,FPGA通过端点0x81向上位机发送数据流6E 69 68 61/ 6F 77 6F 73 /68 69 71 69/ 61 6F 6E 61/6E 6E 6C 61 /69 7A 69 68 /65 6E 61 6E/ 73 68 65 6E,在上位机软件接收到FPGA所发送的数据流如图7 下方框选所示,表明数据上行传输正确.

图9 FPGA发送到上位机的数据流Fig.9 Data from FPGA to upper computer

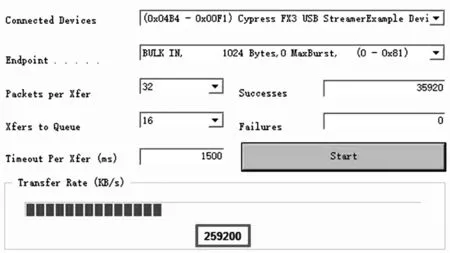

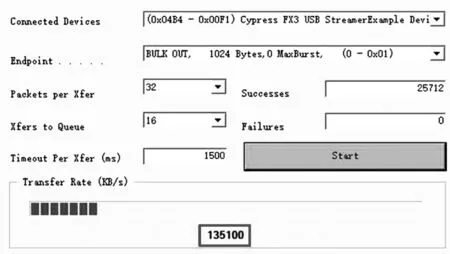

本文使用Cypress公司官方提供的速度测试软件streamer对IP核的传输速度进行测试. 测试结果表明该接口上行通信速率可达到259 200 KB/s,约为253.1 MB/s,如图10 所示. 下行通信速率可达到135 100 KB/s,约为131.9 MB/s,如图11 所示.

图10 上行通信速率测试结果Fig.10 Communication rate test results of upstream

图11 下行通信速率测试结果Fig.11 Communication rate test results of downstream

5 结 论

本文利用Cypress公司FX3系列的CYUSB3014控制芯片,设计适用于FPGA的USB3.0通信IP核接口,并通过实验验证了所设计IP核接口的稳定性和正确性. 通过该IP核接口可以实现FPGA和上位机软件的数据传输,经过测试,该接口实际可达到的上行最大通信速率253.1 MB/s,下行最大通信速率 131.9 MB/s.