基于改进模板匹配及像素相加法的芯片极性二级检测方法

陈 健,王 猛,朱 寒,谢龙华,林 丽

(福建工程学院电子电气与物理学院,福建福州 350118)

0 引言

印刷电路板(printed circuit board,PCB)上芯片的焊接缺陷检测是PCB板缺陷检测的关键环节,也是确保PCB板质量的重要步骤[1-2]。

PCB板缺陷检测中与芯片相关的缺陷包括漏焊和极性焊接错误。早期的缺陷检测多由人工完成,但人工检测存在成本高及易于因疲劳引起漏检等问题[3-7]。随着机器视觉技术的成熟,基于机器视觉的检测系统在工业生产中得到广泛的应用[8-12],包括应用于PCB缺陷检测的机器视觉系统[13-16],学者们也针对缺陷检测系统中的不同问题提出了不同的方法,吴晖辉等[17]针对PCB板上集成电路(integrated circuit,IC)类贴装器件检测的实时性要求提出了基于边缘积分投影和颜色统计的特征检测算法;赵翔宇等[18]提出基于数学形态学结合种子填充的分层提取匹配算法,实现对贴片电阻、电容及IC芯片丢失等多种缺陷的查找;程良伦等[19]提出二值投影分析方法,同样实现对贴片电阻、电容及IC芯片的缺陷检测;陈寿宏等[13]为了提高PCB板中元件焊点缺陷检测的分类准确率,提出一种基于多特征的支持向量机(SVM)多分类缺陷检测方法;曹亮[20]提出一种快速的改进Hough变换圆形检测的方法,检测PCB板中芯片的圆形凹点极性标志,以判断芯片极性是否错误;陈文帅等[21]利用深度学习算法检测电子元器件的极性缺陷。

本文针对PCB板芯片缺陷检测中的极性检测问题,提出一种结合先验知识的感兴趣区域提取、改进模板匹配及像素相加法的芯片极性二级检测方法。实验结果表明,相比于现有方法,本文方法具有更高的芯片定位及极性检测准确性。

1 PCB板芯片极性检测方法

本文提出的芯片极性检测流程如图1所示。

检测流程共分为3个步骤,首先,采用先验知识(芯片封装信息)对PCB板进行划分,确定感兴趣区域(即芯片所在区域),并将其截取出来,随后提出改进模板匹配方法实现芯片的定位,提取出对应芯片图像;其次,对提取的芯片图像利用直方图匹配和中值滤波实现芯片图像的预处理;最后,在对预处理图像进行二值化处理的基础上,提出基于像素相加法的二级检测方法实现芯片的极性检测。

2 PCB板芯片的定位提取

PCB板芯片的定位提取主要分为2个步骤,具体实现流程如图2所示。

基于封装信息的PCB板芯片感兴趣区域划分即结合PCB板原图结构信息,提取不同芯片对应的感兴趣区域范围,每个芯片对应一个感兴趣区域,进行标识。由于焊接后PCB板中各种器件位置是固定的,偏差很小,尤其是芯片位置,因此,事先针对具体PCB板给出芯片所在区域在整个PCB板中的坐标,并存储于数据库中供后续程序调用。

以不同芯片为中心进行感兴趣区域的划分,有利于降低后续模板匹配时其他区域对当前芯片所在区域的干扰,提高芯片定位的准确率及实时性。

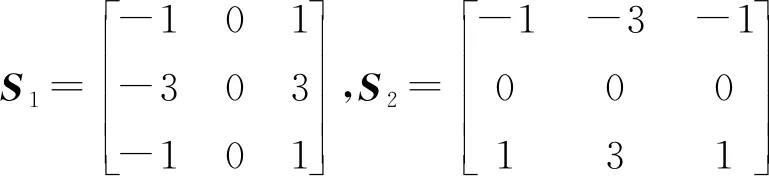

在感兴趣区域划分的基础上,分别以不同的芯片模板按指定的顺序对不同的芯片进行模板匹配。本文提出一种基于多方向Sobel算子的改进模板匹配方法实现待测芯片图像的匹配。多方向改进Sobel算子如式(1)所示。

(1)

式中:S1,S2为水平方向和垂直方向模板;Si(i=3,4,5,6)为对角线方向模板。

多方向Sobel算子的梯度分量信息Hi(x,y)如式(2)所示。

Hi(x,y)=[T*Si]x,y,i=1,2,…,6

(2)

式中:T为图像灰度矩阵;*为卷积运算。

边缘强度M(x,y)计算公式如式(3)所示。

(3)

通常情况下,模板匹配是在计算模板图像和待搜索图像的相似度量的基础上,在待搜索图像中找到模板图像[22]。匹配过程中采用TM_SQDIFF即差值平方和函数作为相似度的测量函数,数学表达式如式(4)所示。

R(x,y)=∑x′y′[T(x′,y′)-I(x+x′,y+y′)]2

(4)

式中:T(x,y)为模板;I(x,y)为目标图像;R(x,y)为相似度量函数,R(x,y)数值越小则匹配度就越好[23-24]。

需要说明的是,考虑到芯片管脚在后续二值化处理过程中存在明显干扰,芯片模板图像去除了管脚部分的信息。

3 基于像素相加法的芯片极性二级检测

提取出待检测芯片后,为提高后续处理的准确性,需要对芯片图像进行预处理。本文分别引入直方图匹配及中值滤波法,实现芯片图像的预处理。

随后,对预处理后的芯片图像进行二值化操作,并对输出图像进行像素相加;最后进行二级检测。检测流程如图3所示。

像素相加即对2幅二值化图像中的像素对位相加,从而得到2幅图像累加信息。设模板图像为bf,待测图像为bh,得到bf和bh像素相加之后的和图像bsum,如式(5)所示:

bsum(x,y)=bf(x,y)+bh(x,y)

(5)

针对电路板的芯片极性缺陷检测,本文提出了二级检测实现步骤,其中步骤1到步骤3为初级检测过程(检测过程如图4所示),步骤4到步骤5为二级检测过程。

步骤1:对预处理后的待测芯片图像和模板芯片图像分别进行图像灰度化,并利用大津法进行二值化操作,计算出待测二值化芯片图像中白色(前景)像素点的个数Nh。

步骤2:将待测二值化芯片图像与模板芯片二值化图像进行像素相加,并计算输出和图像的白色(前景)像素点的个数NT。

步骤3:将和图像的白色像素点的个数除以待测芯片二值化图像的白色像素点个数,并进行阈值判断。若大于设定阈值T1,则跳到步骤4进行二次判断,否则认为芯片无极性问题。

步骤4:截取模板芯片图像及待测芯片图像中的主要特征区域作为模板图像,并在待测芯片中进行模板匹配与提取,再次按步骤1至步骤3进行判断。需要说明的是,为了保证处理的准确性,截取的图像面积小于芯片图像面积的一半,并再次经过预处理过程。

步骤5:判断返回的数值。若返回的数值大于T2,则认为存在芯片极性问题,否则判断为无极性问题。

在上述处理过程中,在初级检测及二级检测阶段各需要一个阈值,在实验中,综合系统的容错性及大量的实验数据结果,T1取1.2,T2取1.3。

4 实验分析

本文搭建的实验平台如图5所示。整个实验平台包括了小型流水线、光源模块、电机控制模块、以太网交换机、工业摄像头、遮光罩及计算机。工业摄像头所采集的图像数据通过以太网交换机传输到计算机进行处理。遮光罩内部包含了条形光源及工业摄像头。

本实验采用单芯片电路板PCB1和多芯片电路板PCB2 2种电路板进行测试,如图6所示,芯片模板图像分别如图7所示。通过在测试系统上采集多组图像得到最终的测试数据集。

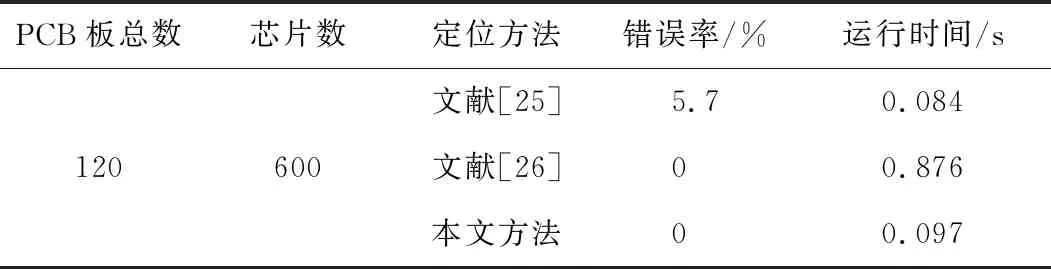

4.1 芯片定位实验对比

针对PCB板中的芯片定位问题,本文引入文献[25-26]中的芯片定位方法与本文的方法进行比较,并采用单芯片和多芯片电路板分别进行实验,比较不同定位方法的运行时间以及准确率,如表1与表2所示。需要说明的是,这里的运行时间是取所有芯片定位时间之和除以芯片总数得到的数值。

表1 单芯片PCB板定位结果对比

表2 多芯片PCB板定位提取结果对比

从运行时间上看,由于文献[26]采用了基于surf算法的芯片匹配检测算法,因此,无论是单芯片电路板还是多芯片电路板,其定位时间均最长。从定位准确性上看,本文方法与文献[26]方法的准确率均能达到100%,而文献[25]的定位方法对多芯片电路板存在错误定位的情况。图8为本文方法准确定位到芯片,而文献[25]的方法出现了错误定位的具体图像。

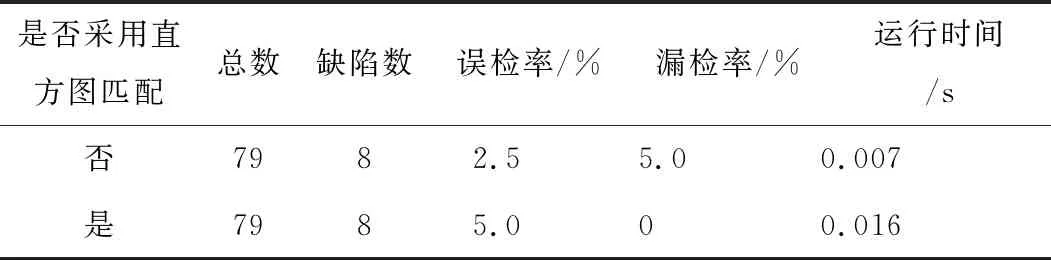

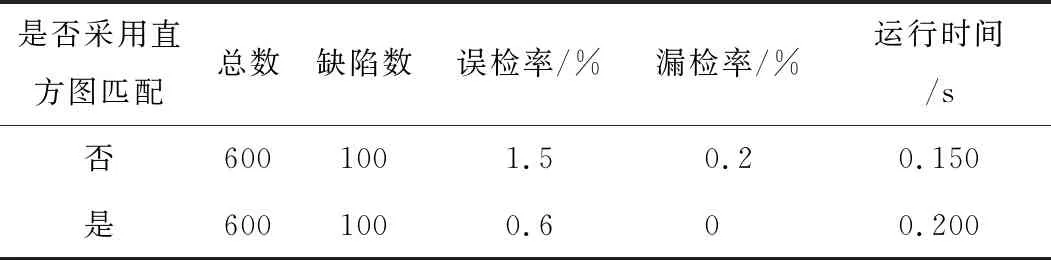

4.2 直方图匹配实验对比

在芯片图像预处理步骤中,本文的方法引入了直方图匹配,在图像的后续处理中起到了很好的效果。实验中,对是否引入直方图匹配进行了对比,并以芯片极性检测的效果即误检概率、漏检概率以及检测时间进行对比,如表3与表4所示。

表3 单芯片PCB板基于直方图匹配的极性检测对比

表4 多芯片PCB板基于直方图匹配的极性检测对比

从表中可以得出,对于单芯片PCB板,对芯片图像采用直方图匹配后,所有极性缺陷芯片都可以检测出来,漏检率为0。对于多芯片PCB板,对芯片图像采用直方图匹配后,漏检率同样为0。而没有采用直方图匹配方法进行预处理的芯片图像,存在1例漏检的情况。另外,不采用直方图匹配进行预处理时,芯片误检率较高。

4.3 芯片极性检测实验对比

针对芯片极性缺陷检测结果,本文在测试平台下采集不同的电路板芯片图像(有极性缺陷和无极性缺陷),进行了对比实验。首先将本文的单级检测方法与二级检测作对比(如表5和表6所示),随后将本文方法与文献[17]作比较,并给出不同方法的运行时间和检测结果(如表7所示)。实验中将全部芯片图像检测的平均时间作为不同方法所需要的最终运行时间。

表5 单芯片PCB板不同级数下本文方法极性检测结果对比

表6 多芯片PCB板不同级数下本文方法极性检测结果对比

表7 不同检测方法的检测效果及时间对比

从表5和表6可以看出,单级检测与二级检测的漏检率均为0,但单级检测的误检率明显高于二级检测。

从表7可以看出,本文检测方法的运行时间较文献[17]的方法长。从检测的效果上看,本文提出的检测方法不存在漏检和误检的问题,而文献[17]存在误检和漏检的情况。

图9和图10给出采用文献[17]方法时误检和漏检的示意图。这里需要说明的是文献[17]中提到的检测方法设置的阈值RA,文献中并未提供,因此在本文中,结合大量实验数据为文献[17]设置了最优阈值,如图中RA值,并将其显示于芯片上以表明具体的误检和漏检的位置。

5 结束语

针对PCB板中芯片极性检测问题,本文提出基于感兴趣区域提取,改进模板匹配及像素相加法的芯片极性检测方法。首先,应用先验知识实现芯片区域(即感兴趣区域)的提取,结合改进模板匹配法实现芯片的精确定位,并提取出待测芯片图像;其次,利用直方图匹配及中值滤波实现对芯片图像的预处理;最后,在对芯片图像进行二值化的基础上,提出基于像素相加法的二级检测方法,实现对芯片极性的检测。实验结果表明,本文提出的芯片定位方法有较好的性能,而针对芯片极性检测的问题,本文提出的检测方法准确性更高。但由于芯片种类繁多,因此,后续可将该方法应用于不同类型芯片的电路板中进行芯片极性的检测。