基于Verilog 的有限状态机编程方式及研究

(西安电子科技大学微电子学院,陕西西安 710126)

0 引言

Verilog HDL[1]是一种常用的硬件描述语言,可以从系统级、电路级、门级到开关级对电路进行设计和验证工作。采用Verilog HDL设计电路并进行仿真实验,具有方便快捷的特点。

有限状态机FSM(Finite State Machine)的基本结构由状态寄存器和组合逻辑电路组成,通过对触发器输入端输入信号,并由状态寄存器对状态完成保持或转换,最后通过组合电路完成特定的输出。分为以下两种情况:

(1)Moore型有限状态机:输出的信号只与当前状态有关。(2)Mealy型有限状态机:输出信号不仅与当前状态有关,而且与输入信号有关。

传统的状态机设计方法需要繁琐的状态分配、绘制状态表、化简次态方程等步骤[2],而使用Verilog语言可以大大简化这一过程。

1 有限状态机的设计流程

有限状态机处于工作状态时,内部的状态寄存器保持现有状态。

根据工作原理,将有限状态机的设计分为以下几个步骤[3]:

(1)确定采用Moore型状态机还是Mealy型状态机。(2)列出状态机的所有状态,并对每一个状态进行状态编码。(3)根据状态转移关系画出状态图。(4)采用硬件描述语言对状态机进行描述。

每一步的选择都会导致编程风格的不一样,更会导致有限状态机性能上各方面的差异。

2 有限状态机的状态编码选择

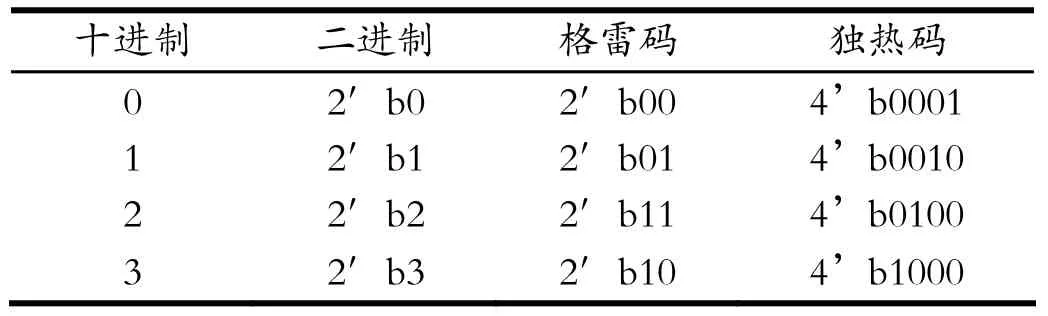

状态编码确定维持状态所需的触发器的数量并影响实现下一个状态和输出时所用的组合逻辑的复杂度[4]。Verilog中常用的状态编码方式有二进制码,格雷(Gray)码和独热(One-hot)码,如表1所示:

表1 Verilog 的常用状态编码方式Tab.1 Verilog's common state encoding methods

通过比较,可以发现二进制编码和格雷码所用的状态向量最短。但对于二进制编码,在状态寄存器进行状态转换时,如果状态从2’b2翻转到2’b3即从2’b01至2’b10这样会产生多个状态的翻转。而格雷码在变化时,实现了仅一位的改变,这样,格雷码在实际应用中减少了电路相邻物理信号线同时变化的情况,从而减少电路中的电噪声[5],若使用独热码,则X 个状态就需要X 个状态寄存器,这将使状态转换过程更加严谨,并且电路的容错性将更好。尽管使用了更多的触发器。但是由于状态解码简单,可以减少组合逻辑[6]。因此,独热码常常在硬件资源丰富的情况下使用。

3 有限状态机的编程方式及其优缺点

通过分析有限状态机的工作方式,可以得到单进程式,双进程式和三进程式三种编程方法。

这几种编程方式的优缺点主要从电路的毛刺、延迟、面积、功耗及速度等方面进行考量。毛刺的产生[7]一方面由于状态机中的组合逻辑对时钟边沿信号的影响,另一方面由于状态向量通过多条电路传输,形成竞争;延迟存在于当前信号改变到下一级电路信号改变时中间经历的时间,延迟的叠加会导致电路的不灵敏;面积和速度不能同时优化,有时为了速度需要牺牲面积。

3.1 单进程式描述方式

单进程式描述方式只有一个always过程块。这种情况下,如果均采用非阻塞语句赋值,电路不会产生毛刺。由于一段式的描述方法是为STATE本身分配一个值,因此会引入一个周期的延时,在设计中需要通过“预计算”将其考虑在内[8]。如果遇到状态较多的情况,编程本身极易出错,且代码冗长,因此,在任何情况下,都不推荐单进程式编程。

3.2 双进程式描述方式

双进程式描述方式有两个always过程块。第一个过程块描述了状态的转移,第二个过程块描述了由输入确定的当前状态以及组合逻辑控制的输出。这种方式使编译器优化效果明显,可以获得非常理想的速度和资源占用率,是目前使用最广泛的状态机描述风格[9]。

3.3 三进程式描述方式

三进程式描述方式有三个always过程块。它由当前状态及输入确定下一级状态,将对输出的选择用单独的一个always过程块描述,从而将组合逻辑电路分离开,使电路不会产生毛刺,可靠性高,并且代码条理清晰,更易维护。

4 实例

用有限状态机实现简易“110”序列检测器,要求避免毛刺、冗余现象,有较快速度。

4.1 状态选择

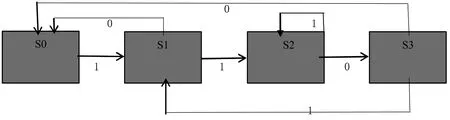

采用Moore型状态机,即输出的信号只与当前状态有关。确定状态转移图如图1 所示:

图1 “110”序列检测器的状态转移图Fig.1 State transition diagram of "110" sequence detector

4.2 编码选择

因为要实现简易状态机,故选择向量长度较短的编码方式,故考虑二进制码和格雷码这两种编码方式。因为格雷码降低了冗余,故选用格雷码进行编码。

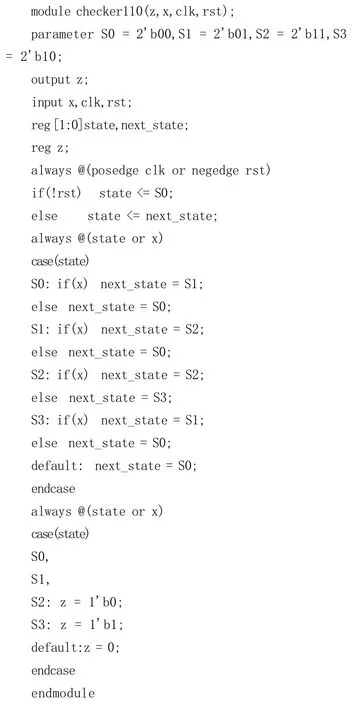

4.3 编程风格选择

由于要求较快速度,则应通过寄存器进行输出,故选用三段式编程方式,这里是牺牲面积,减小延迟,提高速度。

4.4 条件语句选择

选用case语句不需要考虑优先级且编程简洁方便,不会产生锁存器。

4.5 编写程序

4.6 仿真结果

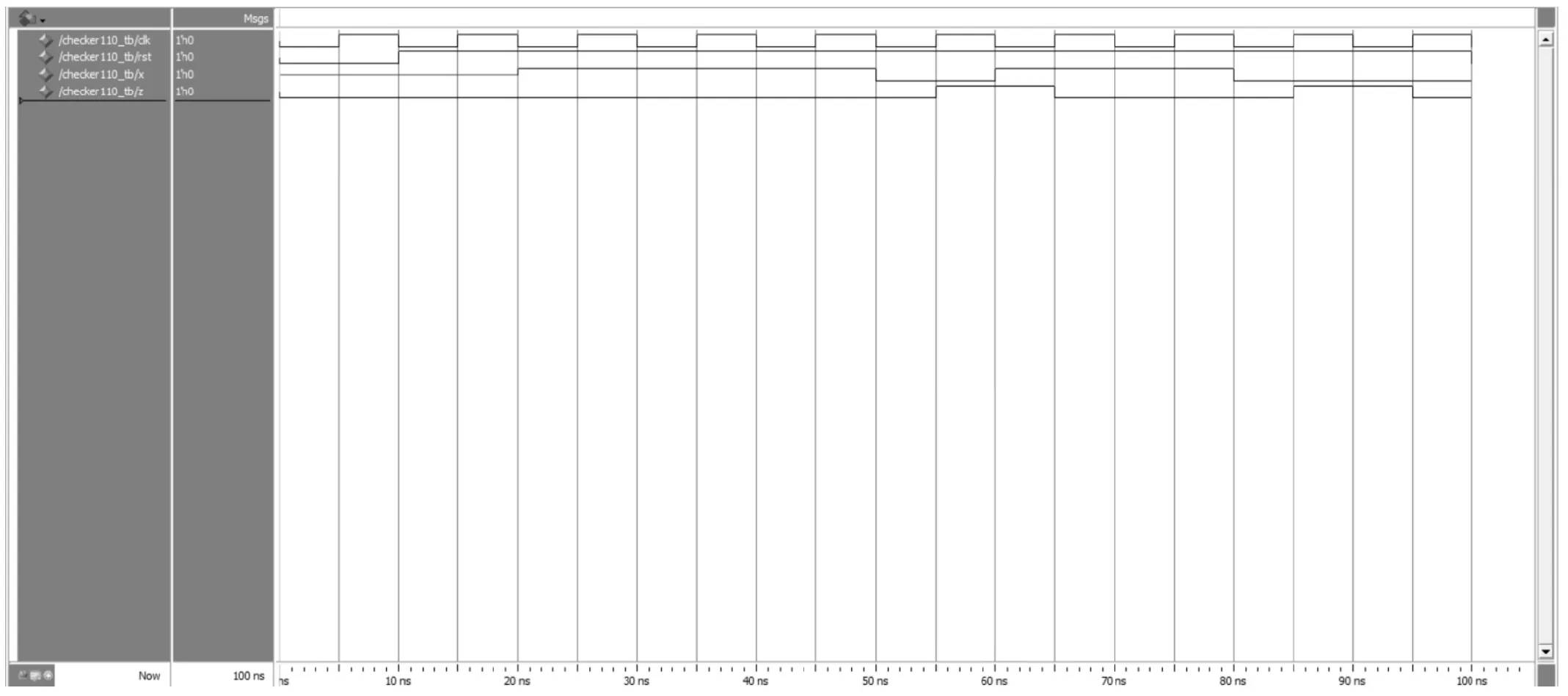

本例通过ModelSim SE 10.6d进行仿真。前10ns对有限状态机实现复位功能,清除上一次运行结果,在第10ns拉高复位信号,启动有限状态机。之后每过10ns对有限状态机输入一个有效信号x,分别为1、1、1、0、1、1、0作为测试序列。通过仿真可以发现,在第一个零(50ns)以及第二个零(80ns)出现之后的时钟沿输出1。运行100ns后,仿真结果如图2所示:

图2 ModelSim 仿真结果Fig.2 ModelSim simulation results

5 结语

有限状态机在集成电路设计中有着重要的作用,选用Verilog 语言进行编程有着方便、简洁等特点。利用Verilog语言编写有限状态机时,编码的选择、编程方式的选取均会影响到有限状态机的性能。对于精确度要求较高的电路可以选用格雷码或者独热码。编程方式尽量选择二进程式或者三进程式。编写条件语句时,要注意清除锁存器。