USB 音频设备中同步时钟系统的设计

来鹏飞李 良徐晟阳邹林均

(无锡中微爱芯电子有限公司,江苏无锡 214072)

通用串行总线(USB)作为一种成熟使用的计算机串行通信接口标准,具有热插拔、即插即用、数据传输可靠、扩展方便的优点,被广泛用于各种嵌入式系统中。

USB 总线是一根4 线电缆,包括2 根差分数据(D+/D-)传输信号线,另外2 根为电源和地线,用于为USB 设备提供电源。USB 总线没有专门的时钟信号用于同步主机和设备之间的数据交互。总线的同步信息包含在数据包的同步字段,通过同步字段可以使主机和设备内的锁相环同步。为了保证通信可靠正确的进行,从机的数据同步时钟频率必须严格跟随主机数据比特信息的时序。

设计了应用于USB 音频外设的同步时钟产生系统,输入参考时钟采用小数分频的方式动态跟随主机传输速率的变化,确保参考时钟的精度,电荷泵锁相环(CPPLL)采用频率倍增的方式产生频率和相位高度跟随参考时钟变化的系统时钟,确保与主机数据传输的可靠性。

1 时钟系统拓扑结构

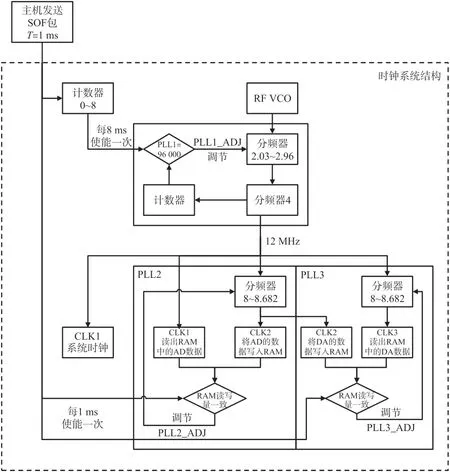

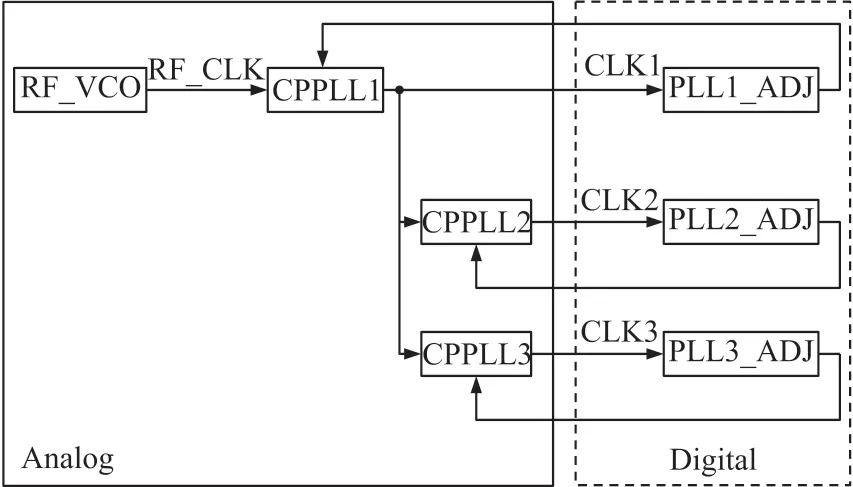

本设计所涉及的USB 音频设备的时钟由内部PLL 频率倍增产生,不需要外接晶振。参考时钟由压控环形振荡器(VCO)时钟进行高精度小数分频产生,小数分频系数根据USB 主机数据包的帧频变化动态调整[1]。PLL1 倍频时钟分频后产生系统时钟,并作为音频AD、DA 模块PLL 的参考时钟,确保音频数据实时传输的可靠性。同步时钟系统的结构如图1 所示。

图1 同步时钟系统拓扑结构

首先主机发送帧起始(SOF)[2-4]包,通过USB总线数据信号传输至音频设备,周期为1 ms。设备对SOF 包解码[5]计数每8 ms 产生一次使能信号,该信号控制PLL1 频率的调整,具体原理如下文。

1.1 PLL1 时钟产生原理

系统上电后,音频设备内的RF 压控振荡器(VCO)首先产生不稳定的高频(640 MHz)时钟信号,该时钟经过小数分频后再800 分频作为PLL1鉴相/鉴频器(PFD)的输入参考时钟。参考时钟在上电默认分频系数下,由于射频时钟的偏差,可能会偏离目标值。此时PLL1 根据参考时钟倍频后分频输出系统时钟CLK1,CLK1 是USB 通信和系统控制的主时钟,PLL1 分频系数调整模块内的计数器以CLK1 进行计数,在SOF 包产生8 ms/次的使能信号时判断计数值是否等于96 000。如果相等,则分频系数不需调整;如果计数值偏大,说明CLK1 频率偏快,需要增大分频系数;如果计数值偏小,说明CLK1频率偏慢,需要减小分频系数。分频系数每8 ms 调整一次,由于PLL 的相位/频率跟随特性,经过若干次调整,PLL1 的频率和相位完成与主机PLL 的同步。

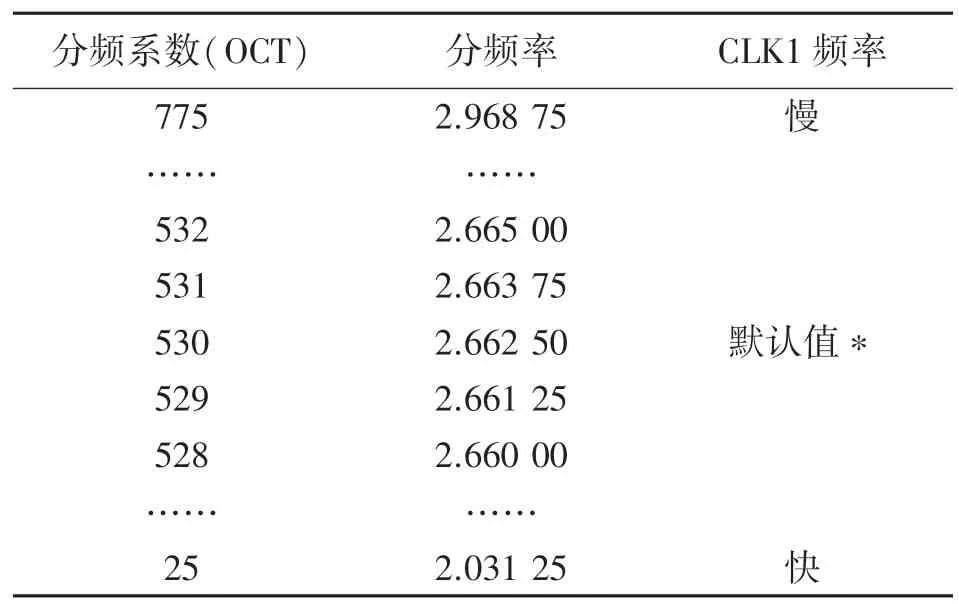

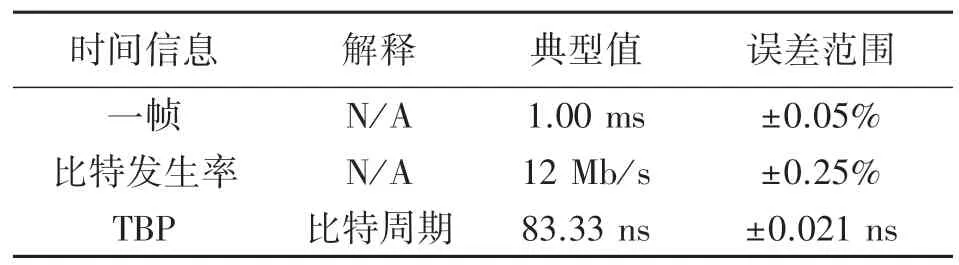

小数分频系数根据CLK1 的频率动态调整,如表1 所示。分频率在2.03~2.97 分频之间调节,共750 级步进,步长0.001 25,确保参考时钟频率为0.3 MHz,误差范围±0.05%,满足USB 全速传输时的时序要求,如表2 所示。

表1 CLK1 频率与小数分频系数的关系

表2 USB 全速传输信号的时序信息[6]

1.2 PLL2/PLL3 时钟产生原理

PLL2/PLL3 分频产生音频设备AD 和DA 模块的工作时钟。为了确保音频数据实时传输时较低的误码率,其数据产生时钟必须与总线比特速率匹配,有必要设计PLL 产生与系统时钟同步的工作时钟。

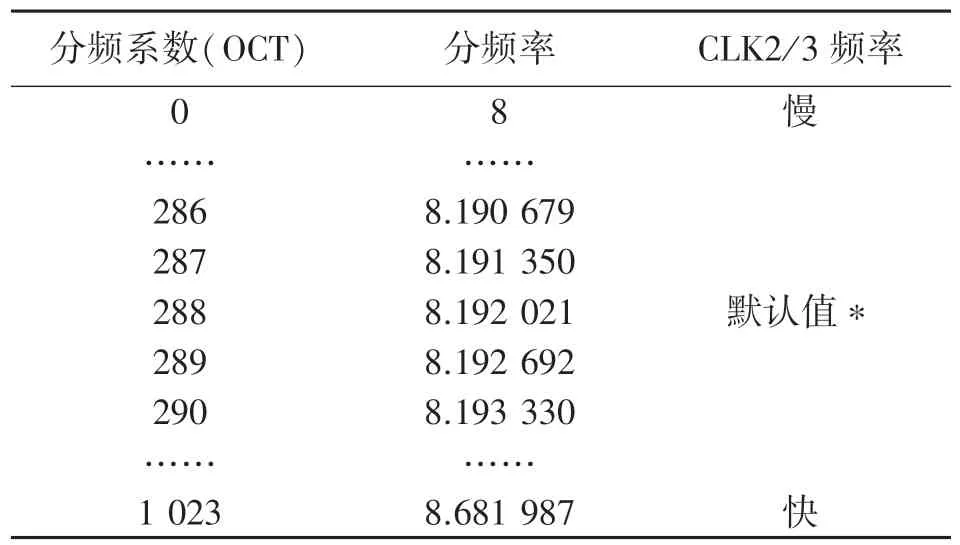

PLL2/PLL3 以CLK1 作为输入参考时钟,根据RAM 数据读写量动态调节所产生的时钟的小数分频系数,小数分频后的时钟送入PFD,确保CLK2/CLK3 的相位/频率跟随CLK1,实现音频数据和总线比特速率的同步。

如图1 所示,设备以CLK1 读取RAM 中的AD数据,并记录读取的字节数,以该字节数为基准,与1 ms 内的写入RAM 字节数作比较,若读写量一致,则认为此时的CLK2 频率不需要调整;若读写量不一致,则控制PLL2 中的分频器做出调整,改变分频系数,使得读写量接近。

同理,设备以CLK2 将主机传输的DA 数据写入RAM 中,并记录写入的字节数,以该字节数为基准,与1 ms 内的读出RAM 字节数作比较,若读写量一致,则认为此时的CLK3 频率不需要调整;若读写量不一致,则控制PLL3 中的分频器做出调整,改变分频系数,使得读写量接近。

表3 CLK2/3 频率与小数分频系数的关系

2 同步时钟系统电路设计

同步时钟系统电路结构如图2 所示。模拟模块包括产生射频时钟RF_CLK 的RF_VCO 电路,产生系统时钟CLK1 的CPPLL1,产生AD 工作时钟CLK2 的CPPLL2 以及DA 工作时钟的CPPLL3。数字模块包括分别产PLL1/2/3 小数分频系数的PLL1/2/3_ADJ 模块。

图2 同步时钟系统电路结构

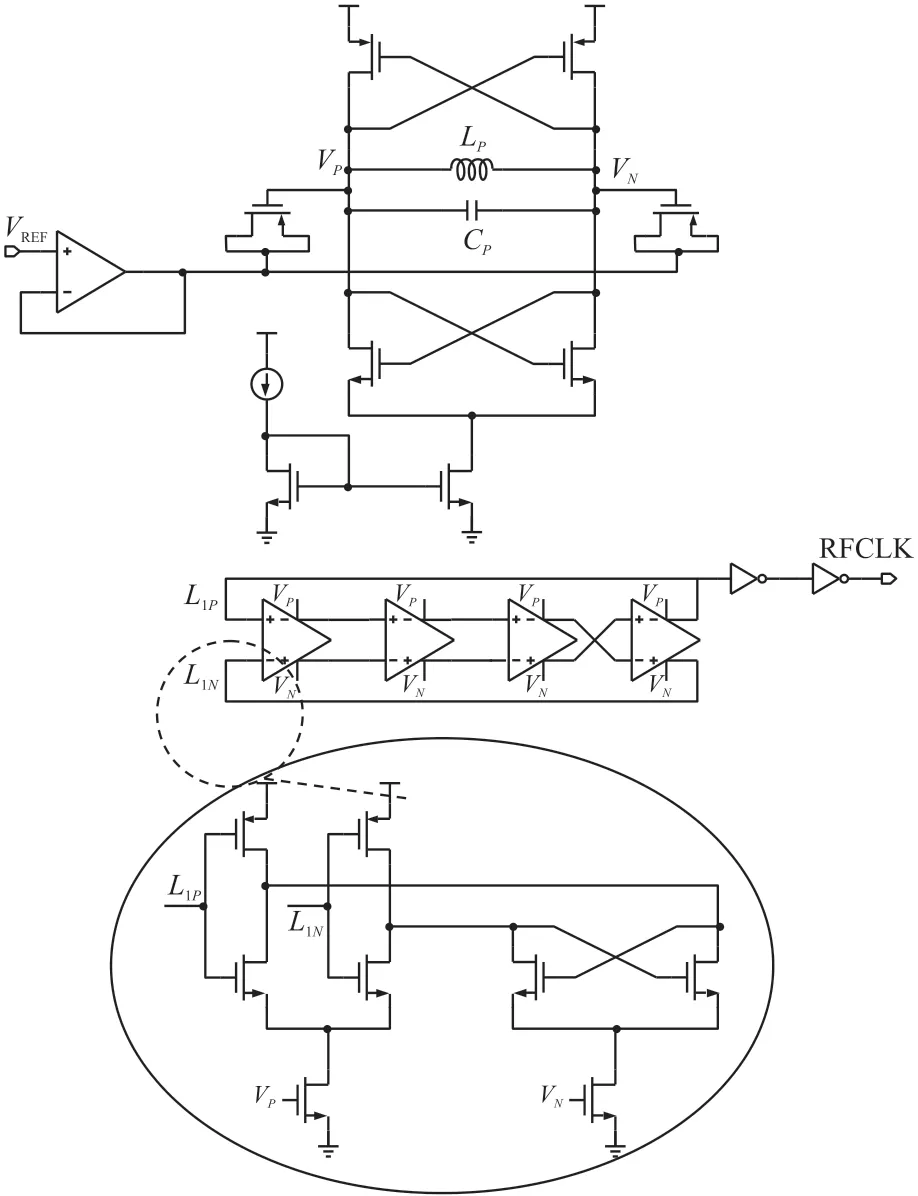

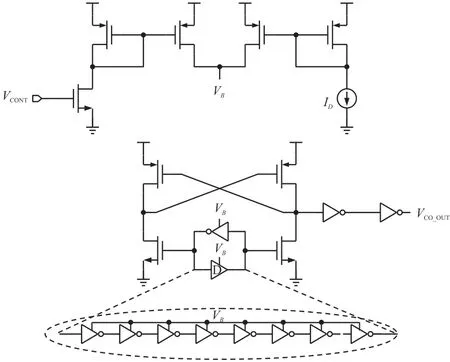

2.1 RF 环形VCO 电路设计

RF 环形VCO 电路结构如图3 所示,M1~M4 采用背靠背交叉正反馈连接构成PMOS 和NMOS 互耦对。互耦对呈“负阻”特性,与LC 振荡回路并联构成负跨导振荡器[7]。采用CMOS 互耦对可以减小电流消耗并降低振荡幅度。通过设置MOS 管宽长比来调整总负阻值,使gmn=gmp=(1.25~1.5)/Rp,确保振荡其可以起振。LC 振荡回路由虚地串联的电容(包括MOS 电容)、电感和并联互耦对并联组成,振荡频率为

MOS 电容一端接VREF控制电压,另一端接X、Y节点,通过改变VREF大小,可以调整MOS 电容容值[8],从而改变振荡频率。

环形振荡采用正反馈技术来调节延迟单元的延迟时间,如图3 所示。LC 振荡器的差分输出信号VX、VY控制延迟单元尾电流。M10 和M11 组成的交互式耦合对产生负阻-2/gm,阻值由偏置电流IN控制,调节负电阻的大小可以改变延迟时间。差分对尾电流IP与IN互补,保证环形振荡具有常数振幅。整个环形振荡器的周期为4TD,TD=1/fLC,所以最终RF 振荡器的频率640 MHz。

图3 RF 环形VCO 电路结构

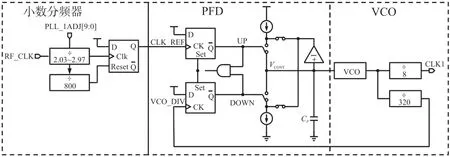

2.2 CPPLL1 电路设计

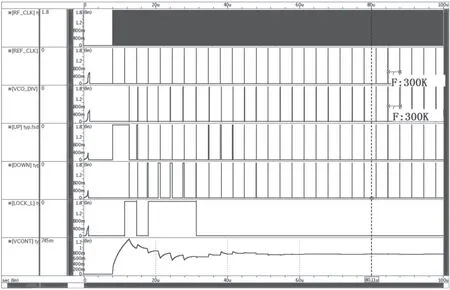

CPPLL1 的电路结构如图4 所示。射频时钟RF_CLK 经小数分频器及整数(800)后作为PFD 的输入参考时钟REF_CLK。VCO 本振时钟分频后(VCO_DIV)与REF_CLK 通过PFD 对比相位及频率,产生电荷泵开关信号UP/DOWN,控制电荷泵对CP充放电,从而改变VCO 控制电压VCONT,使VCO产生与参考时钟频率和相位保持确定的关系的系统时钟CLK1[9]。

图4 PLL1 电路结构

2.2.1 PFD 电路设计

PFD 能检测周期性信号相位差以及频率差,电路结构如图5 所示,由2 个边沿触发、带置位端的D触发器以及具有较大门级延时的与门组成。

图5 PFD 电路结构

输出信号UP 和DOWN 与2 输入信号的相位差和两者的频率差有关,如图5 所示。如果REF_CLK上升沿在VCO_DIV 之前则UP 拉高,电荷泵充电;VCO_DIV 上升沿在REF_CLK 之前则DOWN 拉高,电荷泵放电。

如果器件节点寄生电容较大,当输入信号相位差较小时,则UP/DOW 脉冲信号时间较短,可能无法打开电荷泵开关,导致PFD 存在相位死区,使VCO 的输出在过零点产生“抖动”(jitter)。为了消除死区,在与门产生的置位信号加上一定的延时,延时保证在锁定状态附近(Δφ≈0)时,UP/DOWN 信号宽度足够开启电荷泵开关,从而完成对极小相位差的识别。

当相位锁定后,UP/DOWN 脉冲宽度小于异或门的延时滤波时间,最终LOCK_L 输出低电平,标志时钟稳定,系统可以正常工作;当系统时钟受到干扰,频率/相位不能跟随总线比特率变化时,LOCK_L 产生高电平时钟信号,系统复位。

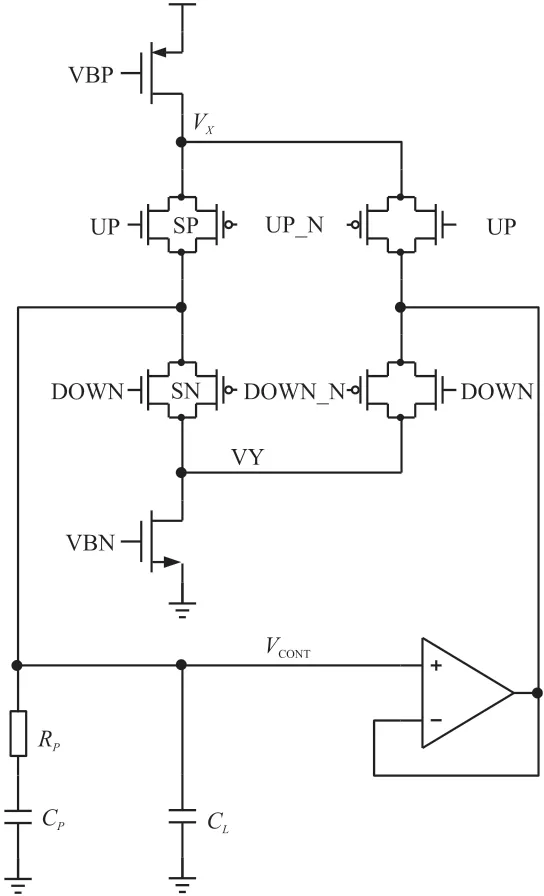

2.2.2 CP 电路设计

CP 电路能够根据PFD 输出信号启动电荷泵控制电容CP的充放电,从而改变VCO 的控制电压VCONT,迫使VCO 输出频率和相位改变,如图6 所示,由CMOS 传输门组成充放电开关,分别有PMOS 电流源及NMOS 电流漏提供CP充放电电流。

图6 CP 电路结构

当UP 信号为高时,说明REF_CLK 频率/相位快于VCO_DIV,开关SP导通,CP上电荷积累,VCONT电压升高,从而使VCO 频率加快,相位提前,当PFD输入信号频率相等,相位差为零时,电荷泵停止充电,环路保持锁定;当DOWN 信号为高时,VCONT电压及VCO 调整过程与以上过程相反。

为了保证反馈系统的稳定性[10],在环路滤波电容中增加了调零电阻RP,同时为了减小VCONT电压的纹波对输出时钟相位的影响,增加了稳压电容CL,抑制VCONT电压的跳动。

由于电流源/漏的漏端寄生电容存在,当相位锁定时如果VCONT电压偏离VDD/2 较大,则在开关SP/SN同时导通时,“电荷共享效应”会导致VCONT电压跳动。为此,在开关断开时,通过电压跟随器将VX/VY电压固定为VCONT,这样开关导通时便不会出现电荷共享效应[11]。

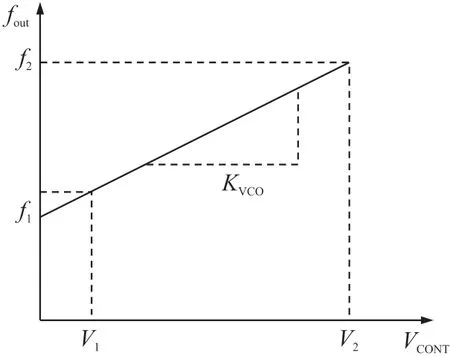

2.2.3 VCO 电路设计

VCO 电路为恒电流源型的环形振荡器,通过改变电流源电流的大小改变振荡频率,如所示,其输出频率是电荷泵输出电压VCONT的函数[12]:

f0为VCONT=0 时的截距,其大小与固定偏置电流ID确定,KVCO表示频率增益或灵敏度(单位为Hz/V)。频率调整范围为f2-f1,如图8 所示。

图7 VCO 电路结构

图8 VCO 频率变化示意图

2.3 CPPLL2/3 电路设计

PLL2/PLL3 电路结构与PLL1 类似,如图9 所示,不同在于其参考时钟为PLL1 产生的CLK1,VCO 产生的分频反馈信号VCO_DIV 的分频系数为小数分频,系数值根据RAM 读写字节量进行动态调整,以使PLL2/3 的VCO 时钟输出与CLK1 匹配,确保音频数据与主机比特速率同步。

图9 PLL2/3 电路结构

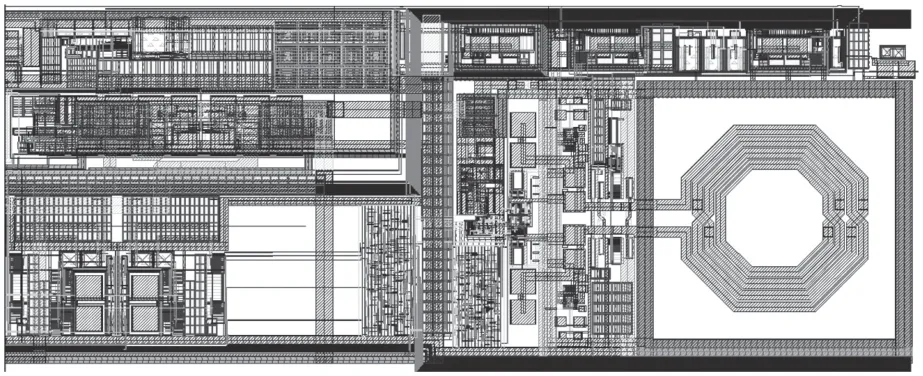

3 版图设计

所设计的同步时钟电路采用0.153 μm CMOS工艺流片,模拟模块版图概貌如所图10 所示。

图10 同步时钟电路模拟模块版图概貌

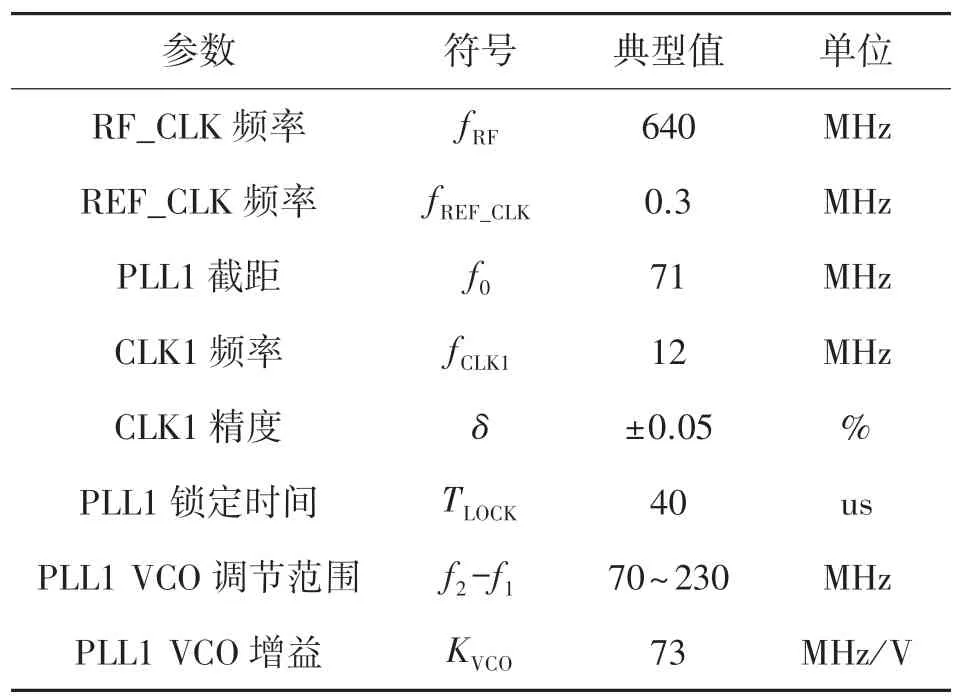

4 仿真结果

同步时钟系统中关键参数的仿真结果如表4所示。

表4 CPPLL 电路中关键参数仿真结果

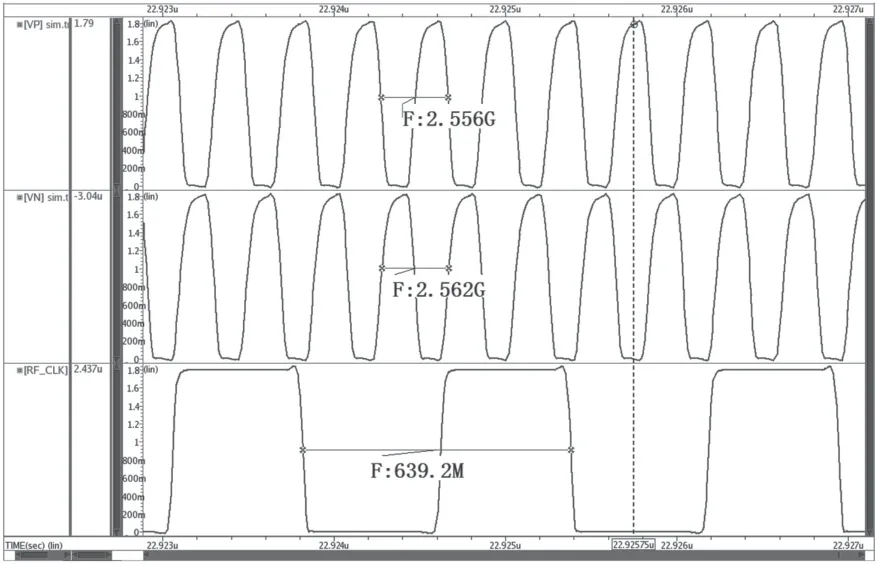

模拟模块中关键信号的仿真波形如图11、图12所示。

图11 CPPLL1 电路仿真波形

图12 CPPLL1 电路仿真波形

5 实测结果

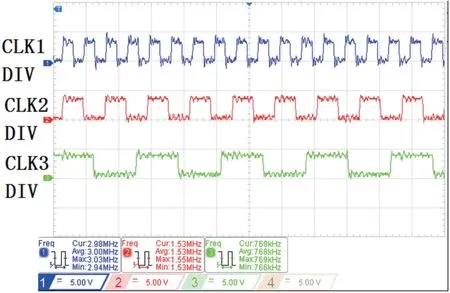

流片测试结果表明USB 音频设备在内部同步时钟的驱动下精确的与主机通信握手,USB 总线差分信号测试结果如图13 所示。

图13 USB 差分信号

PLL1~PLL3 的时钟信号分频后的测试结果如图14 所示,各个PLL 时钟能够精确跟随12 MHz 参考时钟。

当调整参考时钟频率由12 MHz 到13 MHz 时,CLK1 跟随参考时钟频率变化,当两者相位/频率相同时,锁定信号LOCK_L 变为低电平,锁定时间实测为25.8 μs,如图15 所示。

图14 PLL 时钟分频信号

图15 PLL1 锁定信号

6 结论

从USB 音频设备系统的角度,研究了如何确保设备与主机通信可靠地进行,也使设备内部时钟与总线比特数据实现精确的同步。所设计时钟系统以总线数据帧起始包(SOF)作为同步信号,来动态调整CPPLL 参考时钟的小数分频系数,多位调节系数保证了系统时钟的精度,同时为了改善PLL 的相位噪声及抖动问题,分别采取了增加PLL 传输函数零点和消除电荷共享的措施。

仿真及流片实测结果表明,所设计的时钟系统的精度及跟踪范围完全可以满足USB 传输的时序要求,USB 音频设备在内部时钟系统的驱动下,可以与主机可靠地通信。