基于MicroBlaze 的多FPGA 及DSP 远程更新系统设计

赵参,王小龙,郝国锋

(中科芯集成电路有限公司,江苏无锡 214072)

在航空航天、工业控制、雷达等领域,以现场可编程门阵列(FPGA)+数字信号处理器(DSP)设计的设备使用的非常广泛,这些设备通常需要不断地更新完善系统软件[1]。对于大型系统有多个设备和机箱的情况下,通过JTAG 接口连接仿真器的方式进行更新系统软件,不仅耗时耗力,而且有一定的风险,因此不利于设备的维护和管理[2]。

文中设计了基于MicroBlaze 软核的远程更新系统,把多个设备和PC 机通过交换机连接在同一个网络中,上位机设定设备对应的IP 地址,可以对相应的设备程序进行更新,通过更改不同的IP 地址,可以对多个设备进行更新,这样可以完成对整个系统的更新[3]。通过远程更新的方式,使得FPGA 和DSP 更新程序的方式更加便捷,有效提高效率。

1 远程更新系统架构

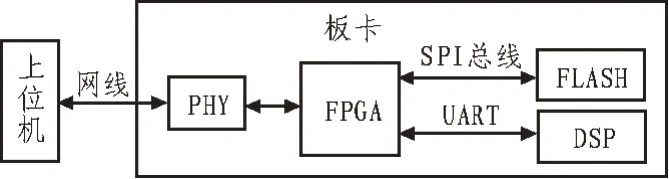

远程更新系统的主要组成如图1 所示,系统主要包括上位机、PHY、FPGA、DSP 和FLASH。上位机通过网络连接到PHY,PHY 芯片连接到FPGA,FPGA通过SPI 接口下发更新应用程序的数据到FLASH,FLASH 用于存储FPGA 的应用程序。另外,FPGA 通过UART 和DSP 进行数据交互,把DSP 的应用程序存储到DSP 片内的FLASH 中[4-5]。

图1 硬件系统结构框图

2 远程更新方法

2.1 FPGA远程更新方法

FPGA 的远程更新功能采用了QuickBoot 的方法,通过快速、健壮的配置方法和高效的基于HDL系统编程设计的互补组合,将编程方法与基于特殊配置头的特殊配置方法集成在一起,实现了可靠的远程更新功能[6-7]。FPGA 的程序加载运行是通过读取FLASH 中的数据进行的,FLASH 包括3 个部分:Header、golden bitstream area 和update bitstream area。Header 包括关键开关字和热启动跳转序列。该系统采用SPI 配置模式,所以关键开关字为0xAA995566。如果关键开关字为打开状态,则执行热启动跳转序列,然后跳转到update bitstream area 区域,读取此区域中的数据配置到FPGA 中运行;如果关键开关字为关闭状态,则继续向下读取数据,这样就把golden bitstream area 中 的 数 据 配 置 到FPGA 中。FPGA 的 远程更新主要是更新golden bitstream area 中的配置文件,步骤如下:

1)擦除关键开关字的块或者扇区,使关键开关字为关闭状态;

2)擦除golden bitstream area 中的配置文件;

3)将要更新的bit 文件写入到golden bitstream area 区域中;

4)验证写入的文件是否正确;

5)验证通过后,将关键开关字打开。

通过Xilinx 提供的TCL 指令和脚本文件,利用要加载的含有远程更新功能的bit 文件生成两个文件:download_initial.mcs和download_update.bin。download_initial.mcs 文件包含上述FLASH 需要的3 个部分,其 中golden bitstream area 和update bitstream area 中的配置文件都含有远程更新的功能。download_update.bin 是上位机下发的要存储到FLASH 中update bitstream area 区域的文件。首先,通过JTAG 烧录download_initial.mcs 文件到FLASH中,设备重新上电后,通过上位机下发download_update.bin 文件,此文件会写入FLASH 的update bitstream area 区域,下次上电后,设备运行的就是更新后的配置文件。如果要更新的文件写入失败,则设备启动的是golden bitstream area 中的文件,此文件也包含有远程更新的功能,这样就保证了可以重新利用上位机下发更新配置文件写入到FLASH 的update bitstream area 区域,完成程序的更新,这样的配置更新方法增加了系统的可靠性。

2.2 DSP远程更新方法

DSP 上电复位后,触发复位中断,中断指向固化在片内ROM 的Bootloader 代码,此代码是出厂就存在的引导程序,不可修改。此代码执行后,读取相关I/O 口的电平,决定Bootloader 模式并初始化相关接口,从该接口读取Bootloader 代码到DSP 的程序空间,读取完成后程序指针跳转到此代码的起始位置并执行,将目的源程序复制到FLASH 中执行,实现真正的代码搬移[8]。上位机发送DSP 远程更新文件后,FPGA 启动配置DSP 的模式管脚电平状态,使得Bootloader 模式为SCIA 模式,然后通过接口下发二级引导程序并执行,将上位机下发的源程序搬移到DSP 内部的FLASH 中。下次重新上电后,DSP 读取到I/O 口的默认电平为全高,从而运行DSP 内部FLASH 中的程序,完成了DSP 的远程更新。

3 远程更新系统设计

3.1 远程更新主要结构

FPGA 和DSP 的远程更新主要是通过FPGA 内部的软核和逻辑设计实现的[9]。其内部主要结构如图2 所示,FPGA 中使用了MicroBlaze 软核,软核中用到了Lwip 协议,此协议在保持了TCP 协议主要功能的基础上减少了对资源的占用。对于FPGA 的更新,上位机通过以太网,将要更新的FPGA 配置文件通过网口下发给FPGA 内部的MicroBlaze 软核,此软核通过Lwip 网络协议解析出有效的数据后,通过AXI 总线把数据传输给FPGA 的fpga_load_ctrl 加载模块,此加载模块会缓存数据并通过SPI 接口把数据存储到FLASH 中。下次上电后,FPGA 从FLASH 中的update bitstream area 区域加载数据,从而完成了远程更新。如果远程更新过程中配置出现错误(比如突然掉电)或者CRC 校验失败,那么FPGA 就从golden bitstream area 区域加载数据,保证了系统的可靠性[10]。对于DSP 的更新,也是通过上位机下发DSP的更新配置文件,软核接收到数据后,通过AXI 总线与axi_uart 模块和dsp_load_ctrl 模块进行数据和指令的交互,把配置文件存储到DSP 的片上FLASH 中。

图2 FPGA内部主要结构

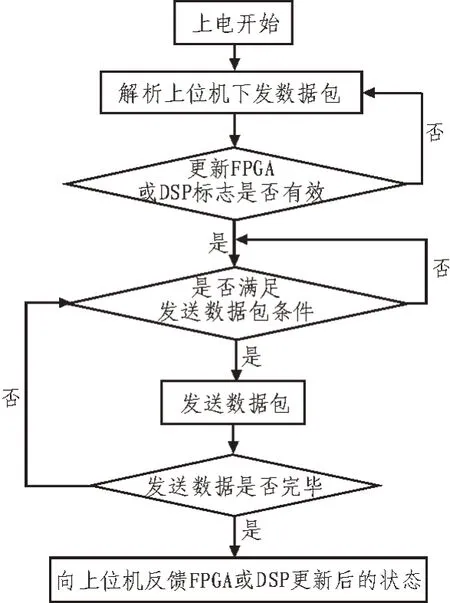

3.2 MicroBlaze软核设计

MicroBlaze 软核的主要流程如图3 所示,上位机通过Lwip 协议解析上位机下发的数据包,提取有效数据判断是否更新FPGA 或DSP,当需要更新FPGA或DSP 时,判断是否满足发送数据包的条件,当满足时继续发送下一包数据,直到所有的配置文件数据都发送完毕为止。最后向上位机反馈FPGA 或DSP更新后的状态,上位机界面显示更新后的状态信息。

图3 MicroBlaze软核主要流程

3.3 FPGA远程更新模块设计

FPGA 远程更新模块主要是fpga_load_ctrl 模块的实现,流程如图4 所示。此模块和MicroBlaze 软核通过AXI 总线进行数据交互,当检测到远程更新启动信号后,就开始对FLASH 进行操作。首先擦除FLASH 关键字,然后擦除FLASH 的update bitstream area 区域,擦除完成后写入更新配置文件,写完毕后,验证写入的数据是否正确,当正确时,打开FLASH 关键字,反之则关闭关键字。操作完成后,反馈给软核此次更新后的状态,软核通过网络传输给上位机显示更新状态[11]。outDone_X4 拉高后,表示为更新成功的状态信息。即使此次更新失败,下次上电启动后,FPGA 检测到FLASH 关键字关闭,也会继续读取FLASH 中的数据,从而加载golden bitstream area 区域中的文件,保证了FPGA 可以正常运行程序。

图4 fpga_load_ctrl模块流程图

3.4 DSP远程更新模块设计

DSP 远程更新模块包括两个部分:dsp_load_ctrl模块和axi_uart 模块。dsp_load_ctrl 模块主要实现二级引导的功能。当更新DSP 的启动标志信号有效后,开始通过波特率为9 600 bit/s 的串口发送二级引导的数据,发送完毕后,给软核反馈数据有效标志,同时把串口收发信号切换到axi_uart 模块,axi_uart模块通过串口接收软核发送过来的配置文件,写入到DSP 的片内FLASH 中[12-13]。

dsp_load_ctrl 模块实现的主要功能是对二级引导数据的发送,具体实现过程如下:

1)发送数据头,共两个字节:0x41,0xAA;

2)发送二级引导数据,共7 079 个字节;

3)延时50 ms;

4)发送5个字节:0xD0、0x2A、0x8D、0xFF、0xFE;

5)DSP 返回9 个字节:0x01、0xE0、0x00、0x00、0xD0、0xF4、0xCA、0xFF、0xFE;

6)发送9 个字节:0x00、0x01、0xC2、0x00、0xD9、0x75、0x7B、0xFF、0xFE;

7)DSP 返回9 个字节:0x00、0x01、0xC2、0x00、0xD9、0x75、0x7B、0xFF、0xFE。

当完成上述过程后,说明二级引导过程成功[14]。然后,把串口收发接口切换给axi_uart 模块,通过软核发送更新DSP 的应用数据给到此模块,波特率为115 200bit/s。

3.5 远程更新上位机软件设计

为了实现FPGA 和DSP 远程更新,用C++语言开发了远程更新工具,其内部集成了网络协议、自定义的收发数据和控制协议,通过和FPGA 内部的软核进行数据交互,把配置文件下发出去。首先,填写IP地址,此IP 地址要和软核中设定的IP 地址保持一致,选择要更新的文件后点击远程更新按键,上位机通过网络开始下发指令和数据给MicroBlaze 软核,最后软核反馈远程更新后的状态给上位机,进而在界面上显示出来[15-20]。图5 和6 分别是FPGA 和DSP远程更新成功后的显示界面。更改IP 地址后,可以远程更新其他设备板卡的FPGA 和DSP,这种实现远程更新的方式不需要任何硬件状态的改变,极大地降低了风险。

图5 FPGA远程更新成功界面

4 结束语

文中设计了通过上位机软件和基于MicroBlaze软核的硬件设备进行通信,对多片FPGA 和DSP 进行远程更新的系统。该设计方案对设备的程序升级和维护带来极大的便利,提高了系统运行可靠性,可以用在许多工程应用领域。

图6 DSP远程更新成功界面