基于FPGA的一种ALU设计与实现方法

向 明 尚

(东北石油大学 计算机与信息技术学院, 黑龙江 大庆 163318)

计算机系统的核心是中央处理器(CPU),目前它的设计技术和产品生产仍被国外企业所垄断。我国的企业和高校也在设计实现CPU,但使用的是国外企业授权的CPU架构和指令集,不具备完全的自主知识产权。为突破贸易和技术壁垒,需要尽快设计实现具有完全自主知识产权的CPU等产品。

算术逻辑单元(ALU)是CPU的核心部件之一,它是一种能够完成多种算术和逻辑运算的单元电路,用来执行CPU指令集中的算术和逻辑操作。因此,ALU的设计直接影响到CPU的性能,进而影响整个计算机系统的工作。现基于FPGA技术和微程序设计思想,提出一种ALU设计实现和仿真验证的方法。

1 ALU功能设计

ALU是一个组合逻辑电路,包括算术单元(AU)和逻辑单元(LU)。它通过数据总线从数据寄存器获得数据,通过控制总线接收CPU发出的算数和逻辑运算指令,把指令分解为微指令对应到具体的微操作,完成相应的运算,然后将计算结果保存到存储器,并放到数据总线上。研究发现,通用微处理器的ALU执行的指令都可以使用加、减、与、或、非等基本运算来完成[1]。为了突出ALU的设计实现方法,在此只给出简单的功能设计。其功能如表1所示。

表1 ALU的功能

2 ALU结构设计

ALU的设计主要有3类结构:复合结构、加法器独立结构和链式结构。我们采用加法器独立结构[2-3]进行设计。加法器和逻辑运算部件分开设计。加法器是运算电路的核心,通常处于ALU的关键路径上。加法器的进位关系包括串行进位和并行进位。串行进位就是进位信号由低位向高位逐级串行传递,进位条件满足式(1)。并行进位就是加法器各级之间的进位信号同时产生,可缩短进位时间,其进位条件满足式(2)。

Ci=f(Ai,Bi,Ci-1)

(1)

Ci=AiBi+(Ai⊕Bi)Ci-1=Gi+PiCi-1

(2)

式中:Ci指第i位向高一位进位产生的进位信号;Ai、Bi指本位的2个操作数据;Ci-1指第i-1位向本位产生的进位信号;Gi指第i位的进位产生信号;Pi指第i位的进位传播信号。

按照串行进位关系,将各级之间的进位信号从低位到高位进行串行连接,构成串行进位链。从最基础的电路原件设计开始,由简到繁逐渐集成,按照自底向上的设计方法设计实现一个8位的串行进位加法器。

2.1 运算单元电路

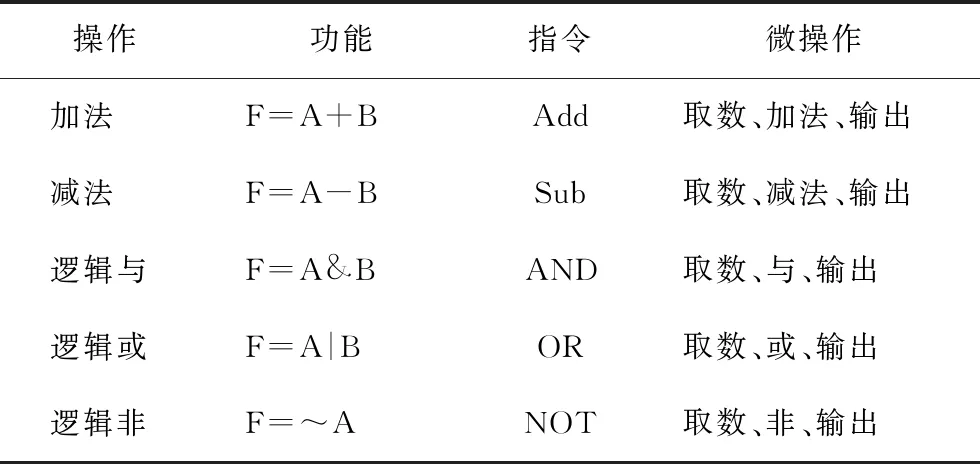

加减运算单元电路是完成2个1位二进制数加减运算的基本电路,它由逻辑与、逻辑或、逻辑异或等基本门电路和输入、输出控制电路组成,如图1所示。

图1 加减单元电路结构及原理示意图

图1中,左右两侧分别为电路的输入和输出引脚。carryin是低位来的进位或借位输入信号,carryin=0时表明低位没有进位或借位,carryin=1时表明低位有进位或借位。a、b是参与加减运算的2个1位二进制数据输入信号。add是做加法和减法运算的控制信号输入端,add=0时做加法运算,add=1时做减法运算。s是 1位的加减运算结果的信号输出端。carryout是本位向高位产生的进位或借位信号输出端,当完成加减运算时,向高位的进位或借位信号由此输出。carryout=0时表明没有进位或借位产生,carryout=1时表明产生了向高位的进位或借位信号。

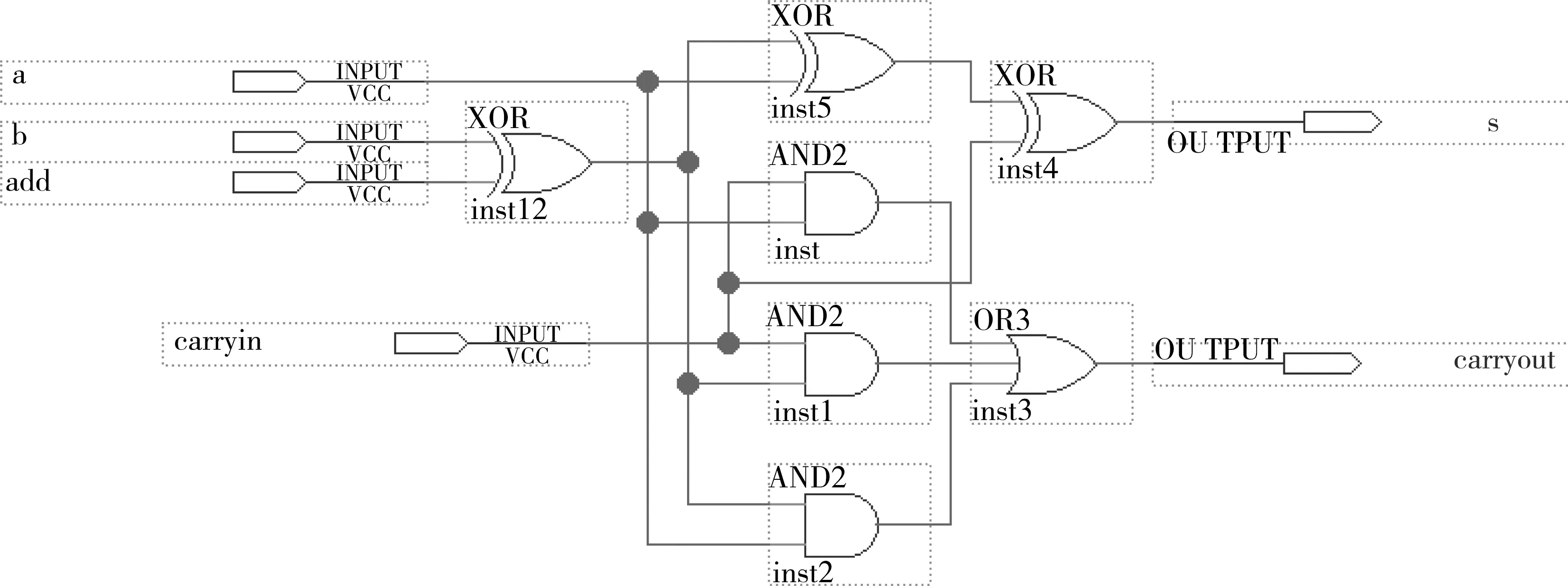

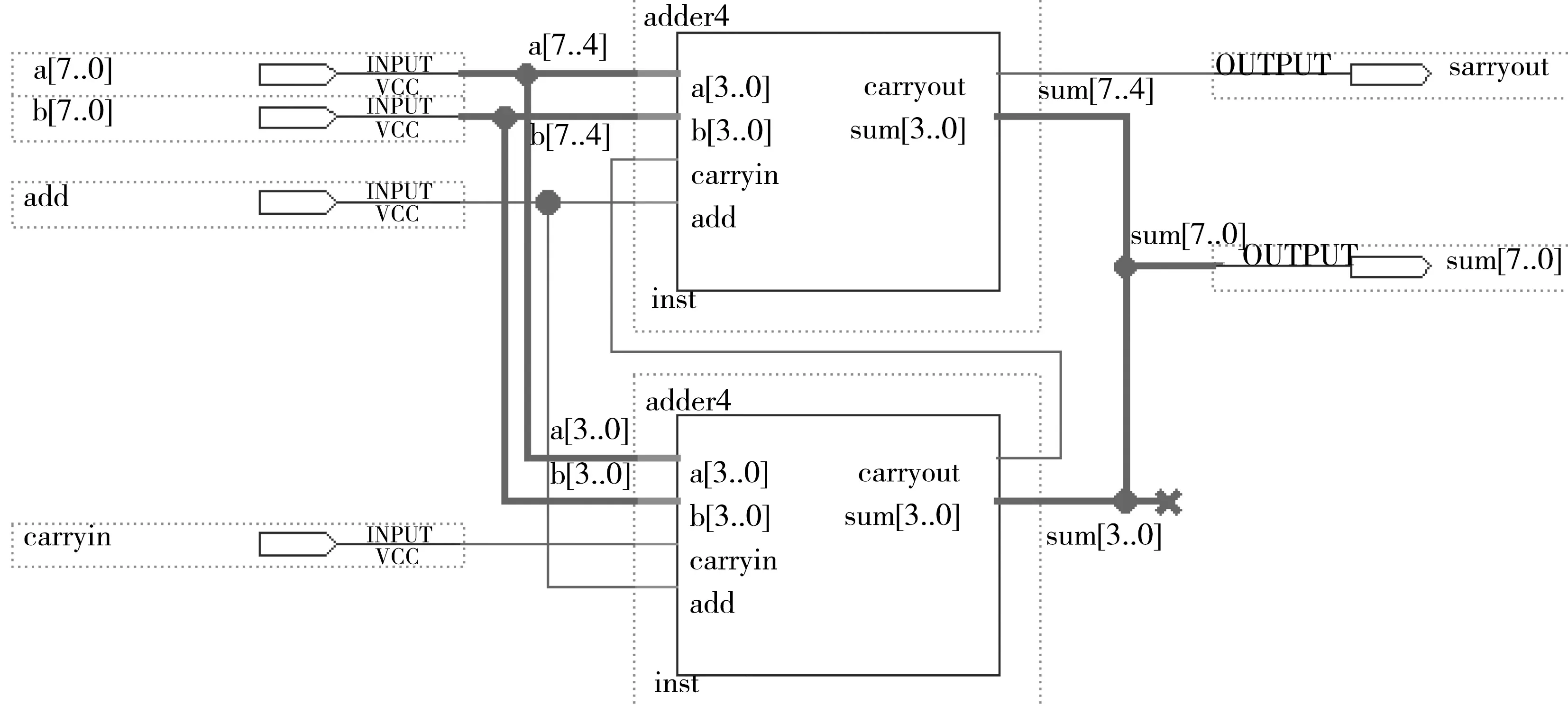

将加减单元电路封装,生成一个加减单元电路器件adderunit,同时连接4个加减单元电路器件,构成四位串行进位加减法器,如图2所示。它可以完成2个4位二进制数的加减法运算。

图2中,a[3..0]和b[3..0]是2个4位二进制数据输入端,分成4部分,分别送往4个adderunit的a、b数据输入端;sum[3..0]是四位加减法器计算结果的信号输出端。

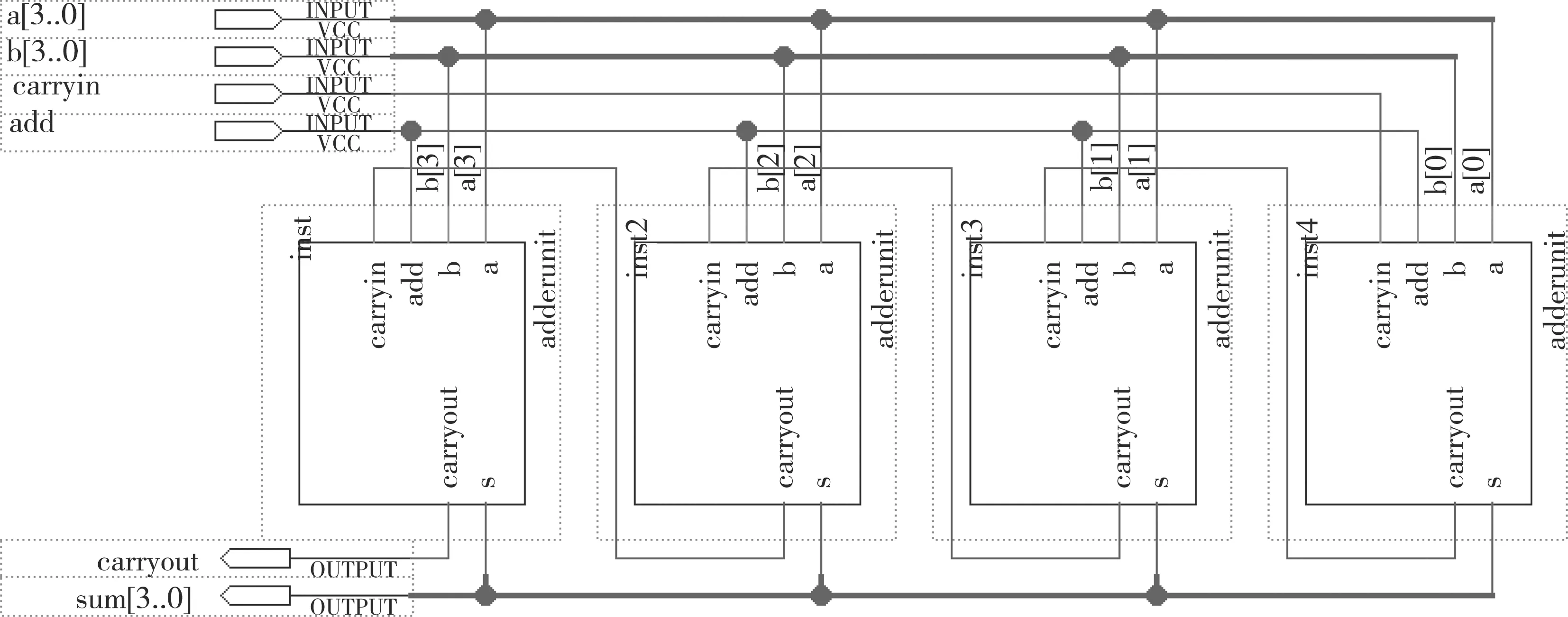

将四位加减法器封装,生成一个四位加减运算单元电路器件adder4;同时连接2个adder4,构成八位加减法器,如图3所示。

图2 四位加减法器电路结构及原理示意图

图3 八位加减法器电路结构及原理示意图

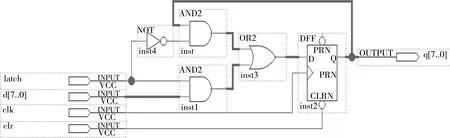

数据寄存器(register)利用D触发器具有存储1位信息的工作特性作为存储原件,输出端和输入端构成一个数据回馈电路(见图4),在脉冲信号的作用下,用来寄存运算过程中产生的结果数据。

图4 数据寄存器电路结构及原理示意图

图4中,latch是数据输入允许锁信号,d[7..0]是8位数据输入信号,q[7..0]是寄存器的数据输出端。latch=1时,高电平有效,图中下面的与门打开,数据d[7..0]进入D触发器保存。latch=0时,低电平有效,图中下面的与门关闭,新的数据无法进来,而此时上面的与门打开,D触发器的输出反馈到输入端,在时钟脉冲信号clk作用下,维持原来的数据不变。clk是时钟控制信号,当clk输入正脉冲信号时,D触发器工作,锁存数据。clr是异步清零信号,不需要时钟控制,可直接用于D触发器清零操作。当clr=0时,低电平有效,D触发器的输出端清零,即Q=0。

2.2 逻辑单元电路

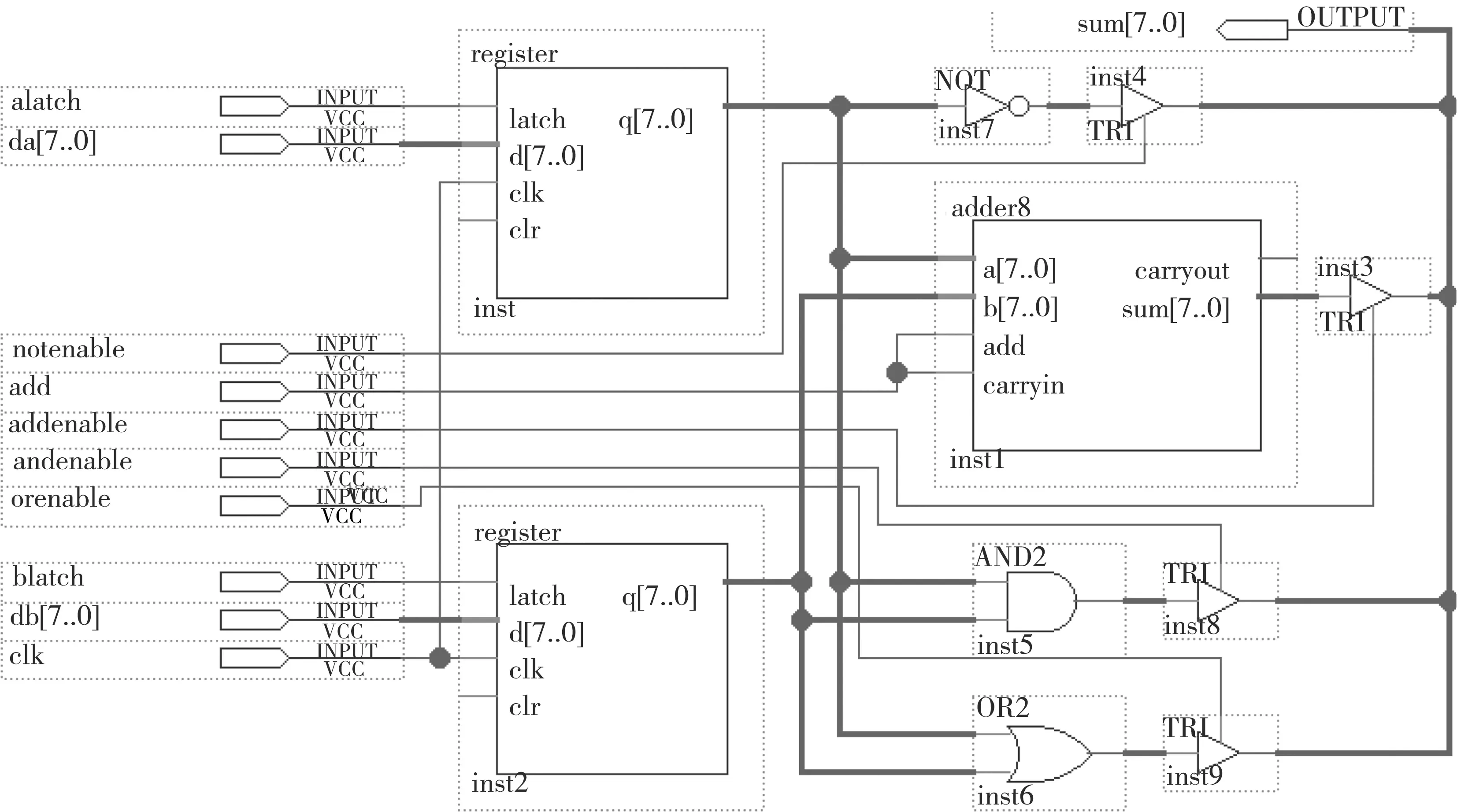

将数据寄存器和八位加减法器分别封装成电路元件,并添加逻辑与、逻辑或、逻辑非、三态门等逻辑门电路,构成一个8位的算术逻辑单元ALU,其电路结构如图5所示。

图5中,register为数据寄存器,用来保存参与运算的2个数据;adder8为加减法器,用来完成2个8位二进制数的加减法运算。4个三态门分时工作,分别将加法的和、减法的差和逻辑运算的结果输出到总线上。da、db是2个参与运算的8位二进制数据输入端。alatch、blatch是数据输入锁存允许信号,高电平有效,分别将数据锁存到2个寄存器,准备参与运算。notenable是逻辑非运算输出允许信号,当notenable=1高电平有效时,输出信号sum=~da,即将输入数据da按位取反后输出,完成逻辑非运算。addenable是加减法运算输出允许信号,当addenable=1高电平有效时,电路输出sum=da±db。add是加减法运算控制信号输入端,同时连接到adder8的carryin和add引脚。当控制信号add=0低电平有效时,做加法运算,即sum=da+db+0;当add=1高电平有效时,做减法运算,即sum=da[7..0]+(db[7..0]⊕11 11 11 11)+00 00 00 01,进而完成da-db的运算。sum[7..0]是8位ALU运算结果的输出信号。

3 控制器设计

设计控制器的目的是为验证ALU的设计在功能和结构上是否正确、是否满足设计要求。控制器可以采用硬布线或微程序控制方式产生控制信号。与硬布线方式相比,微程序控制方式是将操作控制信号以微指令方式编码存放在控制存储器中,在设计及硬件功能扩充维护方面更加灵活方便[4]。

图5 逻辑单元电路结构及原理示意图

利用微程序兼容性好、扩充性强、设计自由度大、易于维护的优点[5],针对ALU的功能要求,将其运算过程分解成多个微操作,并转化为多条微指令,采用Verilog语言,按照微指令的执行过程进行微程序设计。这里给出初始化、加、减、与、或、非运算的部分微程序代码。

initial

begin

addenable=0;andenable=0;

orenable=0;notenable=0;alatch=0;

blatch=0;clk=0;da=0;db=0;add=0;

end

always

begin

#100 add=0;alatch=1;blatch=1;addenable=1;

notenable=0;orenable=0;andenable=0;

#100 alatch=0;blatch=0;addenable=0;

notenable=1;orenable=0;andenable=0;

#100 alatch=0;blatch=0;addenable=0;

notenable=0;orenable=1;andenable=0;

#100 alatch=0;blatch=0;addenable=0;

notenable=0;orenable=0;andenable=1;

#100 add=1;alatch=1;blatch=1;addenable=1;

notenable=0;orenable=0;andenable=0;

end

always

begin

#100 clk=~clk;

end

always

begin

#100 da=da+1;

end

always

begin

#100 db=db+3;

end

4 仿真结果

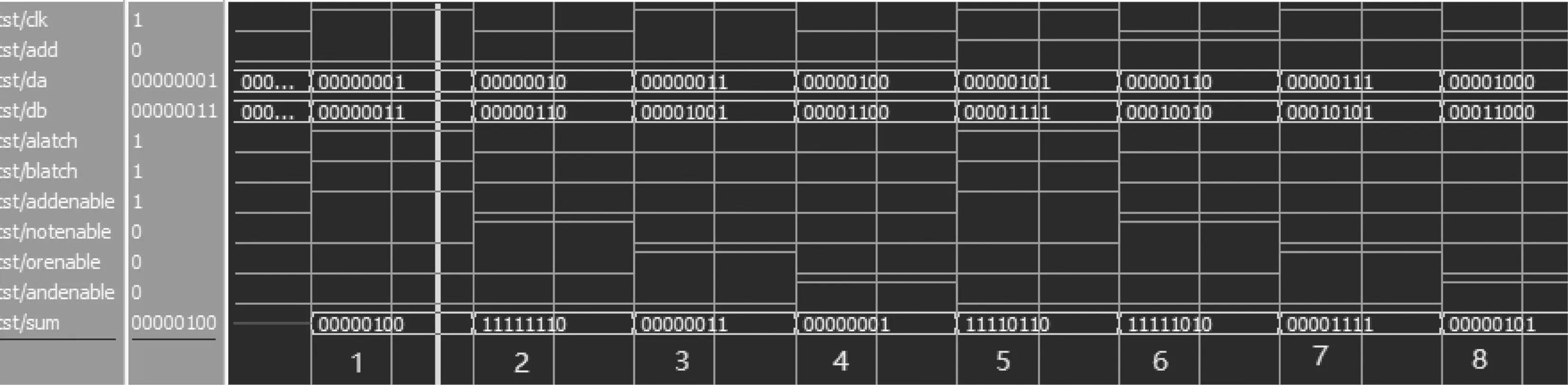

将设计的微程序作为ALU的测试文件,加到项目的工程文件中进行仿真,通过仿真波形验证ALU的功能和设计的正确性。得到的仿真波形如图6所示。

图6 ALU仿真波形图

下面,按图6中标出的数字位置顺序分析结果的正确性。

位置1: alatch=1和blatch=1,2个寄存器的锁存信号同时有效。输入数据da=00 00 00 01和db=00 00 00 11,锁存到2个寄存器中保存,准备参与算术和逻辑运算。此时,add=0,做加法运算,即da+db=00 00 01 00。与此同时,addenable=1,加法输出控制信号有效,对应的三态门打开,ALU输出加法运算的结果 sum=00 00 01 00。

位置2: alatch=0和blatch=0,寄存器锁存信号无效,新的数据无法进入数据寄存器,2个寄存器保存的是原来的数据。此时,notenable=1,逻辑非运算输出允许信号有效,对应的三态门打开,将数据da=00 00 00 01按位取反输出,即 sum=11 11 11 10。

位置3: alatch=0和blatch=0,寄存器锁存信号无效,新的数据无法进入数据寄存器,2个寄存器保存原来的数据。此时,orenable=1,逻辑或运算输出允许有效,对应的三态门打开,将数据da=00 00 00 01和db=00 00 00 11进行按位或运算并输出,即sum=00 00 00 11。

位置4: alatch=0和blatch=0,寄存器锁存信号无效,新的数据无法进入数据寄存器,2个寄存器保存原来的数据。此时,andenable=1,逻辑与运算输出允许有效,对应的三态门打开,将数据da=00 00 00 01和db=00 00 00 11进行按位与运算并输出,即sum=00 00 00 01。

位置5: alatch=1和blatch=1,2个寄存器的锁存信号再次同时有效,新的数据da=00 00 01 01和db=00 00 11 11,即2个十进制数据5、10,保存到2个寄存器中,准备参与算术和逻辑运算。此时,add=1,做减法运算,输出结果sum=11 11 01 10,即完成了2个操作数5、10的减法运算。此时的输出结果sum=11 11 01 10,即为-15的补码表示。与此同时,addenable=1,减法输出控制信号有效,对应的三态门打开,输出减法运算的结果,即总线上输出sum=11 11 01 10。

位置6: alatch=0和blatch=0,寄存器锁存信号无效,新的数据无法进入数据寄存器,2个寄存器保存的是第二次锁存的数据,即da=00 00 01 01和db=00 00 11 11。此时,notenable=1,逻辑非运算输出允许信号有效,对应的三态门打开,将数据da=00 00 01 01按位取反输出,即sum=11 11 10 10。

位置7: alatch=0和blatch=0,寄存器锁存信号无效,新的数据无法进入数据寄存器,2个寄存器保存的是第二次锁存的数据,即da=00 00 01 01和db=00 00 11 11。此时,orenable=1,逻辑或运算输出允许有效,对应的三态门打开,将数据da、db进行按位或运算并输出,即sum=00 00 11 11。

位置8: alatch=0和blatch=0,寄存器锁存信号无效,新的数据无法进入数据寄存器,2个寄存器保存的是第二次锁存的数据,即da=00 00 01 01和db=00 00 11 11。此时,andenable=1,逻辑与运算输出允许有效,对应的三态门打开,将数据da、db进行按位与运算并输出,即sum=00 00 01 01。

通过上述分析过程,结合ALU的设计原理图,按照测试步骤对ALU的加法、减法、逻辑与、逻辑或、逻辑非等功能逐一验证,并结合波形图对应的各阶段的仿真结果进行分析,可以证明算术单元和逻辑单元设计的正确性。

5 结 语

ALU的作用是完成多种复杂的算术和逻辑运算并执行CPU的指令,它对CPU的性能和计算机系统的工作有直接影响。我们尝试设计了一个8位串行ALU,以原理图的形式给出了设计实现的全过程;并通过编写微程序设计了一个控制器,作为ALU的控制部件发出测试命令,对其功能进行测试。测试结果表明,以原理图的形式设计单元电路,以微程序设计测试文件和控制单元,采用自底向上的方法,能够保证ALU在结构和功能上达到设计要求,这是一种简单而有效的实现方法。